.jpg)

제로 드리프트 연산 증폭기는 샘플링을 이용해서 입력 오프셋 전압을 최소화하기 때문에 사실은 에일리어싱에 취약 할 수 있다. 따라서, 설계자는 에일리어싱에 대해 연산 증폭기를 검사를 해야 한다.

글/파하나 사더(Farhana Sarder)

애플리케이션 엔지니어, 온세미컨덕터

제로 드리프트 증폭기 클럭 주파수 파악

제로 드리프트 증폭기 데이터시트 중에는 내부 클럭 주파수 정보가 없는 것이 많다. 때때로, 애플리케이션 섹션 단락에서 언급되기도 한다. 가끔씩은 클럭 주파수가 무엇인지 암시하는 잡음이나 대역폭 플롯의 작은 변화로 파악될 수도 있다. 이 때문에 에일리어싱 민감도에 대한 회로 검사를 하는 것은 사용자 몫이다.

이 글에서 설명하는 검사 방법은 매우 간단하다. 오실로스코프 상의 연산 증폭기 출력을 관찰하면서 이득 대역폭 곱까지 주파수 범위에 걸쳐 증폭기 입력을 스위핑한다. 알려진 제로 드리프트 중폭기는 모두 그 내부 클럭 주파수가, 저자가 아는 바에 따르면, 증폭기의 이득 대역폭 안에 들어오며, 이득 주파수의 약 3분의1 정도에 있는 경우도 많다. 이런 증폭기는 해당 주파수의 절반 미만의 신호 대역폭에서 최고의 성능을 보여줄 것이다.

에일리어싱 발견 및 검사

제로 드리프트 증폭기 데이터시트 중 일부에는 에일리어싱이 없다고 명시되어 있는 것도 있다. 이런 제조업체들은 에일리어싱 측정을 위해 가능한 모든 노력을 해보았지만, 아무것도 발견하지 못했다고 가정할 수 있을 것이다. 온세미컨덕터에서 제로 드리프트 증폭기 개발 과정에서 경쟁 증폭기를 처음 측정했을 때 상태가 깨끗하다는 결과가 나왔다. 그 때, 경쟁사 기기의 출력에서 클럭 아티팩트가 발견되지 않았다. 하지만, 간단한 오실로스코프 기반의 측정 방식을 사용해서 해당 기기에 추가 검사를 한 결과 여전히 에일리어싱이 발견되었다.

에일리어싱은 고객들이 여러 제조업체의 제로 드리프트 연산 증폭기를 사용한 시스템에 대한 문제를 보고하면서 발견되었다. 이런 경우, 관심 신호, 저주파수 또는 dc신호가 높은 진폭, 고주파 간섭 또는 리플(ripple) 신호 겹침을 갖는 공통점이 있었다. 정확한 신호 보고를 할 수 없는 부정확한 조건과 시스템에서 안정화하는 폐쇄 루프 시스템을 포함해서 최종 시스템의 결과는 상이했다.

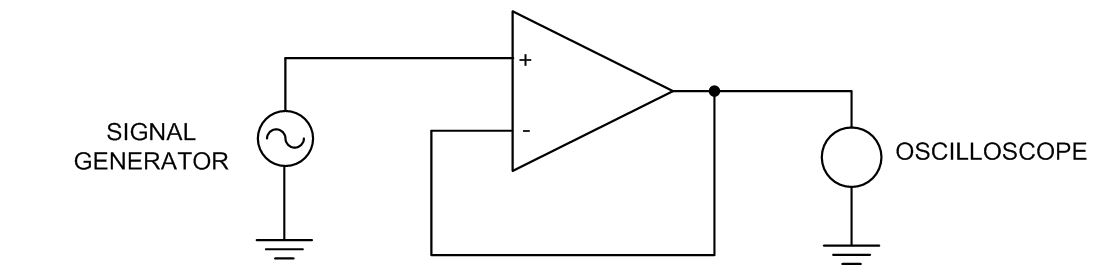

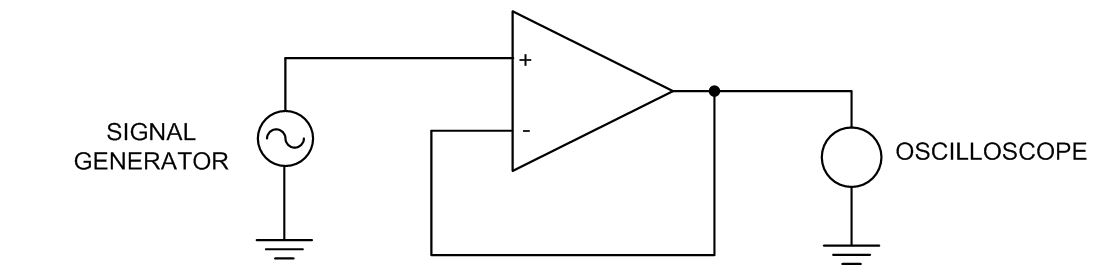

과거에는 에일리어싱을 발견하기 위해 정교한 스펙트럼 및 네트워크 분석 시스템을 사용했으나, 확정적인 결론을 얻을 수는 없었다. 보다 근본적인 방식을 취하기 위해서, 오실로스코프를 증폭기 출력에 연결해서 직접 육안으로 관찰을 했다. 입력 자극을 위해서, “비트(beat) 주파수”가 출력에서 만들어 질 수 있는지 보기 위해서, 클럭 주파수가 있을 것으로 예상되는 곳 주위로(그리고 필요하다면 그 이상으로) 입력 주파수를 스위핑하는데 발생기를 이용했다. 논란의 여지가 있겠지만, 가장 선형적 연산 증폭기 구성 중 하나인, 그림 5에 제시된 +1 구성 이득의 초기 노력을 감안했을 때 이 방법은 놀라울 정도로 성공적이었다.

그림 5. 에일리어싱 탐지를 위한 검사 회로는 단순한 단일 이득 버퍼이다. 이 방법에서는 오실로스코프에서 기기 출력을 관찰하는 것이 필수적이다. 스펙트럼 및 네트워크 분석기로는 제로 드리프트 증폭기의 내부 작동과 관련된 신호가 항상 감지되는 것은 아닌 것 같다.

그림 5. 에일리어싱 탐지를 위한 검사 회로는 단순한 단일 이득 버퍼이다. 이 방법에서는 오실로스코프에서 기기 출력을 관찰하는 것이 필수적이다. 스펙트럼 및 네트워크 분석기로는 제로 드리프트 증폭기의 내부 작동과 관련된 신호가 항상 감지되는 것은 아닌 것 같다.

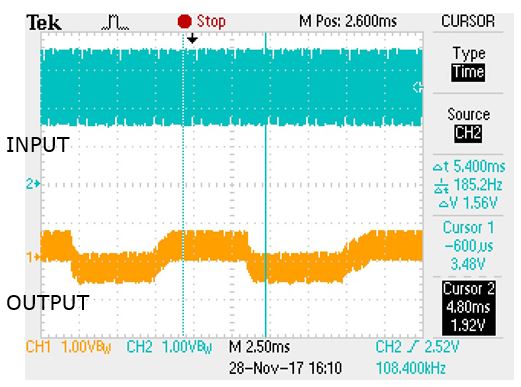

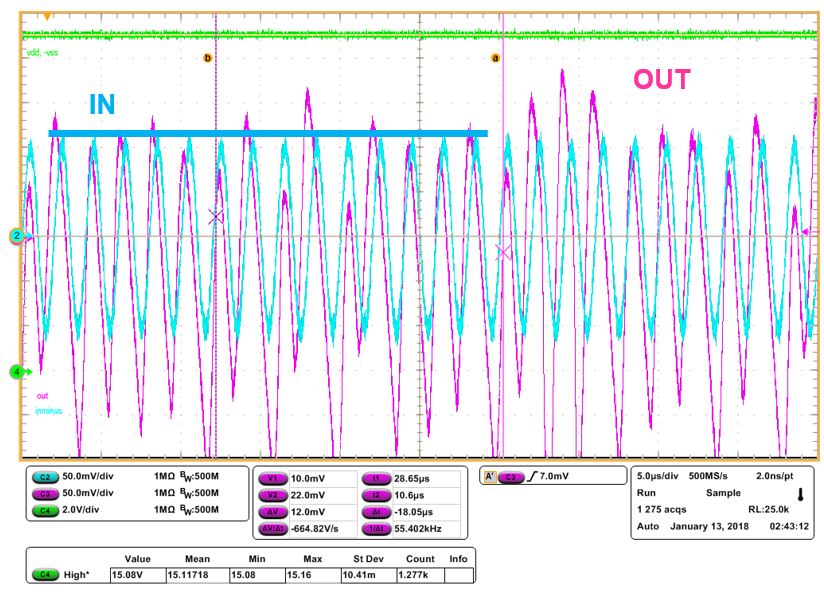

이 검사에 선택된 첫번째 연산 증폭기는 온세미컨덕터의 NCS325이다. NCS325는 다른 검사 대상 기기와 같은 초퍼 안정화 타입이 아니라 오토 제로 기술을 적용한 증폭기이다. 이론적으로 오토 제로 아키텍처는 초퍼 안정화 유형보다 더욱 극적인 에일리어싱을 나타내기 때문에 검사 확인을 위해 편의상 첫번째 연산 증폭기로 선택했다. 그림 6은 NCS325의 에일리어싱을 보여준다. 클럭 주파수는 알려져 있기 때문에 친숙한 증폭기를 먼저 측정하는 것이 검사 확인을 쉽게 해주었다.

그림 6. 단순한 +1 V/V 버퍼에서 첫번째 검사한 온세미컨덕터 NCS325증폭기의 에일리어싱 출력. 상단의 푸른색은 입력 신호를, 하단의 오렌지색은 증폭기 출력에서 관찰된 에일리어싱을 나타낸다.

현 시점에서 에일리어싱은 샘플링 증폭기의 결함이 아니라 거동(behavior)이라는 것을 기억하는 것이 중요하다. 이런 거동과 이를 방지할 수 있는 방법에 대한 지식이 있으면, 제로 드리프트 증폭기를 최상으로 작동할 수 있다.

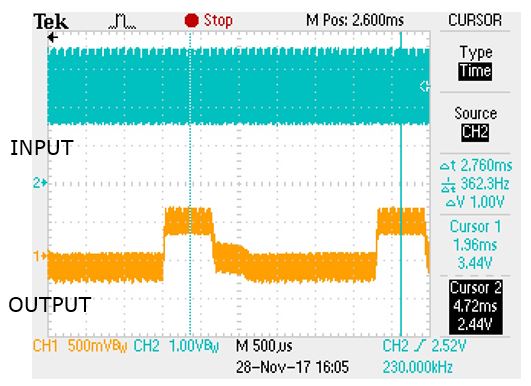

NCS325를 확인한 다음 초퍼 안정화 증폭기인 온 세미컨덕터 NCS333을 다음으로 검사했다. 이 검사에서 흥미로운 결과가 나왔다. 발견할 수 있는 유일하게 분명한 에일리어싱이 클럭 주파수의 두배에서 발생했다. 이것은 에일리어싱을 발견하기 위해 이 검사를 하기 위해서는 해당 신호를 감지하기 위해 증폭기 대역폭 전반에서 스위핑이 필요 할 수도 있다는 것을 시사한다. 그림7은 NCS333의 에일리어싱 신호를 보여준다.

그림 7. NCS333초퍼 안정화 제로 드리프트 연산 증폭기의 에일리어싱. 에일리어싱이 클럭 주파수 근처에서 발생할 것으로 예상했으나, 최선의 노력을 다했음에도 불구하고 그렇지 않았다. 그럼에도 불구하고, 에일리어싱은 클럭 주파수의 2번째 고조파에서 발생했다.

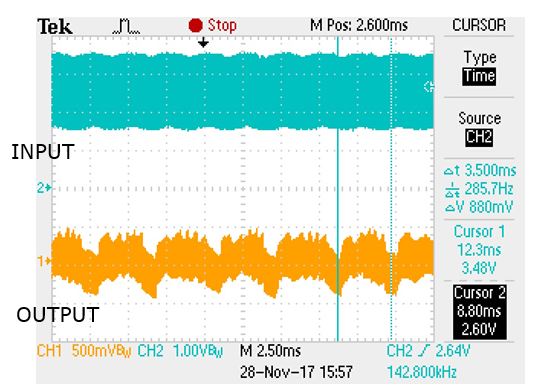

경쟁사의 제로 드리프트 초퍼 안정화 증폭기도 에일리어싱 검사를 했다. 인기 있는 이 증폭기의 데이터시트에는 에일리어싱이 없는 것으로 되어있다. 하지만, 그림 8을 보면 대략 내부 클럭의 기본 주파수에서 에일리어싱이 발생한 것을 알 수 있다. 이 증폭기의 경우, 스펙트럼 및 네트워크 분석기를 사용한 이전의 광범위한 검사에서는 클럭이나 그것의 주파수 증거를 찾을 수 없었다.

그림. 8. 경쟁사 초퍼 안정화 제로 드리프트 연산 증폭기의 에일리어싱. 5-V, 350-kHz 대역폭의 연산 증폭기의 데이터시트에는 에일리어싱이 없다고 되어있다.

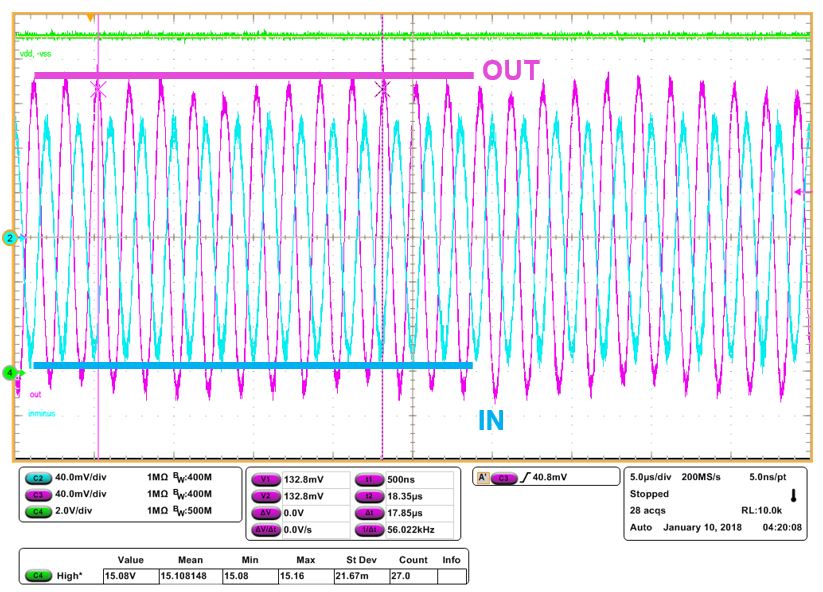

마찬가지로, 2-MHz 대역폭의 NCS21911 정밀 연산 증폭기도 그림9에서 보듯이 이득이 약 G = -1 V/V이고, 입력 신호가500 kHz일 때 에일리어싱을 보여주었다.

그림 9. 36-V, 2-MHz 정밀 증폭기 NCS21911의 에일리어싱. 에일리어싱은 500 kHz에서 그래도 상대적으로 잘 제어된다. 중앙의 파란색 부분이 입력 신호이며, 큰 자홍색 부분이 에일리어싱을 보여주는 증폭기 출력이다.

하지만, NCS21911의 에일리어싱은 그림 10에서 보는 바와 같이 동일한 조건의 또 다른 제조업체의 대응 제품과 비교해서 상대적으로 잘 제어가 되었다.

그림 10. 경쟁사의 36-V, 2-MHz 정밀 증폭기의 에일리어싱은 동일한500 kHz 신호 주파수에서 출력에서 더욱 불규칙적인 거동을 보여준다. 중앙의 파란색 부분은 입력 신호이고, 큰 자홍색 부분이 에일리어싱을 나타내는 증폭기 출력이다.

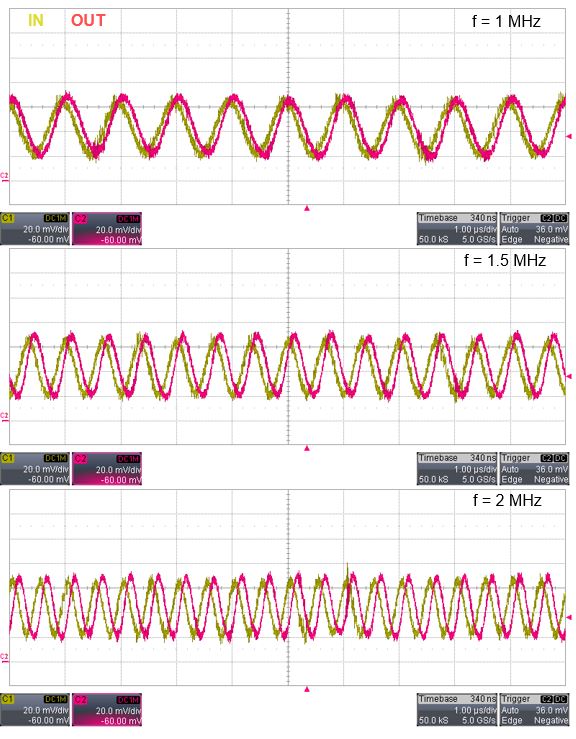

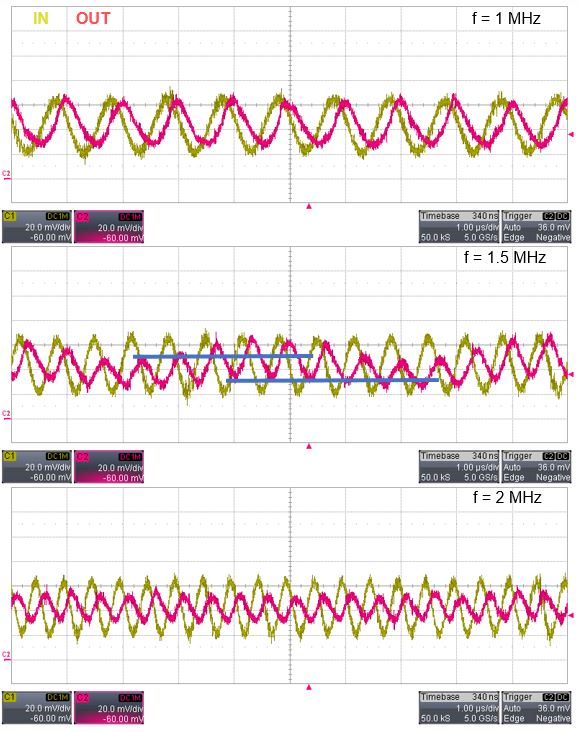

또 다른 예를 NCS21911 및 경쟁사의 2-MHz 초퍼 안정화 정밀 연산 증폭기와 비교해서 제시했다. 그림 11에서 보듯 NCS21911는 단일 이득 버퍼 회로에서 1-MHz 부터 2-MHz 범위에서 최소한의 에일리어싱을 보여준다. 반대로, 경쟁사 부품은 그림 12에 나타난 것처럼 1 MHz에서 정상적으로 거동하고, 1.5 MHz에서는 에일리어싱을 나타내다, 2 MHz에서는 (대역폭과 함께) 에일리어싱이 줄어드는 반응을 보인다.

그림 11. 1 MHz (상단), 1.5 MHz (중간), 2 MHz (하단)에서 작은 신호를 갖는 단일 이득 회로에서의 NCS21911. 에일리어싱은 최소화된다.

그림 12. 1 MHz (상단), 1.5 MHz (중간), 2 MHz (하단)에서 작은 신호를 갖는 경쟁사의 2-MHz 초퍼 안정화 정밀 증폭기. 에일리어싱 (파란색으로 표시)는 1.5 MHz에서 뚜렷하다가 입력 신호가 2 MHz로 높아지면서 약해진다. 하단 파형에서 보이는 것처럼 경쟁사 부품의 대역폭은 낮다는 점에 주목한다.

모든 초퍼 안정화 증폭기가 동일한 방식으로 구축되는 것은 아니다. 그렇기 때문에 전체 작동 주파수 범위를 대상으로 각 부품을 검사하는 것이 매우 중요하다.

에일리어싱에 민감한 시스템

관심 대상 신호가 표유 신호의 고주파 커플링이나 큰 고주파 리플을 동반하게 되는 경우 시스템은 에일리어싱에 취약해진다. 그 결과 단순히 부정확한 값이나 잡음 값이 전달되거나 제어 루프가 부정확한 동작점에 정착하게 된다.

나이퀴스트 샘플링 정리에 따르면, 제로 드리프트 클럭은 관심 신호의 최대 주파수 성분보다 최소 두 배가 되어야 한다. 다시 말하자면, 입력 신호의 최대 주파수가 증폭기 내부 클럭의 절반보다 작거나 같아야 한다는 뜻이다.

어떻게 나이퀴스트 샘플링 이론을 지킬 수 있을까? 신호 주파수에 상한선을 설정하는 것은 충분히 쉽지만(fin < fCLOCK/2), 표유 신호, 잡음 또는 리플의 픽업에 나이퀴스트 주파수보다 높은 주파수가 포함될 수 있다. 이런 주파수는 적절한 주파수 범위로 에일리어싱되어 오차나 부정확한 값을 초래할 수 있다.

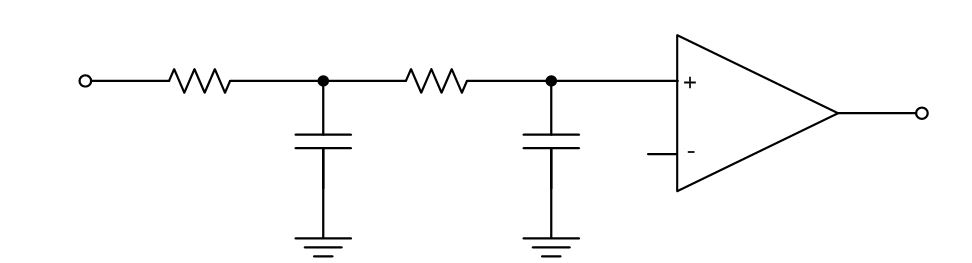

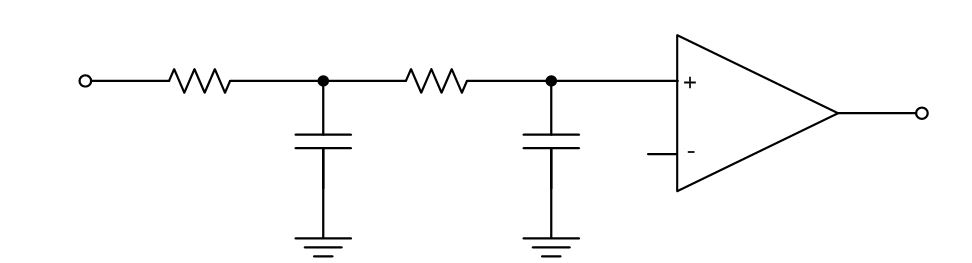

입력 신호의 주파수 성분을 사용가능한 주파수 범위로 제한하기 위해서, 저역통과필터(LPF)를 증폭기 앞에 추가할 수 있다. 이 필터가 안티 에일리어스 필터 역할을 한다. 이 필터는 (나이퀴스트 주파수 이상의) 고주파를 감쇠시켜 에일리어싱 효과를 줄이거나 제거한다.

안티 에일리어싱 필터는 반드시 증폭기 입력 앞에 완전히 아날로그인 필터로 배치해야 한다. 그림 13에 제시된 것처럼 단순한 RC 필터면 충분한 경우가 많다. 정교하고 비싼 필터 아키텍처가 필요한 경우는 드물 것이다. 능동 필터 회로에서 증폭기를 필터의 일부로 구성하지 않도록 한다.

그림 13. 안티 에일리어싱 필터는 2섹션의 RC 필터만큼 간단하게 구성할 수 있다. 필터는 반드시 증폭기 입력 앞에 배치해야 한다.

그림 13. 안티 에일리어싱 필터는 2섹션의 RC 필터만큼 간단하게 구성할 수 있다. 필터는 반드시 증폭기 입력 앞에 배치해야 한다.

다수의 클럭 주파수가 상호작용을 하여 에일리어싱을 초래할 수 있기 때문에 제로 드리프트 증폭기를 케스케이딩(cascading)해도 위험이 발생할 수 있다.

과도 응답 고려사항

초퍼 채널 아키텍처의 시간 기반 샘플링 때문에, 제로 드리프트 증폭기가 낮은 오프셋을 달성하는 데는 시간 관점이 있다. 오프셋 보정이 즉각적으로 일어나지 않는다는 의미이다. 증폭기 입력의 큰 동적 스텝이나 더 심하게는 입력 과부하로 인해 루프가 저 오프셋을 다시 만들어야 할 시간이 필요한 조건이 만들어 질 수 있다. 이렇게 되면 근본적으로 정착 시간과 거동에 영향을 주게 된다.

고클럭 주파수를 사용하면 회복과 정착 시간이 상대적으로 빨라지지만, 이러한 파라미터들은 일반적으로 제로 드리프트 증폭기의 경우 수 십 마이크로초 이상의 범위에 있다. 언제나 그렇듯이 설계상의 절충 때문에 그러한 것이다. 트랜지스터 레벨의 증폭기 설계에서 빠른 정착 시간을 선택하게 되면 오프셋 전압이 높아질 수 있다. 일반적으로 저입력 오프셋 전압 규격에 더 높은 우선순위가 주어진다.

작동(Turn-On)시간 및 강력한 설계

제로 드리프트 증폭기에는 상당한 양의 논리 회로가 포함되어 있기 때문에, 개시와 전력 공급 문제(전압저하 등)가 발생 동안 정의된 행동을 보장하는 수단이 포함된 것은 당연하다. 오프셋 보정 증폭기를 처음 작동할 때, 출력에 보정이 안된 오프셋을 반영되는 기간이 잠시 있다. 공급 전압이 POR(power-on reset) 회로로 설정한 정의된 트립점(trip-point)에 도달하게 되면, 오프셋 보정 메커니즘은 몇 클럭 사이클이 지나야 증폭기의 출력이 정의된 오프셋 전압 한도 안으로 들어오게 된다.

일반적으로 이 증폭기 개시 시간은 전체 시스템의 작동 시작 시간(power-up time) 안에 일반적으로 들어오기 때문에 전체 시스템 관점에서 보면 그렇게 중요하지 않다. 그래서, 많은 연산 증폭기 제조업체들은 이 파라미터를 제로 드리프트 증폭기 데이터시트에 포함하지 않는다. 개시 시간도 증폭기의 이득 구성에 따라 좌우된다는 것을 기억할 필요가 있다. 이득이 크면 전체 개시 시간이 늘어날 수 있다.

매우 중요한 시스템에서는 선형 증폭기는 이런 복잡함을 간단히 없애 버리고, 훨씬 더 강력한 작동 시작 성능을 구현한다는 점을 생각해 볼 필요가 있다. 일부 정밀 연산 증폭기는 초퍼 안정화나 오토 제로 아키텍처 대신 트림(trim)을 이용해서 저오프셋 전압을 달성하기도 한다. 이 경우 증폭기에서 모든 클러킹된 시스템이 제거된다. 이는 대형 산업용 회로 차단기와 같이 많은 설계에서 매우 중요한 고려사항이다. 이런 트림된, 선형 증폭기의 경우는 제로 드리프트 증폭기와 같은 초저 입력 오프셋 전압을 반드시 달성하지는 못한다는 것이 절충할 부분이다.

향상된 레일 투 레일 (Rail-To-Rail) 성능의 제로 드리프트 영향

레일 투 레일(rail-to-rail) 입력 연산 증폭기는 2개 입력 쌍을 사용해서 공통 모드 입력 전압 범위를 확대한다. 저입력 전압 영역에는 입력단으로 PMOS 쌍을, 고입력 전압 영역에는 NMOS쌍을 이용할 수 있다. 각 입력 쌍은 자체의 상응하는 입력 오프셋 전압을 갖고 있다. 공통 모드 전압이 한 영역에서 다른 영역으로 변환할 때, 일반적으로 오프셋 전압이 한 영역에서 다음 영역으로 점프를 하는 교차 영역이 있다.

제로 드리프트 연산 증폭기에서 레일 투 레일 입력 성능은 PMOS 와 NMOS의 입력 쌍 간의 입력단 교차 영역 효과를 현저하게 줄임으로써 비 제로 드리프트 증폭기에 비해 제로 드리프트 증폭기에 상당한 혜택을 준다. 공통 모드 입력 전압 한도에 가까운 오프셋 전압과 오프셋 전압 드리프트 성능은 탁월하다. 이런 이유로 제로 드리프트 증폭기가 하이 사이드(high-side) 전류 감지와 같은 애플리케이션에서도 많이 쓰이는 것이다.

저주파 잡음에 미치는 제로 드리프트 영향

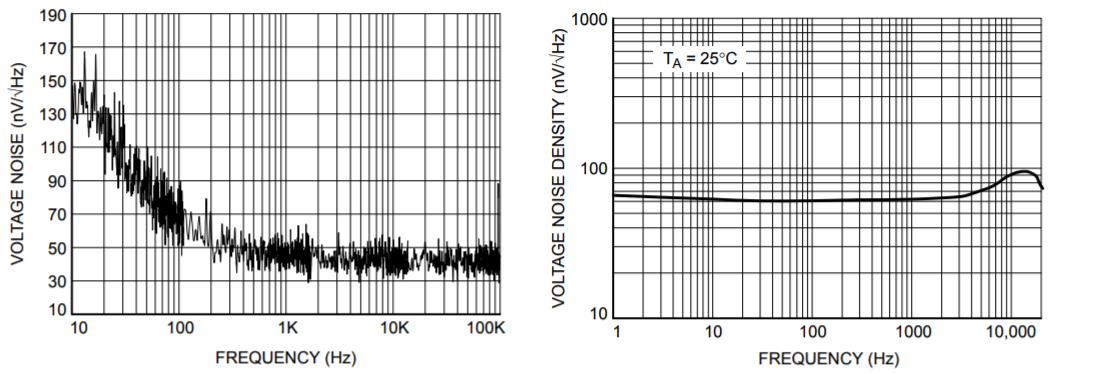

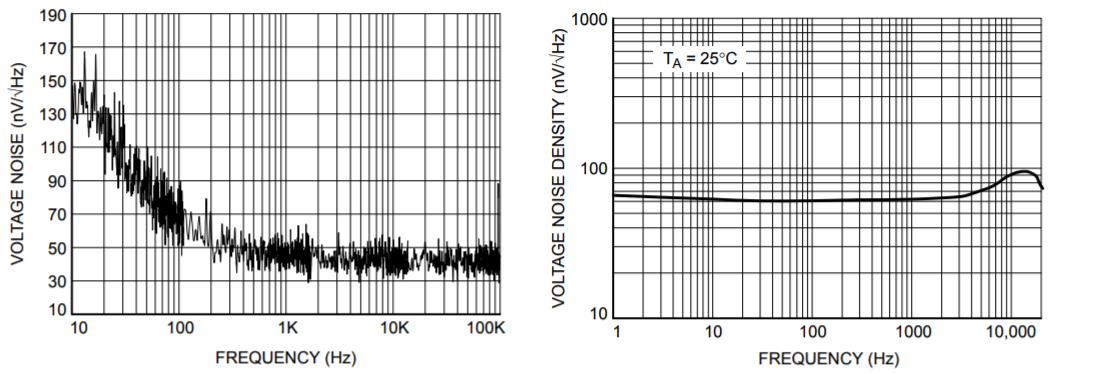

제로 드리프트 초퍼 안정화 증폭기는 저 주파수에서 정확한, 고이득 증폭을 하는데 특히 적합하다. 일반적으로, 선형 연산 증폭기의 고대역폭을 나타내지 않고, 에일리어싱 섹션에서 살펴본 것처럼 클럭 주파수의 위치가 신호 충실도에 현실적인 주파수 한도를 설정한다. 그래서 저주파수의 성능이 특히 중요하다. 초퍼 안정화 아키텍처는 전형적인 선형 연산 증폭기 1/f 입력 전압 잡음을 제거함으로써 저주파수 유용성을 더욱 확대한다(그림 14 참조).

많은 고이득 센서 애플리케이션은 저주파수에 있기 때문에, 이 기능의 경우 자연스럽게 제로 드리프트 증폭기를 선택하게 된다. 여기서 ‘저주파수’라는 용어를 사용하기는 하지만, 이런 증폭기는 일반적으로 최고 약 100 kHz까지 탁월한 성능을 제공한다.

(a) (b)

(a) (b)

전압 잡음과 마찬가지로, 초퍼 안정화도1/f 전류 잡음을 제거한다. 하지만, 초퍼 안정화 증폭기는 입력 스위치의 전하 주입때문에 초핑의 입력 전류 잡음이 높아진다. 이렇게 늘어난 전류는 입력 임피던스(impedance)가 전압 잡음 레벨 이상으로 잡음을 유발하는 레벨을 낮춘다. 1 kHz에서 입력 전압 잡음이 62-nV/√Hz인 NCS333을 예로 이용하면, 177 kΩ 이상의 입력 임피던스가 사용될 때 잡음이 입력 전압 잡음을 초과하게 될 것이다.

이와 비교하여, 제로 드리프트 오토 제로 증폭기는 잡음을 베이스밴드까지 에일리어싱한다. 그래서, 입력 신호가 dc나 저주파수에 있을 때는 오토 제로 아키텍처가 초퍼 안정화 아키텍처에 비해 불리하다.

입력 전류에 미치는 제로 드리프트 영향

초퍼 안정화 방법 때문에 입력 전류 스파이크는 모든 제로 드리프트 증폭기에 존재한다. 이런 전류 스파이크는 전하 주입과 클럭 피드쓰루(clock feedthrough)에 의해 발생한다. 입력 전류는 평균으로 계산하면 IIB 규격으로 되지만, 입력 바이어스가 정확히 일정한 것은 아니다. 실제로는 입력 전류 스파이크가 클럭 주파수와 정기적으로 발생한다.

입력 전류가 입력 저항기 전반에서 끌어당기면서, 입력 전압 스파이크가 발생하고, 이는 이득으로 곱할 수 있다. 전압 스파이크를 최소화하기 위해서, 아주 큰 입력 저항기 값은 권장하지 않는다. 입력 전류 스파이크는 앞서 그림 13에 제시된 것처럼 단순한 저역 통과 RC 필터로 필터링할 수 있다. 필터 주파수는 초퍼 샘플링 레이트보다 낮게 설정해야 한다.

또한, 입력 전력 스파이크 때문에 제로 드리프트 증폭기는 입력 전류를 측정하도록 만들어진 트랜스임피던스 증폭기(TIA)에는 매우 적합하지 않다.

스파이스 모델에서 제로 드리프트 영향 부재

스파이스(Spice) 시뮬레이션은 에일리어싱과 같은 제로 드리프트 거동에 대해 어떤 정보도 제공해주지 않는다. 제로 드리프트 증폭기의 모든 스파이스 모델은 연속 시간 모델이다. 연산 증폭기의 선형 성능을 가능한 비슷하게 모델링하기 위해 만들어졌다. 초퍼는 모델링된 것이 아니다. 클럭킹되고 샘플링된 시스템은 훨씬 느리게 시뮬레이션되기 때문에 연속 시간이다.

결론

제로 드리프트 증폭기는 탁월한 dc 및 저주파수 성능을 제공한다. 이득 대역폭 곱은 제로 드리프트 증폭기 회로의 실질적인 대역폭을 결정하는데 이상적인 규격이 아니다. 특히, 내부 클럭이 이 대역폭 안에 있기 때문에 더욱 그러하다. 최고 성능을 달성하기 위해서는 항상 제공되지는 않는 내부 클러킹 주파수를 알아야 한다. 하지만, 때때로 다른 단서와 검사를 통해 내부 클러킹 주파수를 파악할 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)

(a) (b)

(a) (b)