대만의 알칩 테크놀로지스(Alchip Technologies)가 16일 3차원 집적회로(3DIC) 설계 서비스를 공식적으로 개시했다고 발표했다.

알칩 3DIC 서비스는 단일 패키지 내에 여러 개의 칩을 수직으로 적층하는 AI 및 고성능 컴퓨팅(HPC) 애플리케이션을 겨냥한 최신 고성능 ASIC을 대상으로 한다.

알칩은 2nm 테스트 칩을 테이프아웃(tape-out)했으며, 이번 분기 내에 결과를 받을 것으로 예상하고 있다. 또한, 고성능 2nm ASIC 개발을 위해 고객과 활발히 협력하고 있다.

알칩이 새롭게 제공하는 3DIC 설계 플로는 정적 및 동적 IR 드롭, 하위 다이와 상위 다이 간의 전력 노이즈 전파, 상위 및 하위 다이 간의 서로 다른 전력 도메인 및 공유된 접지면(ground plane) 문제를 포함한 전력 통합 문제를 해결한다.

알칩이 새롭게 제공하는 3DIC 설계 플로는 정적 및 동적 IR 드롭, 하위 다이와 상위 다이 간의 전력 노이즈 전파, 상위 및 하위 다이 간의 서로 다른 전력 도메인 및 공유된 접지면(ground plane) 문제를 포함한 전력 통합 문제를 해결한다.

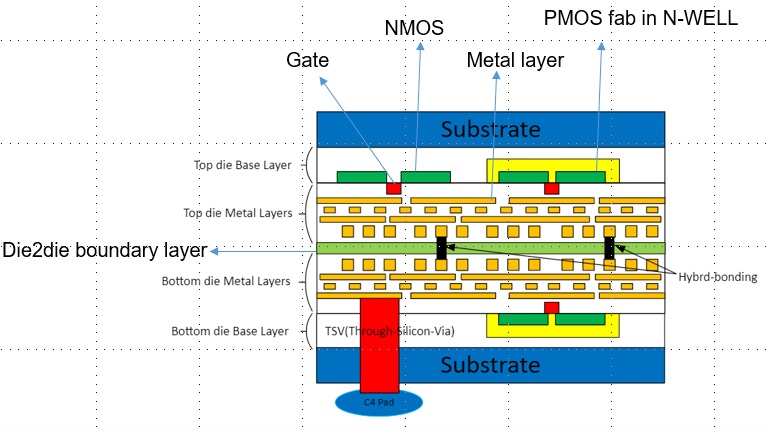

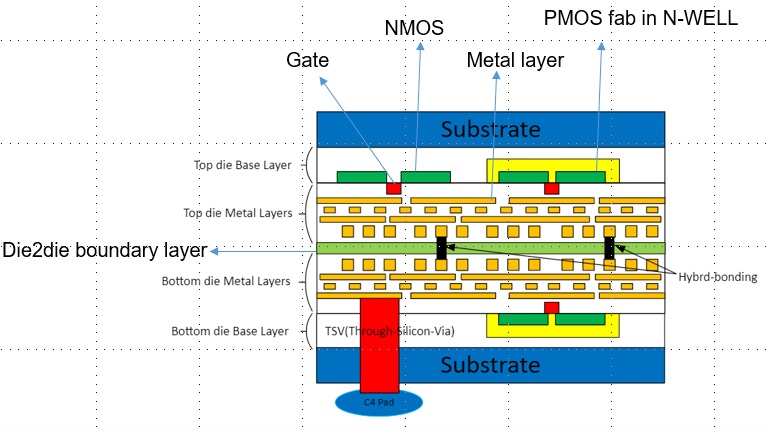

3DIC 서비스는 실리콘 관통전극(Through-Silicon Via, TSV)과 하이브리드 본딩을 활용해 적층된 칩을 통합함으로써 기존 2차원 설계에 비해 데이터 전송 속도를 높이고, 전력 소비를 줄이며, 설치 공간을 더 작게 만들 수 있다. 향후 이러한 애플리케이션의 설계는 클라우드 및 네트워킹 인프라, 모바일 기기, 그래픽 처리 장치(GPU)에서 높은 성능과 효율성을 요구할 것이다.

알칩의 실리콘 검증을 거친 3DIC 설계 플로는 전력 공급, 다이 간 전기적 상호 연결, 시스템 전반의 열 특성화라는 세 가지 핵심 측면에서 선택된 3DIC 설계를 최적화했다.

새로운 3DIC 설계 플로의 전력 공급 모듈은 전력 무결성, TSV 분포를 포함한 전력망 설계, 전력 무결성 시뮬레이션 및 사인오프 기능을 포함한다.

다이 간 전기적 상호 연결 기능은 다이 간 낮은 클록 스큐(clock skew) 공정 변동 내성, 노이즈 내성, 서로 다른 전력 도메인 간 데이터 전송, 다이 간 셋업/홀드 타이밍 마진을 식별하고 처리한다. 또한, 이 기능은 클록 및 데이터에 최적화된 전력-성능-영역(PPA) IO 셀과 이중화(redundancy) 전략도 다룬다.

알칩의 3DIC 설계 플로는 전력 밀도를 높이고, 3D 비균일 전력 매핑을 수행하며, 3D 열 누화(crosstalk) 효과를 완화하고, 패키지 및 시스템 냉각 솔루션 모델링을 제공하는 열 특성화도 포함된다.

알칩의 에레즈 샤이자프(Erez Shaizaf) 최고기술책임자(CTO)는 “알칩은 멀티 다이 설계를 촉진하기 위해 수년 동안 EDA, 파운드리, OSAT 파트너와 협력해 왔다. 이제 수개월 간의 노력의 결실로 고성능 ASIC 시장에 차세대 3DIC ASIC 설계의 복잡성을 비용 효율적으로 처리하는 설계 플로를 제공할 수 있게 됐다”라고 말했다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>