글|알렉스 주(Alex Zou), 선임 필드 애플리케이션 엔지니어(FAE), 아나로그디바이스

이 글에서는 ADI의 IF와 RF 컨버터에서의 집적 DDC 및 DUC 채널을 살펴보고 실제 애플리케이션에서 어떤 식으로 작동하는지 설명한다.

스마트폰의 다양한 기능들로 인해 데이터에 대한 수요가 나날이 증가하고 있다. 이를 충족시키기 위해 현대 디지털 이동통신 시스템의 인프라 아키텍처는 더 넓은 대역과 보다 빠른 데이터 변환을 수용하도록 꾸준히 진화하고 있다. 현재 데이터 변환 아키텍처에서 보다 빠른 데이터율을 달성하는데 사용되는 기능 처리 블록에는 디지털 IF 처리, 디지털 다운컨버터(DDC), 디지털 업컨버터(DUC)가 있다.

이러한 디지털 기능은 DSP 및 FPGA 내에서 구현될 수 있으며, 일부 대기업들은 디지털 IF 처리 주문형 반도체(ASIC)를 자체적으로 제작하는 곳도 있다. ADI는 고속 컨버터 IC에 이러한 디지털 IF 처리 블록을 더 많이 집적시키기 위해 노력하고 있다. 이렇게 집적도가 높아지면 설계 업무의 강도가 크게 완화되며 시스템의 비용 및 전력도 절감할 수 있다.

고속 컨버터는 현대 무선 기지국 시스템에서 주요 성능 가운데 하나를 제공한다. 시스템 설계에서 FPGA의 역할을 간소화시키기 위해 이러한 고속 컨버터는 점점 더 복잡한 디지털 신호 처리 블록에 집적되는 추세다. 컨버터에서 디지털 신호 처리 블록은 시스템 설계에 중요한 혜택을 제공하지만, 이 혜택을 충분히 이해하는 엔지니어는 아직까지 많지 않은 것으로 보인다.

이 글에서는 데이터 컨버터에서 DDC 및 DUC의 성능을 명확히 밝히고자 하며, 시스템 설계자들이 ADI 컨버터가 송수신기 구조에서 제공하는 혜택을 충분히 활용할 수 있게 되기를 바란다. 또한 이 글은 ADC 및 DAC의 디지털 처리 블록을 집중적으로 소개하며 송신기 및 수신기 블록은 묶어서 일부 설명하고 넘어간다는 점을 알아두길 바란다. 이외에 신호의 흐름 방향(signal flow direction)의 경우 혼란을 야기한다면 생략해도 된다.

현대 디지털 이동통신 시스템에서 송수신 경로(아래에서 설명하는 관측 수신 경로 포함)는 신호의 특성을 기반으로 RF 단계, 아날로그 IF 단계, 디지털 IF 단계 이렇게 세 개의 주요 단계로 나눌 수 있다.

〈그림 1〉은 일반적인 송신기 및 수신기의 블록 다이어그램을 나타낸다. RF 단계에서는 RF 신호를 처리하며, 이때 현재의 LTE 표준에서 RF 신호의 주파수 범위는 일반적으로 700 MHz ~ 3.5 GHz다.

믹서, 변조기, 복조기와 같은 모든 주파수 천이 단계를 거친 RF 신호는 DC 근처의 더 낮은 주파수, 300 MHz 보다 낮은 주파수대로 변환된다. 데이터 컨버터와 믹서 사이의 프로세스 모듈에는 컨버터(ADC 또는 DAC), 아날로그 필터, IF 증폭기가 포함되며, 이 단계를 아날로그 IF 단계라고 한다. 컨버터, 더 엄밀히 말하면 컨버터의 양자화기(quantizer)를 통과한 신호는 디지털로 변환되며, 이후 FPGA 또는 ASIC를 지난다. 이 단계를 디지털 IF 단계라고 한다. 이 단계에서 개별 디지털 신호 처리 블록에 대한 일반적인 용어는 Tx 경로일 때 DUC(디지털 업컨버터), Rx 경로일 때 DDC(디지털 다운컨버터)다.

예외는 RF 직접 변환 아키텍처에서 발생하는데 이때 데이터 컨버터가 RF 신호를 직접 샘플링하게 되어 아날로그 IF 단계가 생략되고 그 결과 신호 체인은 RF 단계와 디지털 IF 단계만으로 이루어진다.

DDC 모듈(Typ)에는 반송파 선택, 주파수 다운컨버터, 필터 및 데시메이터가 포함된다. 이러한 기능 블록은 차례대로 작동하거나, 또는 신호가 각각의 블록을 우회해 최종적으로 기능 블록이 DC에서 복소 신호를 생성하거나, 더 낮은 샘플링레이트를 갖는 FPGA 또는 ASIC의 요건에 따라 실제 신호를 생성할 수 있다.

일반적인 DUC 모듈에는 보간, 필터, 주파수 업컨버터, 반송파 결합기가 포함된다. DUC는 시스템 아키텍처 설계에 따라 DC에서, IF 기반으로 또는 RF에서 직접 복소 신호를 생성한다. DDC와 비교해 해당 처리 과정이 DDC의 처리 과정과 거의 정반대라는 사실을 알 수 있다.

여러 단계의 DDC와 DUC는 종종 유연성을 위해 각각 캐스케이드 방식으로 연결된다. 개별 DDC 및 DUC는 여러 개의 반송파를 병렬로 처리하고, 이들을 전송신호로 출력하기 전에 함께 결합하거나 수신 신호에서 분리해야 한다.

DDC

Rx 체인에서 샘플링레이트가 높을수록 신호 앨리어싱을 피할 수 있으며, 아날로그 필터 설계가 수월하고 더 넓은 신호 대역을 제공할 수 있다. 그러나 다른 한편으로는 인터페이스 상에서 전력 및 비용을 절감할 수 있고 FPGA/ASIC에서 고속 로직도 가능해져 보다 낮은 데이터율이 선호되기도 한다. 컨버터의 집적 DDC는 위의 요건을 만족시킨다.

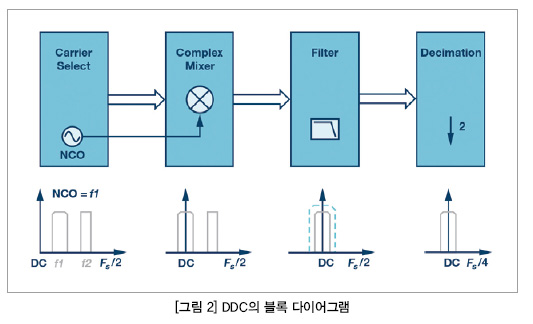

〈그림 2〉는 일반적인 DDC의 블록 다이어그램을 보여준다.

NCO + 믹서

차단기, 간섭, 또는 다른 반송파로 부터 원하는 반송파를 선택하기 위해 NCO의 출력 주파수는 입력 IF 신호와 혼합되어 원하는 반송파를 DC로 천이 한다. 이렇게 하면 그 뒤의 필터 및 데시메이터 단계의 복잡성이 줄어든다.

필터와 데시메이션

NCO와 믹서 단계의 다음으로 원하는 반송파를 선택하고 그 외의 원치 않는 신호 억제하기 위해서는 저역 필터가 사용된다. 필터 다음 단계에서는 데시메이터가 데이터율을 두 배 더 낮춘다.

리소스를 절약하고 고객사를 대상으로 유연성을 제공하기 위해서는 하프밴드 FIR 필터와 데시메이터를 하나의 블록에 결합하고, 그 블록을 복제해 3~4 단계로 캐스케이드 되도록 붙여 넣는다.

시스템 설계자는 애플리케이션에 따라 이들 일부 또는 전체를 선택해 사용할 수 있다. 특히 RF ADC에서 유연성을 추가로 향상시키기 위해 2 배 이상의 데시메이션을 할 수도 있다.

DUC

Tx 체인에는 Rx 체인과 동일한 요건이 존재하며, 높은 샘플링레이트는 필터설계가 쉽고 높은 IF 또는 RF 상에 직접신호를 위치시키고, 이미지 신호를 멀리 보내기 때문에 선호되는 반면, 낮은 데이터율은 인터페이스용으로 선호된다. 컨버터에 집적된 DUC는 이러한 요건을 만족시킨다.

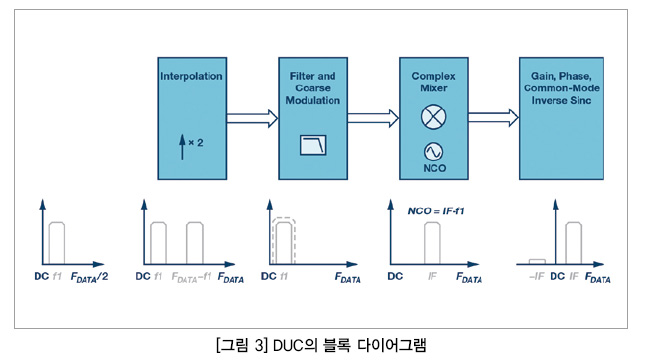

〈그림 3〉은 일반적인 DUC의 블록 다이어그램을 보여준다.

보간법과 필터링

가장 단순한 디지털 보간법 알고리즘은 제로 패딩이라고 하며, 이는 모든 다른 샘플에 0을 삽입해서 샘플링레이트를 두 배로 높이는 것을 뜻하지만, 이로 인해 얻어진 스펙트럼 내의 FS -Fif에서 이미지 신호도 생성된다. 따라서 보간기 다음에 필터 단계를 거쳐야 애플리케이션에 따라 이미지 신호나 기존의 반송파를 제거할 수 있다. 기존의 반송파가 제거되면, 그 결과 신호가 보간되고 FS /2로 거친 변조가 발생된다.

DDC에서처럼 두 배의 보간과 필터가 하나의 블록으로 결합되면 유연성을 위해 이 기능 블록을 복사해 붙여넣고 3~4 단계 캐스케이드한다. 특히 RF DAC에서의 유연성을 향상시키려면 2배 이상으로 보간이 사용된다.

NCO+ 믹서

DDC의 NCO와 믹서 블록과 거의 동일하게 DUC에서 NCO와 믹서 단계의 다음 단계는 시스템 아키텍처의 요건에 따라 반송파를 원하는 IF 또는 RF 주파수로 변환하는 데 사용된다. ZIF 아키텍처에서 NCO와 믹서 블록은 반송파를 DC로 유지시키기 위해 우회된다.

이득, 위상, I/Q 오프셋, 반동기화 블록

이득, 위상 조정, I/Q 오프셋, Anti-Sinc 블록은 IF/RF DAC에 부수적으로 포함되는 경우가 많다.

이득과 위상 조정, I/Q 오프셋 블록은 종종 함께 동작해 출력 신호 I/Q 채널을 개별적으로 조정한다. 그리고 DAC, 아날로그 필터 및 변조기에 의해 발생하는 서로 다른 종류의 I/Q 불일치를 보정해 낮은 LO 누설 및 이미지 신호와 함께 아날로그 변조기를 통과시킨다. 이렇게 하면 마침내 완벽한 복소 신호를 얻을 수 있게 된다.

Anti-Sinc 필터는 DAC에 의해 발생하는 Sinc roll-off를 보정한다. Sinc rolloff는 특히 높은 IF 또는 DRF 아키텍처상의 광대역 애플리케이션에서 주파수 편평도에 영향을 미친다.

맺음말

이 글에서는 IF/RF 컨버터에 집적되는 일반적인 DDC와 DUC가 무엇인지, 또 신호 체인에서 어떻게 작동하며 그 원리가 무엇인지에 대해서도 간단히 설명했다. 이를 이해하고 적절히 사용하면 FPGA/ASIC에서의 리소스를 절약하고 코드 작업도 줄일 수 있으며, 그 결과 시스템의 전력과 비용을 절감할 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>