Imec, 300mm Si 웨이퍼에 GaAs 기반 나노리지 레이저 제작

2025-01-10 윤범진 기자, esmaster@elec4.co.kr

벨기에 루벤에 소재한 유럽 최대 규모의 비영리 종합 반도체 연구소인 Imec이 실리콘 포토닉스 분야에서 중요한 이정표를 세웠다.

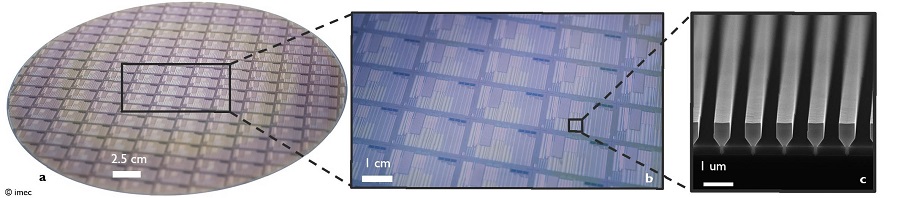

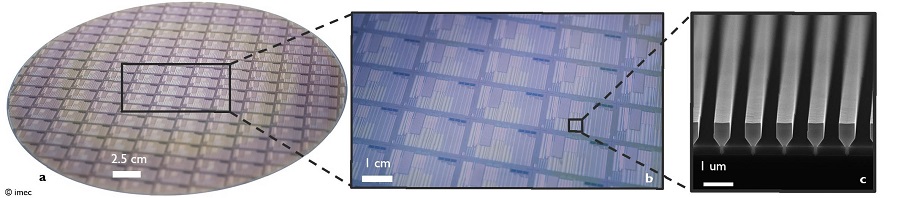

Imec은 9일 300mm 실리콘(Si) 웨이퍼 위에 전기 펌핑 GaAs(갈륨비소) 기반 나노리지(nanoridge) 레이저를 최초로 전체 웨이퍼 규모로 제작하는 데 성공했다고 발표했다.

5mA의 낮은 문턱 전류(threshold currents)와 1mW 이상의 출력 전력으로 실온 연속파(CW) 레이저를 달성한 이 성과는 실리콘에서 고품질 III-V 재료의 직접 에피택셜 성장 가능성을 입증했다. 이 결과는 지난주 네이처(Nature) 지에 자세히 소개됐다.

이 성과는 데이터 통신, 머신 러닝 및 인공 지능 분야의 애플리케이션에서 비용 효율적인 고성능 광학 장치를 개발할 수 있는 길을 제시했다. 레이저를 실리콘 칩에 통합하면 칩렛과 칩 간 상호 연결을 위한 더 많은 옵션이 제공된다.

확장성이 뛰어난 네이티브 CMOS 통합 광원의 부족은 실리콘 포토닉스의 광범위한 채택을 가로막는 주요 장애물이었다. 이로 인해 플립칩, 마이크로 전사 프린팅 또는 다이-투-웨이퍼 본딩과 같은 하이브리드 또는 이기종 통합 솔루션에는 복잡한 본딩 공정이 필요하거나 처리 후 폐기되는 고가의 III-V 기판이 필요하다. 이는 비용을 증가시킬 뿐만 아니라 지속 가능성과 자원 효율성에 대한 우려를 제기한다. 이에 대형 실리콘 포토닉스 웨이퍼에 고품질 III-V 광학 이득(gain) 재료를 선택적으로 직접 에피택셜 성장시키는 기술이 많은 관심을 받고 있다.

주요 문제 중 하나는 III-V 재료와 실리콘 재료 간의 결정 격자(crystal lattice) 파라미터와 열팽창 계수가 크게 불일치한다는 것이다. 이로 인해 결정 결함이 발생해 레이저 성능과 신뢰성이 저하된다. 종횡비 포획(Aspect Ratio Trapping, ART)과 결합된 선택영역성장(Selective-Area Growth, SAG)은 유전체 마스크에 에칭된 좁은 트렌치 또는 나노리지 내에 전위를 구속(confining)함으로써 실리콘에 통합된 III-V 재료의 결함을 크게 줄인다.

전기 구동(electrically-driven) GaAs 다중 양자우물(multi-quantum-well) 나노리지 레이저 다이오드는 imec CMOS 파일럿 프로토타입 라인에서 300mm 실리콘 웨이퍼에 모놀리식으로 제작됐다.

imec의 버나뎃 쿤에르트(Bernardette Kunert) 과학 책임자는 “지난 몇 년 동안 imec은 트렌치 외부에서 결함이 적은 III-V 나노리지를 성장시키기 위해 SAG와 ART를 기반으로 하는 나노리지 기술을 개척해 왔다. 이 접근 방식은 결함을 줄일 뿐만 아니라 재료 치수와 구성을 정밀하게 제어할 수 있다”라고 전했다.

최적화된 나노리지 구조는 일반적으로 관통 전위 밀도(threading dislocation densities)가 105 cm-2 이하로 매우 낮아, 광학 이득 영역으로 사용되는 InGaAs(인듐갈륨비소) 다중 양자우물(MQW)에서 레이저 발진이 가능하다. 이 구조는 in-situ 도핑 p-i-n 다이오드에 내장되고 InGaP(인듐갈륨인) 캡핑 층으로 보호된다. 전기 주입을 통한 실온 연속파(CW) 동작의 구현은 전류 전달 및 인터페이스 엔지니어링의 과제를 극복한 중요한 진전이다.

이 소자는 5mA의 낮은 문턱 전류, 최대 0.5W/A의 기울기 효율(slope efficiencies), 1.75mW에 이르는 광 출력으로 약 1020nm에서 레이저를 발진한다.

쿤에르트 과학 책임자는 “imec은 III-V 나노리지 엔지니어링 개념을 활용해 CMOS 파일럿 제조 라인 내에서 표준 300mm 실리콘 웨이퍼에 전기 펌핑(electrically pumped) GaAs 기반 레이저를 웨이퍼 전체 규모로 제작하는 데 최초로 성공했다”라고 강조했다.

imec의 요리스 반 캄펜하우트(Joris Van Campenhout) 실리콘 포토닉스 펠로우이자 광학 I/O 산업 제휴 R&D 프로그램 책임자는 “대구경 Si 웨이퍼 위에 비용 효율적으로 고품질 III-V 이득 재료를 통합하는 것은 차세대 실리콘 포토닉스 응용 분야를 가능하게 하는 핵심 요소이다. 이러한 혁신적인 나노리지 레이저 결과는 모놀리식 III-V 통합을 위한 직접 에피택셜 성장을 이용하는 데 있어 중요한 이정표가 될 것”이라고 전했다.

이 프로젝트는 단기적으로 플립칩과 전사 프린팅 하이브리드 기술에서, 이기종 웨이퍼 및 다이 본딩 기술을 거쳐 장기적으로 직접 에피택셜 성장으로 이어지는 III-V 통합 공정을 더 높은 기술 준비 상태로 발전시키기 위한 imec의 더 큰 경로 탐색 임무의 일부이다.

Imec은 9일 300mm 실리콘(Si) 웨이퍼 위에 전기 펌핑 GaAs(갈륨비소) 기반 나노리지(nanoridge) 레이저를 최초로 전체 웨이퍼 규모로 제작하는 데 성공했다고 발표했다.

5mA의 낮은 문턱 전류(threshold currents)와 1mW 이상의 출력 전력으로 실온 연속파(CW) 레이저를 달성한 이 성과는 실리콘에서 고품질 III-V 재료의 직접 에피택셜 성장 가능성을 입증했다. 이 결과는 지난주 네이처(Nature) 지에 자세히 소개됐다.

이 성과는 데이터 통신, 머신 러닝 및 인공 지능 분야의 애플리케이션에서 비용 효율적인 고성능 광학 장치를 개발할 수 있는 길을 제시했다. 레이저를 실리콘 칩에 통합하면 칩렛과 칩 간 상호 연결을 위한 더 많은 옵션이 제공된다.

확장성이 뛰어난 네이티브 CMOS 통합 광원의 부족은 실리콘 포토닉스의 광범위한 채택을 가로막는 주요 장애물이었다. 이로 인해 플립칩, 마이크로 전사 프린팅 또는 다이-투-웨이퍼 본딩과 같은 하이브리드 또는 이기종 통합 솔루션에는 복잡한 본딩 공정이 필요하거나 처리 후 폐기되는 고가의 III-V 기판이 필요하다. 이는 비용을 증가시킬 뿐만 아니라 지속 가능성과 자원 효율성에 대한 우려를 제기한다. 이에 대형 실리콘 포토닉스 웨이퍼에 고품질 III-V 광학 이득(gain) 재료를 선택적으로 직접 에피택셜 성장시키는 기술이 많은 관심을 받고 있다.

주요 문제 중 하나는 III-V 재료와 실리콘 재료 간의 결정 격자(crystal lattice) 파라미터와 열팽창 계수가 크게 불일치한다는 것이다. 이로 인해 결정 결함이 발생해 레이저 성능과 신뢰성이 저하된다. 종횡비 포획(Aspect Ratio Trapping, ART)과 결합된 선택영역성장(Selective-Area Growth, SAG)은 유전체 마스크에 에칭된 좁은 트렌치 또는 나노리지 내에 전위를 구속(confining)함으로써 실리콘에 통합된 III-V 재료의 결함을 크게 줄인다.

전기 구동(electrically-driven) GaAs 다중 양자우물(multi-quantum-well) 나노리지 레이저 다이오드는 imec CMOS 파일럿 프로토타입 라인에서 300mm 실리콘 웨이퍼에 모놀리식으로 제작됐다.

imec의 버나뎃 쿤에르트(Bernardette Kunert) 과학 책임자는 “지난 몇 년 동안 imec은 트렌치 외부에서 결함이 적은 III-V 나노리지를 성장시키기 위해 SAG와 ART를 기반으로 하는 나노리지 기술을 개척해 왔다. 이 접근 방식은 결함을 줄일 뿐만 아니라 재료 치수와 구성을 정밀하게 제어할 수 있다”라고 전했다.

최적화된 나노리지 구조는 일반적으로 관통 전위 밀도(threading dislocation densities)가 105 cm-2 이하로 매우 낮아, 광학 이득 영역으로 사용되는 InGaAs(인듐갈륨비소) 다중 양자우물(MQW)에서 레이저 발진이 가능하다. 이 구조는 in-situ 도핑 p-i-n 다이오드에 내장되고 InGaP(인듐갈륨인) 캡핑 층으로 보호된다. 전기 주입을 통한 실온 연속파(CW) 동작의 구현은 전류 전달 및 인터페이스 엔지니어링의 과제를 극복한 중요한 진전이다.

이 소자는 5mA의 낮은 문턱 전류, 최대 0.5W/A의 기울기 효율(slope efficiencies), 1.75mW에 이르는 광 출력으로 약 1020nm에서 레이저를 발진한다.

쿤에르트 과학 책임자는 “imec은 III-V 나노리지 엔지니어링 개념을 활용해 CMOS 파일럿 제조 라인 내에서 표준 300mm 실리콘 웨이퍼에 전기 펌핑(electrically pumped) GaAs 기반 레이저를 웨이퍼 전체 규모로 제작하는 데 최초로 성공했다”라고 강조했다.

imec의 요리스 반 캄펜하우트(Joris Van Campenhout) 실리콘 포토닉스 펠로우이자 광학 I/O 산업 제휴 R&D 프로그램 책임자는 “대구경 Si 웨이퍼 위에 비용 효율적으로 고품질 III-V 이득 재료를 통합하는 것은 차세대 실리콘 포토닉스 응용 분야를 가능하게 하는 핵심 요소이다. 이러한 혁신적인 나노리지 레이저 결과는 모놀리식 III-V 통합을 위한 직접 에피택셜 성장을 이용하는 데 있어 중요한 이정표가 될 것”이라고 전했다.

이 프로젝트는 단기적으로 플립칩과 전사 프린팅 하이브리드 기술에서, 이기종 웨이퍼 및 다이 본딩 기술을 거쳐 장기적으로 직접 에피택셜 성장으로 이어지는 III-V 통합 공정을 더 높은 기술 준비 상태로 발전시키기 위한 imec의 더 큰 경로 탐색 임무의 일부이다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

100자평 쓰기