[연재 기고] 타이밍 보정 통해 빠른 주파수에서 동작하는 반도체 칩 구현하기

2024-01-16 고려대학교 주병권 교수님 연구실

디지털 회로 신호 시간 보정 방법론

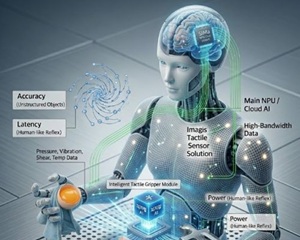

AI를 활용한 솔루션이 발전하면서 대용량 연산이 가능한 NPU(Neural Processing Unit)가 등장했다. 경쟁력 있는 NPU를 개발하기 위해서는 많은 양의 연산을 빠른 시간에 수행해야 한다. 즉, 매우 빠른 주파수를 기반으로 하고 효율적인 전력 사용에 초점을 맞춘 고사양 NPU를 개발해야 한다. 따라서 고사양 NPU에서 데이터가 정상적으로 이동하기 위해서는 빠른 속도의 주파수로 인해 더 어려워진 셋업 타임(setup time rule) 과 홀드 타임 (hold time rule)을 효율적으로 만족시키는 방법이 중요해졌다. 빠른 속도의 주파수로 동작하기 위한 타이밍 규칙에 위배되지 않도록 조정하는 방법들과 그에 따른 효율적인 방법론을 알아보자.

.jpg)

글/ 고려대학교 주병권 교수님 연구실

주병권 (고려대학교 전기전자공학부 교수)

홍재원 (고려대학교 전기전자컴퓨터 공학부 석사 과정)

목 차

1. 회로에서 타이밍 이란?

1-1 셋업타임 과 홀드타임

2. 회로에서 타이밍을 계산하는 방법

3. 회로에서 타이밍을 보정하는 방법

3-1 셀 크기 조정

3-2 셀 문턱전압 조정

3-3 셀 삽입 / 삭제

3-4 메탈 조정

3-5 셀 복제

4. 결론

5. 참고 문헌

1. 회로에서 타이밍 이란?

반도체 회로에서의 타이밍을 이해하기 위해서는 클럭(clock)의 개념이 선제되어야 한다. 클럭 은 회로의 상태가 연속적으로 진행되는데 사용되는 반복적인 파형(wave)이라고 해석할 수 있다. 타이밍은 클럭의 주기(period) 안에 데이터를 올바르게 이동시킬 수 있는 규칙을 의미한다[5]. 대표적인 두 가지 규칙이 셋업 타임과 홀드 타임이다.

1-1. 셋업타임 과 홀드타임

[9] 셋업 타임이란, 동기 신호의 데이터는 반드시 클럭엣지 이전에 안정한 상태로 도착해야 하는 시간이라 정의한다. 홀드 타임이란, 동기 신호의 데이터는 반드시 클럭엣지 이후에 안정한 상태로 유지되어야 하는 시간이라 정의한다.

.jpg)

그림 1을 통해 알 수 있듯이 셋업 타임이 위배된 경우 DATA_B 가 클럭엣지에서 셋업 타임 보다 이전에 들어오지 못하고 DATA_A가 들어온 이후 DATA_B로 바뀌어 버려 셋업 타임 동안 데이터가 안정된 상태로 도착하지 못함을 나타내었다. 홀드 타임이 위배된 경우 DATA_B 가 클럭엣지 이후에 홀드 타임만큼 안정한 상태로 유지되지 못하고 중간에 DATA_C로 바뀌어 버린 것을 나타내었다.

또한, 셋업 타임과 홀드 타임이 모두 지켜진 경우는 그림 1에서 셋업 타임과 홀드 타임이 모두 만족한 부분을 통해 알 수 있듯이 DATA_B가 클럭엣지 기준 셋업 타임보다 이전에 데이터가 도착했고, 클럭엣지 기준 홀드 타임보다 더 데이터가 유지되어 클럭 주파수에 데이터를 올바르게 이동시킬 수 있는 상태가 되었다. 즉, 모든 데이터는 두 가지 타이밍 조건에 만족해야 설계된 의도대로 회로가 동작할 수 있다.

회로에서 타이밍 을 계산하는 방법

매우 복잡한 회로와 매우 많은 양의 회로를 올바르게 동작시키기 위해 타이밍 조건을 만족시키려면 셋업 타임과 홀드 타임 이 모두 만족하였는지 계산해야 한다. [7] STA(Static Timing Analysis)라고 불리는 기법을 통해 설계된 회로들이 의도된 동작을 할 수 있도록 타이밍 요구사항들이 충족하는지 확인할 수 있다. 즉 신호가 늦게 도착해서 의도하지 않은 동작을 하거나, 신호가 너무 빨리 와서 의도하지 않은 동작을 하지 않도록 분석하는 기법이다.

.jpg)

그림 2을 통해 알 수 있듯이 Launch CLK (데이터의 이동이 시작된 시점)으로부터 Capture CLK(다음 클럭엣지)의 셋업 타임만큼 일찍 데이터가 도착하도록 확인하고, 동일하게 Launch CLK로부터 홀드 타임만큼 데이터가 안정된 상태로 유지되는지 확인하도록 하면 된다.

즉, (1) 구간에 DATA_A가 홀드 타임만큼 유지되고 DATA_A의 다음 데이터인 DATA_B가 Capture CLK - 셋업타임 만큼 데이터가 일찍 도착한 경우 타이밍 조건을 모두 만족한다. 타이밍 규칙 위반의 경우를 살펴보자면 (1)구간에서 DATA_A는 홀드 타임만큼 유지되었으나, DATA_B가 Capture CLK - 셋업타임 만큼 데이터가 일찍 도착하지 못해 셋업 타임 규칙이 위반되었다. (2)구간의 경우 DATA_C는 Capture CLK보다 일찍 도착했으나, 이전 데이터인 DATA_B가 홀드 타임만큼 유지되지 못해 홀드 타임 규칙이 위반되었다.

위 개념을 통해 수식적으로 접근하여 타이밍을 분석할 수 있다.

.jpg)

그림 3을 통해 알 수 있듯이 Tck1 + Tck-q + Tcomb < Tck2 + clock 1 period - setup time이 만족하지 않는 경우 셋업 타임 규칙이 위반되었다고 판단할 수 있다.

.jpg)

그림 4를 통해 알 수 있듯이 Tck1 + Tck-q + Tcomb > Tck2 + hold time이 만족하지 않는 경우 홀드 타임 규칙이 위반되었다고 판단할 수 있다.

이러한 알고리즘을 기반으로 타이밍을 분석하여 회로 전체의 타이밍을 만족시켜야 한다.

3. 회로에서 타이밍을 보정하는 방법

만약 타이밍 분석 알고리즘을 기반으로 분석된 회로 중 셋업 타임과 홀드 타임이 위반된 회로들이 있다면, 타이밍 조건이 만족하도록 보정해야 한다. 기본적으로 딜레이(delay) 관점에서 보정하는 방법에 접근해야 하며, 딜레이를 증가시킬 방법과 딜레이를 감소시킬 방법을 이해하고 적절히 사용해야 한다.

기본적으로 딜레이는 저항과 커패시턴스에 비례한다. 저항과 커패시턴스가 커지면 딜레이는 늘어나고 저항과 커패시턴스가 작아지면 딜레이는 작아진다[2].

3-1. 셀 크기 조정

셀 크기를 더 크게 만들거나 작게 만들어서 딜레이를 조정할 수 있다. 셀을 크게 만드는 경우 셀 내부 트랜지스터의 크기가 커진다고 해석할 수 있고, 이는 W?L 중 Width가 커져서 트랜지스터의 전류 공식에 따라 더 많은 전류를 흐를 수 있게 한다는 의미이다.

즉, 해당 트랜지스터의 Drive Strength를 증가시킨다고 해석할 수 있다. 따라서 Drive strength가 커짐에 따라 빠른 시간에 커패시터에 전류를 충전할 수 있어서 딜레이가 작아질 수 있다. 하지만, Drive strength를 키운다고 해도 항상 딜레이가 감소하지는 않는다. 큰 Load 커패시턴스를 충분히 충전할 정도의 크기가 되면 더 이상 커져도 딜레이가 줄지 않는다. 이러한 현상을 self-loading 현상이라고 부른다.

즉, 타이밍을 보정하기 위해서는 크기를 변경할 셀의 딜레이가 줄어들 수 있는 상황인지 파악한 후 보정해야 한다. 같은 맥락으로 load 커패시턴스가 매우 큰 경우 크기를 작게 만들게 되면 Drive strength가 작아지고 이에 따라 load 커패시턴스를 충전할 능력이 부족해지기 때문에 전체적인 딜레이가 커질 수 있다. 하지만 load 커패시턴스가 작은 경우 셀 크기를 작게 만들면 셀 자체의 내부 커패시턴스 값이 줄어들어 딜레이가 작아질 수도 있다. 즉, 셀의 크기 조정을 통해 딜레이를 조정하는 경우에는 여러 상황을 고려해서 적합한 셀의 크기를 찾아 조정해야 한다.

3-2 셀 문턱전압 조정

셀의 문턱전압을 높게 만들거나 낮게 만들어서 딜레이를 조정할 수 있다. 더 낮은 수준의 전압으로 트랜지스터를 켜고 끌 수 있다는 내용만으로도 딜레이의 차이가 존재한다는 것을 추측할 수 있지만, 문턱전압과 전류의 연관성이 존재하는 트랜지스터의 전류 공식에서 확인할 수 있다.

위 수식을 통해 알 수 있듯이, 문턱전압을 높은 것으로 바꾸면 전류의 크기가 작아지므로 딜레이가 커지게 되고 문턱전압을 낮은 것으로 바꾸면 전류의 크기가 커지므로 딜레이가 작아진다고 해석할 수 있다.

위 내용에 근거하여 문턱전압 수준에 따라 4가지 종류로 분류하고 있다. HVT (High Voltage Treshold), RVT (Regular Voltage Treshold), LVT (Low Voltage Treshold), SLVT (Super Low Voltage Treshold). 문턱전압이 낮을수록 딜레이가 빨라지지만, 낮은 전압으로 쉽게 트랜지스터를 스위칭할 수 있다는 점은, 낮은 전압 에서부터 누설전류가 발생한다고도 해석할 수 있다. 따라서 전력 관점에서 SLVT 와 같은 낮은 문턱전압에 동작하는 셀을 사용하는 것이 문제없는지 검토해야 한다.

3-3 셀 삽입/삭제

셀을 넣거나 뺌으로써 딜레이를 조정할 수 있다. 불필요하게 삽입되어 있는 셀을 지우면 해당 셀로 인해 존재했던 커패시턴스와 저항 같은 전류의 이동을 방해하는 요소들이 사라져 딜레이가 감소하게 된다. 하지만, 긴 거리를 이동하는 경우 셀을 삭제할수록 셀 간에 연결된 wire의 길이가 매우 길어지게 된다.

긴 거리의 신호 전송 시 긴 wire가 형성되고 이는 물리적으로 메탈 길이(Metal Length)가 길어지게 된다. 메탈 길이가 길어지면 긴 메탈에 존재하는 커패시턴스가 많아지므로 동일한 Drive strength 대비 충전시켜야 할 커패시턴스 용량이 커져서 충·방전 속도가 느려진다. 이는 신호가 전환하는 데 시간이 오래 걸린다는 것을 의미한다. 즉, 딜레이는 오히려 증가하게 된다.

반대로 긴 거리의 신호를 전송하는데 셀을 중간 위치에 추가로 넣는다면 동일한 Drive Strength로 이동해야할 거리가 짧아진다. 즉, 동일한 Drive Strength로 충전해야 할 커패시턴스의 수가 작아지는 것을 의미하기도 한다. 따라서 긴 거리의 데이터를 이동하는데 셀을 추가로 넣어 짧은 거리의 데이터 이동을 만들어낸다면 딜레이를 줄일 수 있다.

3-4 메탈 조정

Layout 상에서 메탈의 width, spacing, layer 등을 조정하거나 강제로 우회(Detour)시킴으로써 딜레이를 조정할 수 있다. 서로 다른 회로를 연결할 때 interconnect 되는 부분을 wire라고 하고 전기가 흐를 수 있는 메탈을 통해 연결된다. 셀 내부에 트랜지스터가 가지고 있는 커패시턴스와 저항을 통해 딜레이를 계산하지만, 셀 간 연결되는 메탈의 커패시턴스와 저항 또한 딜레이를 계산하는데 큰 부분을 차지한다.

일반적으로 전기저항 R은 길이에 비례하고 단면적과 반비례한 관계가 (R=ρ L/A) 있다. 즉, 메탈 Width가 커지면 저항은 작아지며 저항과 반비례한 전류는 커지기 때문에 딜레이는 작아진다. 즉, 셋업 타임 관점에서 딜레이를 줄이기 위해서 메탈 width를 크게 만드는 것은 딜레이를 줄이는 데 도움이 될 수 있다.

또한, 두 개의 메탈 간 너무 가까이 붙어있으면 불필요한 신호 간섭으로 인해 의도하지 않은 회로의 오작동을 유발할 수 있다. 이처럼 메탈 간 적절한 간격을 유지하는 것이 불필요한 신호 간섭을 방지할 수 있기 때문에 중요하다. 전류가 흐르는 과정에서 Coupling Capacitance 가 형성되고, 크로스토크(Cross-Talk) 및 노이즈 (Noise)와 같은 불필요한 신호 간섭이 생길 수 있다 [8].

이러한 문제들은 딜레이에 어떤 방향으로 영향을 줄지 예측할 수 없어서 동일한 wire에 대해 딜레이 계산 시 maximum 딜레이 분석 시에는 딜레이가 증가하고, minimum 딜레이 분석 시에는 딜레이가 감소하여 셋업 타임과 홀드 타임이 모두 취약해진다. 따라서 특정 Wire에 크로스토크 및 노이즈 현상으로 인한 불필요한 간섭을 줄여야하는 경우에 메탈 간 거리를 적정거리 이상 떨어뜨리는 것이 셋업 타임과 홀드 타임 모두를 개선할 수 있다. [4].

Detour는 사전적 정의로 우회하다, 라는 뜻을 가지고 있다. 즉, 우리는 출발지와 도착지 사이의 길을 우회시켜 너무 일찍 도착하지 않도록 만들 수 있다. 앞서 설명한 바와 같이 저항은 L 길이와 비례하기 때문에 짧은 거리를 연결해 두었던 메탈을 우회시켜 메탈 길이가 길어지면 저항이 커짐에 따라 딜레이는 증가한다.

보통 반도체 칩을 구현하는 과정에서 타이밍 보정 작업이 모두 완료되고 Physical Verification까지 완료되면 GDS(Graphic Design System)라고 하는 데이터를 파운드리에 전달해 FEOL(Front-End of Layer) 마스크를 제작하게 된다. 그리고 파운드리에서 FEOL 마스크를 제작하는 도중에 홀드 타임 규칙 위반이 발견되면, 이때 메탈만을 조정하여 딜레이를 추가로 만들어내 보정할 수 있다. 이러한 방법은 FEOL 마스크용 GDS 데이터를 변경하지 않고, 메탈만 수정하여 만든 딜레이이기 때문에 FEOL 마스크를 다시 제작해야하는 일을 방지할 수 있다.

공정별로 메탈 Layer의 특성이 모두 다르지만, Top Down 구조의 경우 기본적으로 전류가 칩 내에서 위에서 아래로 전파되기 때문에, 하위 Layer까지 전류가 이동하기 위해서는 수많은 메탈 Layer와 Via를 지나가야 한다. 따라서 하위 Layer까지 이동하는 경로가 상위 Layer보다 저항과 커패시턴스가 크기 때문에 딜레이 측면에서는 더 커질 수밖에 없다. 따라서 필요시 상위 Layer를 통해 셀 간 연결하면 딜레이를 감소시킬 수 있고 반대로 하위 Layer를 통해 셀 간 연결하면 딜레이를 증가시킬 수 있다.

3-5 셀 복제

Layout 친화적이지 않은 설계 탓에 타이밍 문제가 발생하는 경우, 동일한 기능을 하는 설계를 유지하되 셀을 복제하여 딜레이를 조정할 수 있다. Cloning이라고 부르는 셀 복제 기법은 여러 가지 조건에 부합하는 특정 상황에 사용할 수 있는 방법이다.

일반적으로 디지털 회로를 설계하는 설계자는 설계의 다양한 요소를 최적화하고 회로의 성능을 향상하기 위해 플립플롭과 로드(load)될 데이터를 동일한 논리요소를 기반으로 분리할 필요가 있다. 그림 5을 통해 알 수 있듯이 플립플롭은 3가지로 종류로 구분되어 있지만, 플립플롭에 Drive 되는 데이터는 동일한 논리요소를 기반으로 분리되어 있지 않다. 이 경우 상위에 존재하는 플립플롭의 경우 불필요하게 긴 딜레이를 가질 수 있기 때문에 복제를 통해 병목현상을 완화할 수 있다.

위 방법은 Boolean function을 가지고 있는 논리게이트의 연결 정보가 달라졌기 때문에, 동일한 기능을 유지한 상태에서 조정되었는지 꼭 확인해야 한다. 또한, 물리적으로 구현 가능한지 확인이 필요하다. 단순 조합논리 회로를 복제한다면 입력과 출력의 연결만 디자인 룰에 위배되지 않게 구현하면 되지만, 클럭 게이팅 셀이나 플립플롭을 복제하는 경우 ‘data network’ 뿐 아니라 ‘clock network’도 새로 구현해야 하므로 물리적으로 Layout에 구현 가능한지 검토가 선제적이다. 위와 같은 방법으로 병목현상을 개선한다면, 불필요하게 긴 시간이 소요되었던 플립플롭에 대해서 딜레이를 줄일 수 있다.

.jpg)

결론

점점 복잡한 방식으로 반도체가 설계되고, 고스펙의 반도체 칩을 제작해야만 경쟁력이 있는 시대가 찾아왔다. 빠른 연산속도를 가졌으며, 전력효율이 높고, 작은 면적을 차지하도록 최고 성능의 반도체를 설계했다고 하여도, 구현 과정에서 타이밍 조건들이 모두 성립되지 않으면 실제로 ‘fab out’된 반도체 칩은 설계된 회로 동작대로 동작하지 않는다.

또한 보이지 않는, 공정상에서 불확실성 혹은 반도체 칩의 여러 가지 변수들을 합리적으로 수치화하여 타이밍을 분석해야만 신뢰성 있는 반도체를 만들어낼 수 있다.[1][3][6].

즉, 타이밍 보정 방법들을 통해 빠른 주파수에서 동작하는 반도체 칩을 구현하는 기술은 미래지향적인 분야라고 생각한다. 이러한 타이밍 분석 및 보정 기술이 발전하게 된다면 스펙에 맞는 칩을 구현해내는 시간이 짧아질 수 있고 이는 반도체 칩의 가격을 낮추는 데 일조하게 된다. 이는 곧 최고 성능의 반도체 칩이 탑재된 전자제품들을 싸게 소비자가 구매하게 되는 날이 올 것이라고 기대된다.

참고 문헌

[1] Chang, K.-J. (2004). Accurate on-chip variation modeling to achieve design for manufacturability. 4th IEEE International Workshop on System-on-Chip for Real-Time Applications, IEEE.

[2] Cong, J. J. and K.-S. Leung (1995). "Optimal wiresizing under Elmore delay model." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 14(3): 321-336.

[3] Harkness, C. L. (1991). An approach to uncertainty in VLSI design, Brown University.

[4] Kumar, A., et al. (2007). An ECO technique for removing crosstalk violations in clock networks. 20th International Conference on VLSI Design held jointly with 6th International Conference on Embedded Systems (VLSID'07), IEEE.

[5] Ramanathan, P., et al. (1994). "Clock distribution in general VLSI circuits." IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications 41(5): 395-404.

[6] Zejda, J. and P. Frain (2002). General framework for removal of clock network pessimism. Proceedings of the 2002 IEEE/ACM international conference on Computer-aided design.

[7] page, S. w. "What is Static Timing Analysis (STA)?". Retrieved 2024.01.03, from https://www.synopsys.com/glossary/what-is-static-timing-analysis.html.

[8] Franzini, B., et al. (2000). Crosstalk aware static timing analysis: a two step approach. Proceedings IEEE 2000 First International Symposium on Quality Electronic Design (Cat. No. PR00525), IEEE.

[9] Balef, H. A., et al. (2017). An analytical model for interdependent setup/hold-time characterization of flip-flops. 2017 18th International Symposium on Quality Electronic Design (ISQED), IEEE.

AI를 활용한 솔루션이 발전하면서 대용량 연산이 가능한 NPU(Neural Processing Unit)가 등장했다. 경쟁력 있는 NPU를 개발하기 위해서는 많은 양의 연산을 빠른 시간에 수행해야 한다. 즉, 매우 빠른 주파수를 기반으로 하고 효율적인 전력 사용에 초점을 맞춘 고사양 NPU를 개발해야 한다. 따라서 고사양 NPU에서 데이터가 정상적으로 이동하기 위해서는 빠른 속도의 주파수로 인해 더 어려워진 셋업 타임(setup time rule) 과 홀드 타임 (hold time rule)을 효율적으로 만족시키는 방법이 중요해졌다. 빠른 속도의 주파수로 동작하기 위한 타이밍 규칙에 위배되지 않도록 조정하는 방법들과 그에 따른 효율적인 방법론을 알아보자.

.jpg)

글/ 고려대학교 주병권 교수님 연구실

주병권 (고려대학교 전기전자공학부 교수)

홍재원 (고려대학교 전기전자컴퓨터 공학부 석사 과정)

목 차

1. 회로에서 타이밍 이란?

1-1 셋업타임 과 홀드타임

2. 회로에서 타이밍을 계산하는 방법

3. 회로에서 타이밍을 보정하는 방법

3-1 셀 크기 조정

3-2 셀 문턱전압 조정

3-3 셀 삽입 / 삭제

3-4 메탈 조정

3-5 셀 복제

4. 결론

5. 참고 문헌

1. 회로에서 타이밍 이란?

반도체 회로에서의 타이밍을 이해하기 위해서는 클럭(clock)의 개념이 선제되어야 한다. 클럭 은 회로의 상태가 연속적으로 진행되는데 사용되는 반복적인 파형(wave)이라고 해석할 수 있다. 타이밍은 클럭의 주기(period) 안에 데이터를 올바르게 이동시킬 수 있는 규칙을 의미한다[5]. 대표적인 두 가지 규칙이 셋업 타임과 홀드 타임이다.

1-1. 셋업타임 과 홀드타임

[9] 셋업 타임이란, 동기 신호의 데이터는 반드시 클럭엣지 이전에 안정한 상태로 도착해야 하는 시간이라 정의한다. 홀드 타임이란, 동기 신호의 데이터는 반드시 클럭엣지 이후에 안정한 상태로 유지되어야 하는 시간이라 정의한다.

.jpg)

그림 1. 타이밍 규칙 위반의 예시

그림 1을 통해 알 수 있듯이 셋업 타임이 위배된 경우 DATA_B 가 클럭엣지에서 셋업 타임 보다 이전에 들어오지 못하고 DATA_A가 들어온 이후 DATA_B로 바뀌어 버려 셋업 타임 동안 데이터가 안정된 상태로 도착하지 못함을 나타내었다. 홀드 타임이 위배된 경우 DATA_B 가 클럭엣지 이후에 홀드 타임만큼 안정한 상태로 유지되지 못하고 중간에 DATA_C로 바뀌어 버린 것을 나타내었다.

또한, 셋업 타임과 홀드 타임이 모두 지켜진 경우는 그림 1에서 셋업 타임과 홀드 타임이 모두 만족한 부분을 통해 알 수 있듯이 DATA_B가 클럭엣지 기준 셋업 타임보다 이전에 데이터가 도착했고, 클럭엣지 기준 홀드 타임보다 더 데이터가 유지되어 클럭 주파수에 데이터를 올바르게 이동시킬 수 있는 상태가 되었다. 즉, 모든 데이터는 두 가지 타이밍 조건에 만족해야 설계된 의도대로 회로가 동작할 수 있다.

회로에서 타이밍 을 계산하는 방법

매우 복잡한 회로와 매우 많은 양의 회로를 올바르게 동작시키기 위해 타이밍 조건을 만족시키려면 셋업 타임과 홀드 타임 이 모두 만족하였는지 계산해야 한다. [7] STA(Static Timing Analysis)라고 불리는 기법을 통해 설계된 회로들이 의도된 동작을 할 수 있도록 타이밍 요구사항들이 충족하는지 확인할 수 있다. 즉 신호가 늦게 도착해서 의도하지 않은 동작을 하거나, 신호가 너무 빨리 와서 의도하지 않은 동작을 하지 않도록 분석하는 기법이다.

.jpg)

그림 2. 타이밍 규칙 위반 확인 방법의 예시

그림 2을 통해 알 수 있듯이 Launch CLK (데이터의 이동이 시작된 시점)으로부터 Capture CLK(다음 클럭엣지)의 셋업 타임만큼 일찍 데이터가 도착하도록 확인하고, 동일하게 Launch CLK로부터 홀드 타임만큼 데이터가 안정된 상태로 유지되는지 확인하도록 하면 된다.

즉, (1) 구간에 DATA_A가 홀드 타임만큼 유지되고 DATA_A의 다음 데이터인 DATA_B가 Capture CLK - 셋업타임 만큼 데이터가 일찍 도착한 경우 타이밍 조건을 모두 만족한다. 타이밍 규칙 위반의 경우를 살펴보자면 (1)구간에서 DATA_A는 홀드 타임만큼 유지되었으나, DATA_B가 Capture CLK - 셋업타임 만큼 데이터가 일찍 도착하지 못해 셋업 타임 규칙이 위반되었다. (2)구간의 경우 DATA_C는 Capture CLK보다 일찍 도착했으나, 이전 데이터인 DATA_B가 홀드 타임만큼 유지되지 못해 홀드 타임 규칙이 위반되었다.

위 개념을 통해 수식적으로 접근하여 타이밍을 분석할 수 있다.

.jpg)

그림 3. 셋업 타임 규칙이 위반되었는지 확인하는 수식

그림 3을 통해 알 수 있듯이 Tck1 + Tck-q + Tcomb < Tck2 + clock 1 period - setup time이 만족하지 않는 경우 셋업 타임 규칙이 위반되었다고 판단할 수 있다.

.jpg)

그림 4. 홀드 타임 규칙이 위반되었는지 확인하는 수식

그림 4를 통해 알 수 있듯이 Tck1 + Tck-q + Tcomb > Tck2 + hold time이 만족하지 않는 경우 홀드 타임 규칙이 위반되었다고 판단할 수 있다.

이러한 알고리즘을 기반으로 타이밍을 분석하여 회로 전체의 타이밍을 만족시켜야 한다.

3. 회로에서 타이밍을 보정하는 방법

만약 타이밍 분석 알고리즘을 기반으로 분석된 회로 중 셋업 타임과 홀드 타임이 위반된 회로들이 있다면, 타이밍 조건이 만족하도록 보정해야 한다. 기본적으로 딜레이(delay) 관점에서 보정하는 방법에 접근해야 하며, 딜레이를 증가시킬 방법과 딜레이를 감소시킬 방법을 이해하고 적절히 사용해야 한다.

기본적으로 딜레이는 저항과 커패시턴스에 비례한다. 저항과 커패시턴스가 커지면 딜레이는 늘어나고 저항과 커패시턴스가 작아지면 딜레이는 작아진다[2].

3-1. 셀 크기 조정

셀 크기를 더 크게 만들거나 작게 만들어서 딜레이를 조정할 수 있다. 셀을 크게 만드는 경우 셀 내부 트랜지스터의 크기가 커진다고 해석할 수 있고, 이는 W?L 중 Width가 커져서 트랜지스터의 전류 공식에 따라 더 많은 전류를 흐를 수 있게 한다는 의미이다.

즉, 해당 트랜지스터의 Drive Strength를 증가시킨다고 해석할 수 있다. 따라서 Drive strength가 커짐에 따라 빠른 시간에 커패시터에 전류를 충전할 수 있어서 딜레이가 작아질 수 있다. 하지만, Drive strength를 키운다고 해도 항상 딜레이가 감소하지는 않는다. 큰 Load 커패시턴스를 충분히 충전할 정도의 크기가 되면 더 이상 커져도 딜레이가 줄지 않는다. 이러한 현상을 self-loading 현상이라고 부른다.

즉, 타이밍을 보정하기 위해서는 크기를 변경할 셀의 딜레이가 줄어들 수 있는 상황인지 파악한 후 보정해야 한다. 같은 맥락으로 load 커패시턴스가 매우 큰 경우 크기를 작게 만들게 되면 Drive strength가 작아지고 이에 따라 load 커패시턴스를 충전할 능력이 부족해지기 때문에 전체적인 딜레이가 커질 수 있다. 하지만 load 커패시턴스가 작은 경우 셀 크기를 작게 만들면 셀 자체의 내부 커패시턴스 값이 줄어들어 딜레이가 작아질 수도 있다. 즉, 셀의 크기 조정을 통해 딜레이를 조정하는 경우에는 여러 상황을 고려해서 적합한 셀의 크기를 찾아 조정해야 한다.

3-2 셀 문턱전압 조정

셀의 문턱전압을 높게 만들거나 낮게 만들어서 딜레이를 조정할 수 있다. 더 낮은 수준의 전압으로 트랜지스터를 켜고 끌 수 있다는 내용만으로도 딜레이의 차이가 존재한다는 것을 추측할 수 있지만, 문턱전압과 전류의 연관성이 존재하는 트랜지스터의 전류 공식에서 확인할 수 있다.

위 수식을 통해 알 수 있듯이, 문턱전압을 높은 것으로 바꾸면 전류의 크기가 작아지므로 딜레이가 커지게 되고 문턱전압을 낮은 것으로 바꾸면 전류의 크기가 커지므로 딜레이가 작아진다고 해석할 수 있다.

위 내용에 근거하여 문턱전압 수준에 따라 4가지 종류로 분류하고 있다. HVT (High Voltage Treshold), RVT (Regular Voltage Treshold), LVT (Low Voltage Treshold), SLVT (Super Low Voltage Treshold). 문턱전압이 낮을수록 딜레이가 빨라지지만, 낮은 전압으로 쉽게 트랜지스터를 스위칭할 수 있다는 점은, 낮은 전압 에서부터 누설전류가 발생한다고도 해석할 수 있다. 따라서 전력 관점에서 SLVT 와 같은 낮은 문턱전압에 동작하는 셀을 사용하는 것이 문제없는지 검토해야 한다.

3-3 셀 삽입/삭제

셀을 넣거나 뺌으로써 딜레이를 조정할 수 있다. 불필요하게 삽입되어 있는 셀을 지우면 해당 셀로 인해 존재했던 커패시턴스와 저항 같은 전류의 이동을 방해하는 요소들이 사라져 딜레이가 감소하게 된다. 하지만, 긴 거리를 이동하는 경우 셀을 삭제할수록 셀 간에 연결된 wire의 길이가 매우 길어지게 된다.

긴 거리의 신호 전송 시 긴 wire가 형성되고 이는 물리적으로 메탈 길이(Metal Length)가 길어지게 된다. 메탈 길이가 길어지면 긴 메탈에 존재하는 커패시턴스가 많아지므로 동일한 Drive strength 대비 충전시켜야 할 커패시턴스 용량이 커져서 충·방전 속도가 느려진다. 이는 신호가 전환하는 데 시간이 오래 걸린다는 것을 의미한다. 즉, 딜레이는 오히려 증가하게 된다.

반대로 긴 거리의 신호를 전송하는데 셀을 중간 위치에 추가로 넣는다면 동일한 Drive Strength로 이동해야할 거리가 짧아진다. 즉, 동일한 Drive Strength로 충전해야 할 커패시턴스의 수가 작아지는 것을 의미하기도 한다. 따라서 긴 거리의 데이터를 이동하는데 셀을 추가로 넣어 짧은 거리의 데이터 이동을 만들어낸다면 딜레이를 줄일 수 있다.

3-4 메탈 조정

Layout 상에서 메탈의 width, spacing, layer 등을 조정하거나 강제로 우회(Detour)시킴으로써 딜레이를 조정할 수 있다. 서로 다른 회로를 연결할 때 interconnect 되는 부분을 wire라고 하고 전기가 흐를 수 있는 메탈을 통해 연결된다. 셀 내부에 트랜지스터가 가지고 있는 커패시턴스와 저항을 통해 딜레이를 계산하지만, 셀 간 연결되는 메탈의 커패시턴스와 저항 또한 딜레이를 계산하는데 큰 부분을 차지한다.

일반적으로 전기저항 R은 길이에 비례하고 단면적과 반비례한 관계가 (R=ρ L/A) 있다. 즉, 메탈 Width가 커지면 저항은 작아지며 저항과 반비례한 전류는 커지기 때문에 딜레이는 작아진다. 즉, 셋업 타임 관점에서 딜레이를 줄이기 위해서 메탈 width를 크게 만드는 것은 딜레이를 줄이는 데 도움이 될 수 있다.

또한, 두 개의 메탈 간 너무 가까이 붙어있으면 불필요한 신호 간섭으로 인해 의도하지 않은 회로의 오작동을 유발할 수 있다. 이처럼 메탈 간 적절한 간격을 유지하는 것이 불필요한 신호 간섭을 방지할 수 있기 때문에 중요하다. 전류가 흐르는 과정에서 Coupling Capacitance 가 형성되고, 크로스토크(Cross-Talk) 및 노이즈 (Noise)와 같은 불필요한 신호 간섭이 생길 수 있다 [8].

이러한 문제들은 딜레이에 어떤 방향으로 영향을 줄지 예측할 수 없어서 동일한 wire에 대해 딜레이 계산 시 maximum 딜레이 분석 시에는 딜레이가 증가하고, minimum 딜레이 분석 시에는 딜레이가 감소하여 셋업 타임과 홀드 타임이 모두 취약해진다. 따라서 특정 Wire에 크로스토크 및 노이즈 현상으로 인한 불필요한 간섭을 줄여야하는 경우에 메탈 간 거리를 적정거리 이상 떨어뜨리는 것이 셋업 타임과 홀드 타임 모두를 개선할 수 있다. [4].

Detour는 사전적 정의로 우회하다, 라는 뜻을 가지고 있다. 즉, 우리는 출발지와 도착지 사이의 길을 우회시켜 너무 일찍 도착하지 않도록 만들 수 있다. 앞서 설명한 바와 같이 저항은 L 길이와 비례하기 때문에 짧은 거리를 연결해 두었던 메탈을 우회시켜 메탈 길이가 길어지면 저항이 커짐에 따라 딜레이는 증가한다.

보통 반도체 칩을 구현하는 과정에서 타이밍 보정 작업이 모두 완료되고 Physical Verification까지 완료되면 GDS(Graphic Design System)라고 하는 데이터를 파운드리에 전달해 FEOL(Front-End of Layer) 마스크를 제작하게 된다. 그리고 파운드리에서 FEOL 마스크를 제작하는 도중에 홀드 타임 규칙 위반이 발견되면, 이때 메탈만을 조정하여 딜레이를 추가로 만들어내 보정할 수 있다. 이러한 방법은 FEOL 마스크용 GDS 데이터를 변경하지 않고, 메탈만 수정하여 만든 딜레이이기 때문에 FEOL 마스크를 다시 제작해야하는 일을 방지할 수 있다.

공정별로 메탈 Layer의 특성이 모두 다르지만, Top Down 구조의 경우 기본적으로 전류가 칩 내에서 위에서 아래로 전파되기 때문에, 하위 Layer까지 전류가 이동하기 위해서는 수많은 메탈 Layer와 Via를 지나가야 한다. 따라서 하위 Layer까지 이동하는 경로가 상위 Layer보다 저항과 커패시턴스가 크기 때문에 딜레이 측면에서는 더 커질 수밖에 없다. 따라서 필요시 상위 Layer를 통해 셀 간 연결하면 딜레이를 감소시킬 수 있고 반대로 하위 Layer를 통해 셀 간 연결하면 딜레이를 증가시킬 수 있다.

3-5 셀 복제

Layout 친화적이지 않은 설계 탓에 타이밍 문제가 발생하는 경우, 동일한 기능을 하는 설계를 유지하되 셀을 복제하여 딜레이를 조정할 수 있다. Cloning이라고 부르는 셀 복제 기법은 여러 가지 조건에 부합하는 특정 상황에 사용할 수 있는 방법이다.

일반적으로 디지털 회로를 설계하는 설계자는 설계의 다양한 요소를 최적화하고 회로의 성능을 향상하기 위해 플립플롭과 로드(load)될 데이터를 동일한 논리요소를 기반으로 분리할 필요가 있다. 그림 5을 통해 알 수 있듯이 플립플롭은 3가지로 종류로 구분되어 있지만, 플립플롭에 Drive 되는 데이터는 동일한 논리요소를 기반으로 분리되어 있지 않다. 이 경우 상위에 존재하는 플립플롭의 경우 불필요하게 긴 딜레이를 가질 수 있기 때문에 복제를 통해 병목현상을 완화할 수 있다.

위 방법은 Boolean function을 가지고 있는 논리게이트의 연결 정보가 달라졌기 때문에, 동일한 기능을 유지한 상태에서 조정되었는지 꼭 확인해야 한다. 또한, 물리적으로 구현 가능한지 확인이 필요하다. 단순 조합논리 회로를 복제한다면 입력과 출력의 연결만 디자인 룰에 위배되지 않게 구현하면 되지만, 클럭 게이팅 셀이나 플립플롭을 복제하는 경우 ‘data network’ 뿐 아니라 ‘clock network’도 새로 구현해야 하므로 물리적으로 Layout에 구현 가능한지 검토가 선제적이다. 위와 같은 방법으로 병목현상을 개선한다면, 불필요하게 긴 시간이 소요되었던 플립플롭에 대해서 딜레이를 줄일 수 있다.

.jpg)

그림 5. De-clone 과 clone 이후 예시

결론

점점 복잡한 방식으로 반도체가 설계되고, 고스펙의 반도체 칩을 제작해야만 경쟁력이 있는 시대가 찾아왔다. 빠른 연산속도를 가졌으며, 전력효율이 높고, 작은 면적을 차지하도록 최고 성능의 반도체를 설계했다고 하여도, 구현 과정에서 타이밍 조건들이 모두 성립되지 않으면 실제로 ‘fab out’된 반도체 칩은 설계된 회로 동작대로 동작하지 않는다.

또한 보이지 않는, 공정상에서 불확실성 혹은 반도체 칩의 여러 가지 변수들을 합리적으로 수치화하여 타이밍을 분석해야만 신뢰성 있는 반도체를 만들어낼 수 있다.[1][3][6].

즉, 타이밍 보정 방법들을 통해 빠른 주파수에서 동작하는 반도체 칩을 구현하는 기술은 미래지향적인 분야라고 생각한다. 이러한 타이밍 분석 및 보정 기술이 발전하게 된다면 스펙에 맞는 칩을 구현해내는 시간이 짧아질 수 있고 이는 반도체 칩의 가격을 낮추는 데 일조하게 된다. 이는 곧 최고 성능의 반도체 칩이 탑재된 전자제품들을 싸게 소비자가 구매하게 되는 날이 올 것이라고 기대된다.

참고 문헌

[1] Chang, K.-J. (2004). Accurate on-chip variation modeling to achieve design for manufacturability. 4th IEEE International Workshop on System-on-Chip for Real-Time Applications, IEEE.

[2] Cong, J. J. and K.-S. Leung (1995). "Optimal wiresizing under Elmore delay model." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 14(3): 321-336.

[3] Harkness, C. L. (1991). An approach to uncertainty in VLSI design, Brown University.

[4] Kumar, A., et al. (2007). An ECO technique for removing crosstalk violations in clock networks. 20th International Conference on VLSI Design held jointly with 6th International Conference on Embedded Systems (VLSID'07), IEEE.

[5] Ramanathan, P., et al. (1994). "Clock distribution in general VLSI circuits." IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications 41(5): 395-404.

[6] Zejda, J. and P. Frain (2002). General framework for removal of clock network pessimism. Proceedings of the 2002 IEEE/ACM international conference on Computer-aided design.

[7] page, S. w. "What is Static Timing Analysis (STA)?". Retrieved 2024.01.03, from https://www.synopsys.com/glossary/what-is-static-timing-analysis.html.

[8] Franzini, B., et al. (2000). Crosstalk aware static timing analysis: a two step approach. Proceedings IEEE 2000 First International Symposium on Quality Electronic Design (Cat. No. PR00525), IEEE.

[9] Balef, H. A., et al. (2017). An analytical model for interdependent setup/hold-time characterization of flip-flops. 2017 18th International Symposium on Quality Electronic Design (ISQED), IEEE.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

본 기사의 전문은 PDF문서로 제공합니다.

(로그인필요)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

100자평 쓰기