조셉 유(Joseph Yiu), 시니어 임베디드 테크놀로지 매니저, ARM

본지 5월호에 이어 ARM Cortex-M 입문자를 위한 ‘ARM Cortex-M 입문자용 백서’ 시리즈를 소개한다. 참고로, 3회에서 2회로 변경되어 이번 호를 끝으로 시리즈를 완결한다.

4. 시스템 기능 및 특징

4.1 저전력 지원 기능

저전력은 Cortex-M 프로세서의 주요 장점 중 하나다. 저전력 지원 기능은 아키텍처에 내장되어 있다.

· WFI 및 WFE 명령어

· 아키텍처상 수면 모드(Sleep Mode) 정의 이 외에도 Cortex-M 프로세서에서 제공하는 여러가지 저전력 기능이 있다.

· 휴면(Sleep) 및 딥 슬립 모드(Deep Sleep Modes): 아키텍처에서 지원하며 특정 디바이스의 전력 제어 레지스터를 활용해 더 확장될 수 있다.

· 슬립 온 엑시트(Sleep-On-Exit): 인터럽트(Interrupt) 구동 방식의 애플리케이션에서 저전력 기능을 활성화한다. 이를 통해 예외 처리를 끝낸 후 처리할 예외 사항이 없다면 프로세서는 휴면 상태로 자동 전환된다. 이 기능은 Cortex-M 프로세서가 쓰레드(Thread) 모드에서의 추가 코드 실행을 위한 활성 상태에 있는 시간을 없애 전력을 절약하고 불필요한 스택 연산을 줄인다.

· WIC(Wake-up Interrupt Controller): 일정 수준의 저전력 상태에서 프로세서 외부의 소형 블록이 인터럽트 감지 기능을 수행하도록 하는 옵션 기능이다(예. SRPG(State Retention Power Gating) 설계에서 프로세서 전원이 꺼진 경우).

· 클록 게이팅(Clock Gating) 및 아키텍처상 클록 게이팅: 레지스터 클록이나 프로세서 서브 모듈 클록을 차단해 전력 소모량을 줄인다.

이러한 기능들은 Cortex-M0, Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23 및 Cortex-M33 프로세서에서 지원된다. 이와 함께 다양한 저전력 설계 기술을 통해 전력 소비량을 낮춰준다.

낮은 게이트 카운트로 인해 Cortex-M0과 Cortex-M0+ 프로세서는 Cortex-M3, Cortex-M4, 그리고 Cortex-M7 프로세서보다 전력 사용량이 적다. 또한 Cortex-M0+에는 최적화가 추가로 적용돼 브랜치 쉐도우(Branch Shadows)에 의한 프로그램 액세스와 같은 추가적인 프로그램 액세스 횟수를 줄여 전체적인 시스템의 전력 소모량을 낮게 유지한다.

Cortex-M23은 Cortex-M0이나 Cortex-M0+만큼 작진 않지만 동일한 구성에서 Cortex-M0+ 와 비슷한 수준의 전력 효율성을 지니고 있다.

더욱 우수한 성능과 최적화된 저전력 덕분에 동일한 구성 조건에서 Cortex-M33의 에너지 효율성이 Cortex-M4 프로세서보다 뛰어난 것으로 나타났다.

4.2 비트 밴드(Bit-Band) 기능

Cortex-M3와 Cortex-M4 프로세서는 비트 밴드(Bit Band)라는 옵션 기능을 갖추고 있다. 비트밴드는 2개의 1MB 주소 범위(0x20000000번지부터 시작하는 SRAM 영역 1개와 0x40000000번지부터 시작하는 주변장치영역 1개)가 비트밴드 에일리어스(Alias) 주소를 통해 비트 단위로 접근이 가능하도록(Bit Addressable) 만들어준다.

Cortex-M0, M0+와 Cortex-M1 프로세서에는 해당 기능이 없지만, ARM CMSDK(Cortex-M System Design Kit)의 버스 레벨 컴포넌트를 활용해 시스템 수준에 추가할 수 있다. Cortex-M7 프로세서의 캐시 지원 기능은 비트밴드에서 사용할 수 없기 때문에 비트 밴드 기능을 지원하지 않는다(캐시 컨트롤러가 메모리 공간 앨리어싱(Aliasing)을 인식하지 못한다).

ARMv8-M 시스템용 TrustZone에서는 비트밴드가 지원되지 않는다. 다른 보안 도메인에 존재할 수 있는 2개의 다른 주소로 비트 정보를 에일리어스(Alias)할 필요가 있기 때문이다. 이런 시스템들은 주변장치 데이터의 비트 조작은 비트세트나 클리어 레지스터를 제공해 주변장치 수준에서 처리할 수 있다.

4.3 MPU(Memory Protection Unit: 메모리 보호 장치)

Cortex-M0 프로세서를 제외하고, 다른 Cortex-M 프로세서 제품군에는 MPU 옵션이 있다. MPU는 메모리 액세스 권한, 메모리 속성 또는 메모리 영역을 정의하는데 사용할 수 있다. RTOS(Real-Time Operating System) 체제의 시스템에서 OS는 각 작업에 대한 메모리 액세스 권한과 메모리 구성을 정의해 각 작업이 다른 작업이나 OS 커널이 사용하는 메모리 범위를 오염시키지 않게 할 수 있다.

Cortex-M0+, Cortex-M3, 그리고 Cortex-M4의 MPU에는 8개의 프로그램 가능한 영역이 있고, 프로그래머 모델도 상당히 비슷하다. 주요 차이점은 Cortex-M3/M4 MPU는 시스템 레벨 캐시 유형과 같은 두 레벨의 메모리 속성을 허용하는 반면에 Cortex-M0+ 프로세서 MPU는 한 가지 레벨만 지원한다. Cortex-M7에서 옵션으로 사용가능한 MPU는 8개나 16개 영역을 지원하도록 구성할 수 있고, 두 가지 레벨의 메모리 속성을 허용한다. Cortex-M0과 Cortex-M1는 MPU를 지원하지 않는다.

Cortex-M23과 Cortex-M33에도 MPU옵션이 있으며, TrustZone보안 확장이 적용되면 최대 2개의 보안 소프트웨어용과 비보안 소프트웨어용 MPU를 보유하게 된다.

4.4 단일 사이클 I/O 인터페이스

Cortex-M0+ 프로세서의 고유 기능인 단일 사이클 I/O 인터페이스는 Cortex-M0+가 입출력 제어 작업을 신속하게 처리하도록 도와준다. 대부분의 Cortex-M 프로세서의 버스 인터페이스는 파이프라인 버스 프로토콜인 AHB 라이트(Lite)나 AHB5 프로토콜을 기반으로 하며, 이는 높은 클록 주파수 연산을 가능하게 한다. 즉, 전송할 때마다 매번 2개의 클록 사이클이 필요하다는 것이다.

단일 사이클 I/O 인터페이스는 다용도 입출력 포트(GPIO: General Purpose Inputs/Outputs)와 같은 소형 디바이스 종속적 주변장치 세트와 연결하기 위해 파이프라인되지 않은 단순한 버스 인터페이스를 추가한다. 이 기능을 Cortex-M0+ 프로세서의 낮은 분기 패널티(Branch Penalty) 속성과 결합하면 (파이프라인이 단지 2단계이기 때문), 대부분의 다른 마이크로컨트롤러 아키텍처보다 더 빨리 많은 I/O 컨트롤 연산을 실행할 수 있다.

5. 성능 고려사항

5.1 일반 데이터 처리 성능

일반적인 마이크로컨트롤러 시장에서, 마이크로컨트롤러 성능을 측정하기 위해 벤치마크 수치가 자주 사용된다. 〈표 7〉은 일반적으로 사용되는 벤치마크를 통해 Cortex-M 프로세서의 성능을 보여준다.

.jpg)

드라이스톤(Dhrystone)과 관련해 한가지 주의를 해야할 것은 공식(Official) 수치의 경우 인라인(Inline) 없이, 멀티파일 컴파일레이션 없이 코드를 컴파일해야 한다는 점이다. 그러나 많은 마이크로컨트롤러 벤더들이 완전히 최적화된 상태의 드라이스톤 수치를 인용한다.

하지만 벤치마크 제품군의 결과가 애플리케이션에서 얻을 수 있는 성능의 정확한 추정치를 제공하지 못할 수도 있다. 예를 들어, 단일 사이클 I/O 인터페이스의 효과나 DSP 애플리케이션에서 Cortex-M4/M7의 SIMD 혹은 FPU를 사용하는 가속화 효과가 벤치마크 수치에 반드시 나타나는 것은 아니다.

일반적으로 Cortex-M3와 Cortex-M4은 아래와 같은 기능을 통해 높은 수준의 데이터 처리 성능을 제공한다.

풍부한 명령어 세트 기능

· 하버드(Harvard) 버스 아키텍처

· Write 버퍼(단일 사이클 쓰기 연산)

· 브랜치 타깃의 추측 추출(Speculative Fetch of Branch Target)

Cortex-M33도 하버드(Harvard) 버스 아키텍처 기반이며 풍부한 명령어 세트를 갖고 있다. 하지만 Cortex-M3, Cortex-M4와 달리 Cortex-M33 프로세서는 동일한 클록 사이클에서 최대 2개의 명령어를 실행하도록 허용하는 제한적 이중 이슈(Dual-Issue)를 지원하기 위해 재설계된 효율적인 파이프라인을 보유하고 있다.

Cortex-M7 프로세서는 6단계로 구성된 이중 이슈 파이프라인과 분기 예측 지원 기능을 통해 보다 높은 성능을 제공한다. 또한 명령어와 데이터 캐시뿐만 아니라 긴밀히 연동된 메모리(Tightly Coupled Memory)를 제공해 메인 메모리가 느릴 때조차 (예를 들어, 임베디드 플래시) 성능 저하를 피하기 때문에 높은 시스템 레벨 성능을 구현한다.

그러나 일부 I/O 집약적 작업은 다음과 같은 특징 때문에 Cortex-M0+ 프로세서에서 더 빨리 처리될 수 있다.

· 짧은 파이프라인(분기에 2개의 사이클만 요구된다)

· 단일사이클 I/O 인터페이스

디바이스 별 요인도 있다. 예를 들어, 시스템 레벨 설계, 메모리 속도는 시스템의 성능에 영향을 줄 수 있다.

자체 애플리케이션 코드가 필요에 가장 적합한 벤치마크가 되는 경우가 매우 많다. 어떤 프로세서가 다른 프로세서 보다 두 배 이상의 코어마크(CoreMark) 점수를 기록했더라도, 그 프로세서가 애플리케이션을 두 배 빠른 속도로 수행할 수 있다는 것은 아니다. 시스템 레벨 아키텍처는 I/O 처리 작업이 많은 애플리케이션의 성능에 많은 영향을 줄 수 있고, 이러한 성능은 디바이스마다 다르게 나타난다.

5.2 인터럽트 지연

성능과 관련된 또 다른 측면은 인터럽트 지연이다. 인터럽트 지연은 인터럽트 요청부터 인터럽트 서비스 루틴에서 첫 명령어 실행까지의 클록 사이클 수로 측정하는 것이 일반적이다. 〈표 8〉은 메모리 속도에 의한 지연이 없는 시스템(Zero wait state memory system) 시나리오에서 인터럽트 지연을 보여준다.

.jpg)

사실상 실제 인터럽트 지연은 메모리 시스템 대기 상태(Wait states of the memory system)의 영향을 받는다. 예를 들어, 100 MHz 이상에서 운영되는 많은 마이크로컨트롤러에는 30~50 MHz와 같이 느린 플래시 메모리가 적용된다. 성능 향상을 위해 플래시 액세스 가속화 하드웨어가 사용되고 있지만, 인터럽트 지연은 여전히 플래시 메모리 대기 상태(Wait State)의 영향을 받을 수 있다. 따라서 제로 대기 상태 메모리 시스템(Zero wait state memory system)으로 돌아가는 Cortex-M0/M0+ 시스템이 Cortex-M3/M4/M7 시스템보다 더 짧은 인터럽트 지연 시간을 제공할 수도 있다.

성능을 조사할 때 인터럽트 처리기의 실행 시간을 고려하는 것도 잊어서는 안된다. 일부 8비트 또는 16비트 프로세서 아키텍처의 경우 인터럽트 지연이 매우 짧을 수도 있으나, 인터럽트 요청 처리를 끝내는데 필요한 클록 사이클 수가 몇 배가 될 수도 있다. 그 결과 실질적으로 인터럽트 대응 시간은 훨씬 늦어지고 인터럽트 처리 대역폭은 낮아질 수 있다.

6. 디버그 및 트레이스 기능

6.1 디버그 및 트레이스 기능 개요

Cortex-M 프로세서 제품간에는 여러가지 차이점이 있다. 이러한 차이점은 〈표 9〉에 정리되어 있다.

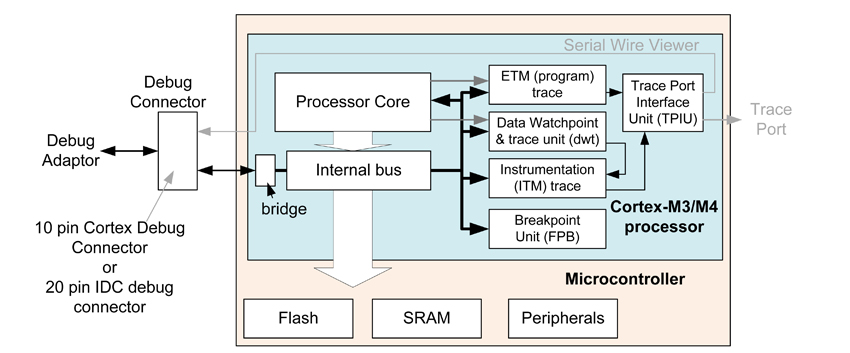

Cortex-M 프로세서의 디버그 아키텍처는 ARM CoreSight 디버그 아키텍처를 기반으로 한다. 이는 확장성이 우수한 아키텍처로 다중 프로세서(Multi-Processor) 시스템을 지원한다.

〈표 9〉에 나타난 정보는 일반적인 설계용이다. CoreSight 아키텍처에서 디버그 인터페이스와 트레이스 인터페이스 모듈은 프로세서로부터 분리가 가능하다. 그렇기 때문에 실제 사용하는 디바이스의 디버그 및 트레이스 연결은 〈표 9〉와 다를 수 있다. 또한 추가 CoreSight 디버그 구성 요소를 추가함으로써 디버그 기능 추가도 가능하다.

6.2 디버그 커넥션

디버그 커넥션을 통해 디버거(Debugger)는 다음과 같은 기능을 수행 할 수 있다.

· 디버그와 트레이스 기능을 제어하는 레지스터 엑세스

· 메모리 맵 엑세스. Cortex-M 프로세서의 경우, 프로세서가 작동하고 있을 때에도 가능하다. 이를 온더플라이(On the Fly) 메모리 액세스라고 한다.

· 코어 레지스터 엑세스. 프로세서가 중단됐을 경우에만 가능하다.

· Cortex-M0+ 프로세서의 MTB(Micro Trace Buffer)가 생성한 트레이스 이력 엑세스 또한 디버그 커넥션은 다음 목적으로도 사용할 수 있다.

· 플래시(Flash) 프로그래밍

Cortex-M 프로세서에서는 4~5개 핀(TDI, TDO, TCK, TMS 및 옵션 nTRST)이 필요한 전통적인 JTAG 커넥션과 핀수가 제한된 디바이스에 이상적인 2개의 핀만 필요한 새로운 시리얼 디버그(Serial Debug) 프로토콜 중에 선택할 수 있다.

시리얼 와이어(Serial Wire) 디버그 프로토콜은 JTAG에서 제공되는 모든 기능을 제어할 수 있고, 패러티 체킹(Parity Checking) 기능도 제공할 수 있다. ARM 툴 벤더들은 시리얼 디버그(Serial Debug) 프로토콜을 많이 도입하고 있으며, 많은 디버그 도입 기업들이 두 가지 프로토콜을 모두 지원한다. 시리얼 와이어 신호는 디버그 커넥터에서 TCK와 TMS 핀을 공유한다.

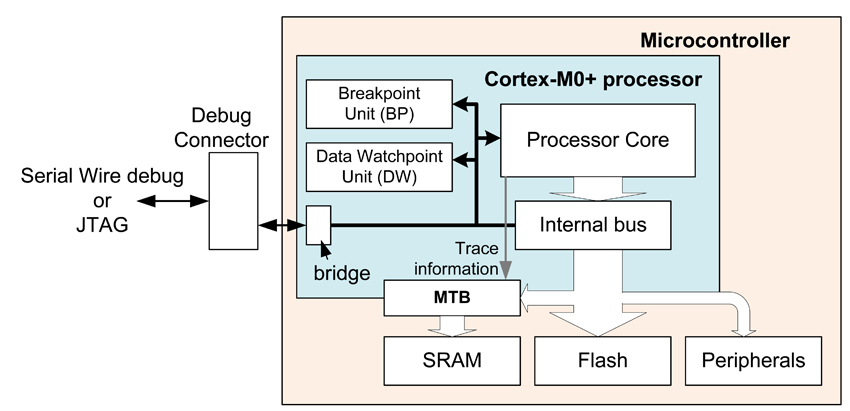

▲ 그림 10. 프로세서의 디버그 기능 및 주변장치를 포함한 메모리 공간 액세스를 허용하는 시리얼 와이어 또는 JTAG 디버그 커넥션

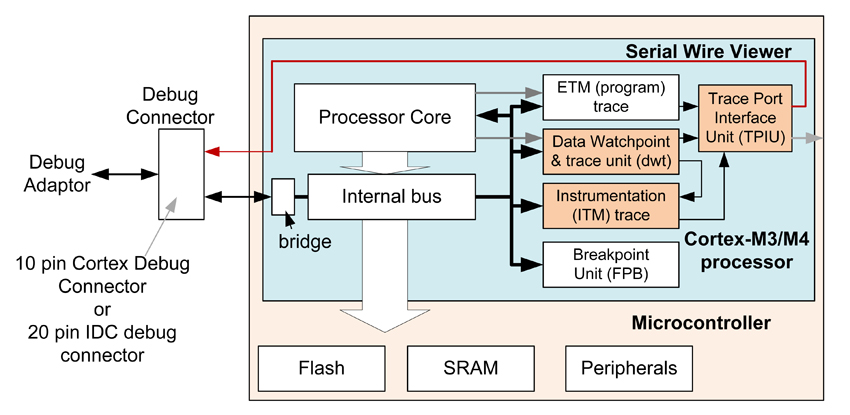

6.3 트레이스 커넥션

트레이스 커넥션 기능을 통해 디버거는 프로그램 실행 중에 실시간으로 프로그램 실행에 관한 정보를 수집할 수 있다. 수집되는 정보에는 Cortex-M3/M4/M7/M33에서 사용 가능한 Embedded Trace Macrocell(ETM)에서 생성된 프로그램 플로우 정보(명령어 트레이스), Data WatchPoint & Trace(DWT) 장치에서 생성된 데이터/이벤트/프로파일링 트레이스, 또는 소프트웨어 컨트롤에 의해 Instrumentation Trace Macrocell(ITM)에서 생성된 정보 등이 있다.

2가지 유형의 트레이스 커넥션이 사용 가능하다.

· 트레이스 포트(Trace Port): 다중 데이터 핀 및 클록 신호. SWV보다 훨씬 높은 트레이스 대역폭을 제공하며, SWV에서 모든 트레이스 유형뿐만 아니라 명령어 트레이스를 지원할 수 있다. Cortex-M3/M4/M7이나 Cortex-M33을 탑재한 디바이스의 트레이스 포트에는 보통 4개의 데이터 핀과 1개의 클록 핀이 있다(그림 11 참조).

· 시리얼 와이어 뷰어(Serial Wire Viewer: SWV): 선택적 데이터 트레이스, 이벤트 트레이스, 프로파일링과 인스트루멘테이션 트레이스(Instrumentation Trace)를 지원하는 단일 핀 트레이스 커넥션(그림 12 참조).

▲ 그림 11. 트레이스 포트는 명령어 트레이스 및 기타 트레이스에 필요한 트레이스 대역폭을 제공한다.

트레이스 커넥션을 통해 프로세서가 돌아가는 동안 충분한 양의 유용한 정보를 캡처할 수 있다. 예를 들어, ETM으로 명령어 실행 이력(명령어 트레이스)을 캡처할 수 있고, ITM을 통해 소프트웨어는 메시지(예. printf를 통해)를 생성하고, 트레이스 커넥션을 통해 캡처할 수 있다. 또한 Cortex-M3/M4/M7/M33에 있는 DWT(Data Watchpoint and Trace) 모듈은 다음 기능을 지원한다.

선택적 데이터 트레이스: 프로세서가 위치에 접근 할 때마다 메모리 위치 정보(예시: 주소, 데이터 값, 타임스탬프 조합)를 포착할 수 있다.

· 프로파일링 트레이스: 다양한 동작(예시: 메모리 액세스, 휴면)에서 CPU가 사용하는 클록 사이클 수

· 이벤트 트레이스: 프로세서가 처리한 인터럽트/예외(Exception)의 이력 및 기간을 제공한다.

▲ 그림 12. 시리얼 와이어 뷰어(Serial Wire Viewer)는 저비용의 LPC(Low-Pin Count)트레이스를 제공한다.

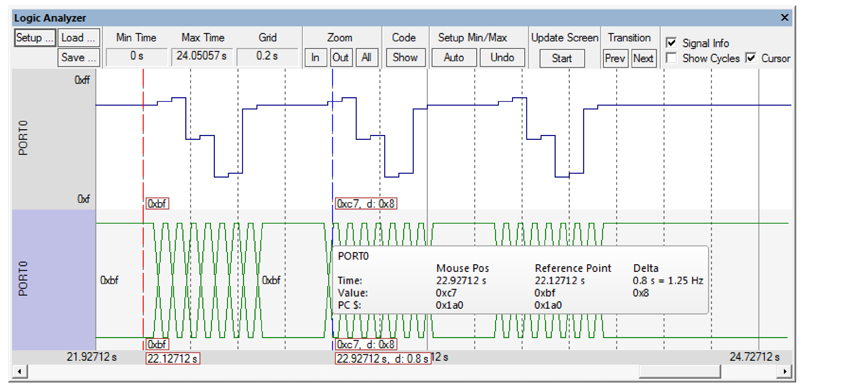

이러한 트레이스 기능들은 여러 툴 벤더들이 폭넓게 지원하고 있고 정보는 여러 방식으로 시각화할 수 있다. 예를 들어, DWT의 데이터 트레이스는 Keil 마이크로컨트롤러 개발 키트의 일부분인 Keil μVision 디버거에서 파형으로 시각화가 가능하다(그림 13 참조).

▲ 그림 13. 카일(Keil) μVision 디버거의 로직 분석기

Cortex-M0와 Cortex-M0+ 프로세서에는 트레이스 인터페이스가 없지만, Cortex-M0+ 프로세서에는 Micro Trace Buffer(MTB)라는 기능이 있다(그림 14 참조). MTB를 통해 사용자들은 시스템 SRAM의 작은 일부를 명령어 저장 목적의 버퍼로 할당할 수 있다. 주로 원형 버퍼(Circular Buffer) 배열로 할당하는데, 이렇게 되면 최근 명령어 실행 이력을 디버거에서 캡처하고 확인할 수 있다.

MTB 트레이스 기능은 Cortex-M23 및 Cortex-M33프로세서에도 제공된다.

▲ 그림 14. Cortex-M0+/M23/M33프로세서의 MTB 기능은 저비용 명령어트레이스 솔루션을 제공한다.

7. ARM Cortex-M 프로세서 제품 개발

7.1 Cortex-M 프로세서가 사용하기 쉬운 이유

Cortex-M 프로세서는 다양한 기능을 지니고 있으며 이러한 기능들을 매우 쉽게 사용할 수 있다. 예를 들어, 대부분의 기능들을 C와 같은 고급언어로 프로그래밍이 가능하다. Cortex-M 프로세서 기반 제품은 서로 다른 메모리 크기와 주변장치, 성능, 패키지를 갖추고 있어 매우 다양하지만, 일관된 아키텍처를 지니고 있기 때문에 Cortex-M프로세서를 사용해보면 새로운 Cortex-M 프로세서를 쉽게 사용할 수 있다.

소프트웨어 개발을 쉽게 만들고, 소프트웨어 재사용성(Reusability) 및 이식성(Portability)을 더욱 개선하기 위해 ARM은 CMSIS-CORE를 개발했다. CMSIS는 Cortex 마이크로컨트롤러 소프트웨어 인터페이스 표준(Cortex Microcontroller Software Interface Standard)을 나타낸다.

CMSIS-CORE는 API 세트를 이용해서 인터럽트 관리 제어 등과 같은 다양한 프로세서 기능에 표준화된 하드웨어 추상화 계층(Hardware Abstraction Layer)을 제공한다. 다양한 마이크로컨트롤러 벤더들이 CMSIS-CORE를 디바이스 드라이버 라이브러리에서 통합하고 있고, 다양한 컴파일레이션(Compilation) 제품군으로 지원된다.

CMSIS-CORE 외에도, CMSIS에는 DSP 소프트웨어 라이브러리(CMSIS-DSP)도 있다. 다양한DSP 함수를 제공하고 Cortex-M4 및 Cortex-M7 프로세서용으로 최적화되어 있으며, 다른 Cortex-M 프로세서도 지원한다. CMSIS-CORE와 CMSIS-DSP 모두 무료이며, GitHub(CMSIS 4, CMSIS 5)에서 다운로드 가능하고, 다수의 툴 벤더가 지원하고 있다.

7.2 프로세서 선택

대부분의 마이크로컨트롤러 사용자들에게 마이크로컨트롤러 디바이스를 선택하는 기준은 비용과 이용 가능한 주변장치에 크게 의존하는 것으로 나타난다. 하지만 차세대 실리콘 제품을 위해 프로세서 코어를 선택하는 실리콘 설계자들도 많을 것이다. 이런 경우에는 프로세서 자체가 주된 기준이 될 것이다.

성능, 실리콘 크기, 전력, 비용 등이 이런 시나리오에서 핵심 요소가 된다는 것은 분명하다. 이와 동시에 고려해야 할 다양한 기타 요인들이 있을 수 있다. 예를 들어, 인터넷과 연결된 제품을 개발하고 있다면 TrustZone 보안 확장 기능과 MPU(Memory Protection Unit)가 적용된 프로세서를 선택해 TrustZone으로 핵심 보안 기능을 보호하고, 권한이 없는 상태(Unprevileged State)에서 나머지 작업을 진행하며 MPU를 통해 메모리 공간을 보호할 수 있다.

이와 반대로 어떤 식으로든 제품을 인증하려면 Cortex-M23이나 Cortex-M33, Cortex-M3, Cortex-M4, Cortex-M7 의 ETM에서 생성된 명령어 트레이스가 코드 커버리지 증명에 매우 유용하게 작용할 수 있다.

실리콘 설계의 다른 측면을 살펴보면, 회수된(Harvested) 에너지로 구동되는 소형 센서를 설계하고 있다면 초소형 크기와 최신 전력 최적화를 갖춘 Cortex-M23이나 Cortex-M0+ 프로세서가 최고의 옵션이 될 수 있다.

7.3 에코시스템

ARM Cortex-M 프로세서의 주요 장점 중 하나는 디바이스, 툴, 미들웨어 등을 광범위하게 지원한다는 것이다. 현재 지원 현황은 아래와 같다.

- ARM Cortex-M 프로세서 기반 마이크로컨트롤러 제품을 출하하는 15개 이상의 마이크로컨트롤러 벤더

- Cortex-M 프로세서를 지원하는 10개 이상의 개발 제품군

- 40개 이상의 OS 벤더가 Cortex-M용 OS 지원

이를 통해 고객사들에게 폭 넓은 선택권을 제공하며 타깃 애플리케이션을 구성하는데 디바이스와 툴, 미들웨어의 최적 조합을 찾을 수 있도록 도와준다.

8. 결론

실리콘 크기 및 전력과 성능 및 기능 중 어느 한 부분을 달성하려면 다른 부분은 늦어지거나 포기해야 하는 경우가 생기기 마련이다. 따라서 ARM은 서로 다른 레벨의 명령어 세트 기능, 성능, 시스템 및 디버그 기능이 구현된 다양한 Cortex-M 프로세서를 개발했다. 이 백서에서는 Cortex-M 프로세서 제품군의 다양한 유사점과 차이점에 대해 설명했다.

제품 간의 차이는 있지만 아키텍처의 일관성과 CMSIS-CORE에서 표준 API가 제공되기 때문에 소프트웨어의 이식성과 재사용성이 더욱 향상됐다. 이와 동시에 Cortex-M 프로세서는 사용하기에 매우 용이하다. 이러한 Cortex-M 프로세서가 마이크로컨트롤러 세그먼트에서 가장 대중성 있는 32비트 프로세서 아키텍처로 빠르게 자리잡아 가고 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>