토마스 뉴(Thomas Neu), 고속 제품ㆍ시스템 엔지니어, 텍사스 인스트루먼트

리시버에서 특히 중요한 사양은 블로커 사양이다. 이것은 인밴드 간섭/차단이 존재할 때 감지할 수 있는 가장 약한 신호 전력레벨을 결정한다.

블록킹 이벤트일 때의 리시버 성능을 알아내려면 시스템 개발자는 데이터 컨버터의 클록 노이즈 부분 등 리시버의 여러 가지 다양한 노이즈 원인들을 분석해야만 한다.

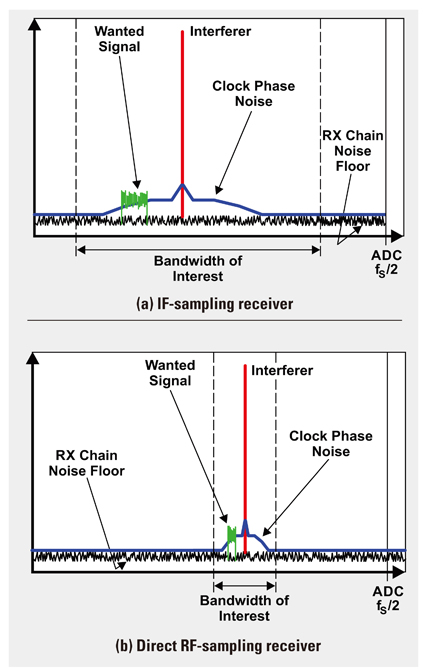

기존의 헤테로다인 리시버에서는 데이터 컨버터 클록의 노이즈 부분은 통합 지터 수를 이용한 시간 도메인에서 주로 파생된다. 직접 RF 샘플링 아키텍처(그림 1)의 경우, 실제 신호 대역폭은 ADC(Analog-to-Digital Converter)의 나이퀴스트 존(Nyquist Zone)보다 훨씬 작을 수 있다. 전체 나이퀴스트 존에서 클록의 페이즈-노이즈 부분을 통합하기 보다는 주파수 도메인에서 주파수 오프셋에 좌우되는 페이즈 노이즈를 직접 다루는 것이 더 합리적일 수 있다. 시간-도메인 방식이 더 간단하긴 하지만, 이것은 비현실적이면서 실용적이지 못한 클록-노이즈가 요구된다.

최근에 ADC12J4000 및 ADC32RF45 같은 고성능 RF 샘플링 컨버터의 등장으로 ADC 샘플링 클록의 외부 페이즈-노이즈 요건에 대해 잦은 문의가 들어온다. 그 대답은 리시버 성능에 대해 고객이 요구하는 바와 데이터 컨버터의 클록 노이즈에 영향을 주는 몇 가지 추가 요인들에 좌우된다. 여기에는 ADC 애퍼처 지터(Aperture Jitter), 클록 진폭이나 슬루율(Slew Rate), 신호 입력 주파수, 입력-신호 진폭, 기타 등등이 해당된다. 이 글에서는 주파수 도메인에서 노이즈 부분을 추론해 그것을 시간-도메인 지터의 기존 계산 방식과 비교하는 방법을 살펴보려 한다.

주파수 도메인에서의 ADC 노이즈 분석

주파수 도메인에서 데이터-컨버터의 노이즈 부분은 아래 다섯 단계를 이용해 분석할 수 있다. 이해를 돕기 위해 입력 신호 주파수에 맞춰 단순하게 표준화시킨 다이어그램을 추가했다.

1 단계

주파수 도메인에서 외부 클록 페이즈 노이즈(PNE)와 ADC 애퍼처 지터(PNA)를 dBc/Hz로 구한다. 그 주파수의 빈 크기(Bin Sizes)와 단계들은 동일해야 한다. 클록 페이즈-노이즈는 로그-타입 포맷으로 제공되는 것이 일반적이다. 주파수 전체에서 ADC 애퍼처 지터가 고르지 않을 것이라 추정되는 경우, 이 페이즈-노이즈 데이터 포맷에 맞게 일부 데이터 보간을 해야 할 수도 있다. 앞서 언급했듯이, ADC 애퍼처 지터는 클록 진폭에 좌우되기 때문에, 이것도 함께 고려해야 한다.

▲ 그림 1. 클록 페이즈 노이즈 부분

2 단계

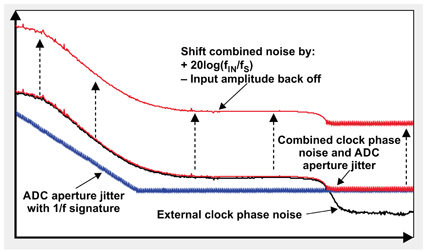

PNC는 방정식 1에서 계산된 병합 외부-클록 페이즈노이즈와 ADC 애퍼처 지터로, 〈그림 2〉에 나와 있다. 상단의 적색 곡선은 단계 3에서 계산한 신호-진폭 백오프에 맞춰 이동을 조정한 것이다.

.jpg)

3 단계

방정식 2는 병합 클록 노이즈의 신호 입력-주파수 이동을 설명한다.

.jpg)

여기에서 fIN은 신호 입력 주파수이고, fS는 ADC 샘플링 레이트다. 신호 입력 주파수가 증가하면 클록 노이즈로 인한 SNR(Signal-to-Noise) 감손도 증가한다.

4 단계

또한 그 입력 신호의 진폭도 확인해야 한다. ADC 풀스케일과 관련해 신호 진폭을 줄이면 클록 노이즈 부분이 바로 줄어든다. 예를 들어, 3 dB 백오프(AIN = -3 dBFS)는 매 주파수 빈마다 노이즈 전력을 3 dB까지 줄인다.

5 단계

마지막 단계는 이동한 클록 노이즈를 데이터 컨버터에 내재하는 열 노이즈와 병합하는 것으로 〈그림 3〉처럼 입력 신호의 특정 주파수 오프셋에 대해 예상되는 그 ADC의 총 노이즈 부분이 나온다.

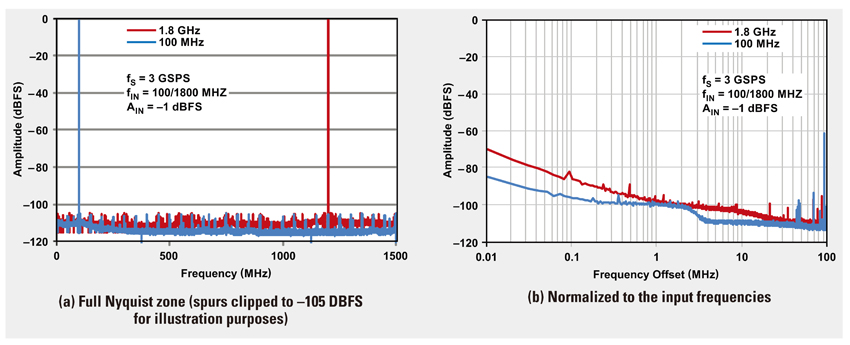

〈그림 3〉의 최종 ADC 노이즈는 여러 가지 사용 사례들을 보여준다. 예컨대, 언더샘플링 시나리오의 높은 입력 주파수의 경우(여기에서 fS=3 GSPS, fIN=1.8 GHz), 이 클록 노이즈 부분이 증가한다. 이것은 그 클록의 클로즈인(Close-In) 페이즈 노이즈를 ADC 열 노이즈 층 위로 밀어 올린다.

▲ 그림 2. ADC 애퍼처 지터를 외부 클록 페이즈 노이즈와 병합한 후의 데이터 컨버터 노이즈

▲ 그림 3. 데이터-컨버터 열 노이즈를 추가한 후의 총 ADC 노이즈

▲ 그림 4. FFT(Fast Fourier transform) 노이즈 비교.

(a) 풀 나이퀴스트 존(설명을 위해 스퍼를 ?105 DBFS에 고정시킴), (b) 입력 주파수 표준화

그 결과 ADC는 클록 지터로 인한 SNR 하락을 겪게된다. 이것을 〈그림 4〉에서 확인할 수 있으며, 〈그림 4a〉에서 1.8 GHz 입력 신호의 적색 곡선은 100 MHz곡선에 비해 더 큰 클로즈인 노이즈와 원거리 노이즈층을 보여주고 있다. 둘 다 높은 입력 주파수로 인한 ADC 애퍼처 지터의 진폭 증가 때문이다.

〈그림 4b〉는 입력 신호 자체의 페이즈-노이즈 시그니처(주파수 코너=3 MHz)를 청색 곡선으로 보여주고 있는데 이것은 아무런 진폭 이동도 겪지 않으면 1.8 GHz 시나리오의 클록 노이즈에서 사라진다.

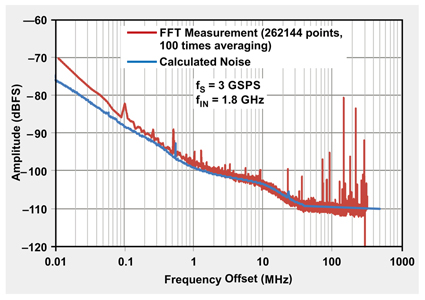

계산과 측정

이 주파수-도메인 분석에서 데이터-컨버터 노이즈를 얼마나 잘 예측할 수 있을까? ADC32RF45의 애퍼처 지터 정보와 클록 및 입력 신호 제너레이터 둘 다의 페이즈 노이즈 정보를 이용한 이전 측정에 대한 노이즈계산을 해보았다. 그 결과가 〈그림 5〉에 나와 있는데 이것은 전원 공급 장치의 노이즈와 온도 효과 같은 그밖의 저하사항을 포함시키지 않을 경우 매우 가깝게 일치한다. 이런 식으로 시스템 개발자는 ADC 클록 노이즈 부분을 특정 주파수 오프셋에서 예측할 수 있다.

▲ 그림 5. FFT 측정과 계산된 데이터 컨버터 노이즈의 비교

시간 도메인과 주파수 도메인의 비교

시스템 엔지니어는 SNRJitter=20log(2πfIN×tJitter)라는 간단한 지터 방정식으로 시간 도메인을 계산하는데 익숙하다. 〈표 1〉은 주파수 도메인 방식을 기존의 시간 도메인 방식과 비교한 것이다.

.jpg)

결론

RF 샘플링 데이터 컨버터의 노이즈 부분을 평가하는 것은 시스템 개발자가 시스템 간섭 사양을 분석할 때 매우 유용하다. 이것을 하나씩 비교하면 시간 도메인방식과 주파수 도메인 방식 둘 다 같은 정보를 사용하고 있음을 알 수 있다. 그렇지만, 주파수 도메인 분석이 주파수 오프셋에 대해 결정적인 애플리케이션 고유 정보를 보존하기 때문에 ADC32RF45 같은 최신의 고성능 RF 샘플링 컨버터에 훨씬 더 잘 맞을 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>