글|해리 루안(Harry Luan), CTO, 킬로패스

킬로패스(Kilopass)가 DRAM 비트셀로 사용할 수 있는 새로운 정적 RAM 비트셀을 개발했다. VLT(Vertical Layered Thyristor) 비트셀이 그것이다. 콘텐츠가 정적이므로 리프레시를 하지 않아도 된다. 또한 새로운 소재나 물리학적 특성을 사용하지 않으므로 기존 팹에서 기존 장비를 사용해서 제조할 수 있다.

VLT 비트셀은 기술적 관점에서 잘 작동할 뿐만 아니라, 기존 DRAM에 비해 경제성 면에서 경쟁력이 뛰어나다. 이글에서는 VLT 비트셀에 대해 개괄적으로 설명하고, 비용 측면에서 다양한 각도로 기존 DRAM과 비교해 보고자 한다. VLT 비트셀로 만들어진 메모리 어레이가 LPDDR4와 완벽하게 호환성을 유지할 뿐만 아니라, 기존 DRAM 비트셀을 사용하는 같은 크기의 메모리 어레이에 비해 비용이 약 45% 절감 된다는 것을 알 수 있다.

VLT 비트셀

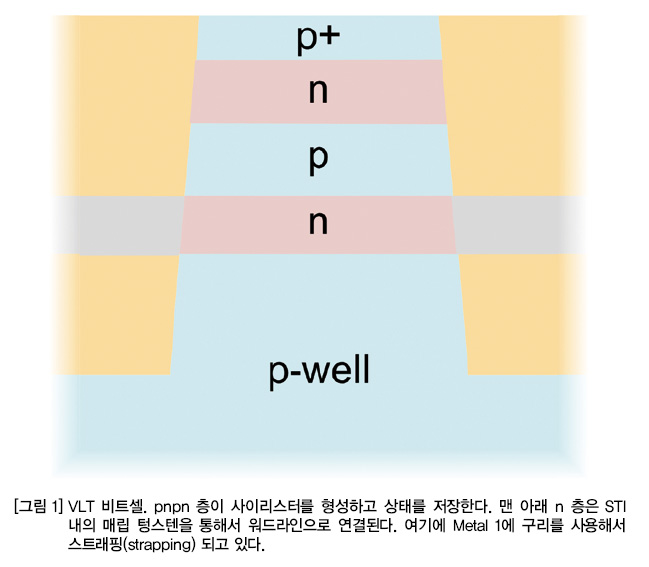

킬로패스의 새로운 비트셀은 SCR(Semiconductor-Controlled Rectifier)이라고도 불리는 사이리스터를 수직 구조로 만든 것이다. 이 구조는 P-우물(p-well) 구조 위에 pnpn 층을 만듦으로써, 정공(Hole)이 인접한 셀들을 방해하지 못하도록 한다(그림 1).

맨 아래 n 층은 매립형(buried) 워드라인을 형성하며, 주어진 워드라인을 따라서 인접한 셀들은 STI(Shallow Trench Isolation) 내의 텅스텐 브리지에 의해서 연결된다. 텅스텐은 비교적 저항이 크므로, 매립형 영역을 따라서 적정한 전압이 유지되도록 하기 위해 대략 매 32셀마다 이 매립형 워드라인을 탭핑(tapping)해야 한다. 또한 전반적인 성능을 달성하기 위해 매립형 워드라인 탭을 구동하기 위한 Metal 1에 구리를 사용한다.

VLT 비트셀은 기존 DRAM 비트셀과 비교해 다음과 같은 특징이 있다.

· 저장 메커니즘이 어떠한 새로운 물리적 성질이나 새로운 소재를 사용하지 않기 때문에 모든 공정에 기존 팹 장비를 사용할 수 있다. 따라서 새로운 설비 투자가 필요 없다.

· 기존 DRAM 업체들에게는 모든 공정 단계가 친숙한 것이다.

· 로직 파운드리 업체들에게는 대부분 공정

이 표준적이다. 매립형 워드라인은 표준 로직 디바이스에서는 통상적으로 사용하는 것이 아니지만, 그에 따른 추가적인 공정들을 표준 CMOS 장비 및 소재를 사용해서 수월하게 구현할 수 있다.

비용 분석

VLT와 기존 DRAM 기술 사이에 다섯가지 요소를 비교해 봄으로써 두 기술의 비용 차이를 이해할 수 있을 것이다. 다섯 가지 요소는 비트셀 크기, 어레이 효율, 금속의 선택, 공정의 복잡성, 리프레시 회로다. 비교를 위해, 공정 노드는 20 nm 혹은 적어도 2x-nm로 가정한다.

비용을 살펴보기 위해서는 전반적인 메모리 솔루션에서 두 가지 구성요소를 구분할 필요가 있다.

우선은 메모리 콘텐츠의 저장 및 검출에 필요한 기술이 주를 이루는 메모리 어레이다. 나머지는 컨트롤러 또는 인터페이스 회로다. 새로운 메모리 비트셀 및 아키텍처를 개발하는 기업으로서 킬로패스가 초점을 맞추고 있는 부분은 메모리 자체의 비용이다. 제어 로직에 대해서도 비용 절감이 가능하지만, 이 글에서는 주로 메모리 어레이와 관련해 논의를 진행해 나갈 것이다.

셀 크기

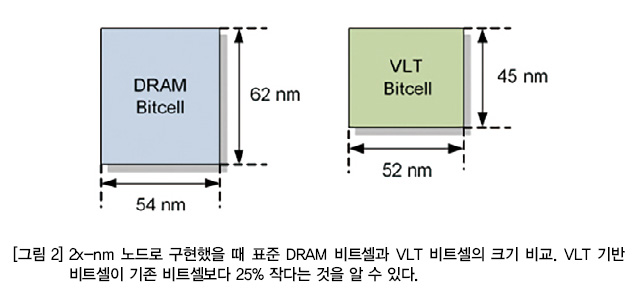

2x-nm 공정 노드를 사용하는 전형적인 커패시터 기반 DRAM 비트셀은 크기가 54 nm×62 nm, 즉 3,348 nm2이다. 일반적으로 DRAM은 추상화된(abstracted) 비트셀 크기가 6F2인 것으로 알려져 있다. 여기에서 F는 최소 프로세스 피처(Feature) 크기다.

이 DRAM의 경우, 비트셀 크기는 F가 23.6 nm로서, 채택한 공정 노드와 같은 수준이다. 그러면 이 F 값을 사용해서 VLT 비트셀과 비교해 볼 수 있다.

VLT 비트셀은 크기가 52 nm×45 nm, 즉 2,496 nm2이다. 기존 DRAM에 비해서 25% 이상 작은 셈이다.

23.6의 F 값을 사용하면 추상화된 VLT 비트셀 크기는 4.47F2라는 것을 알 수 있다(그림 2).

어레이 효율

메모리 기술에 따라서 그 기술을 활용해 제조할 수 있는 최대 메모리 어레이 크기가 결정된다. 이것을 메모리 어레이타일(Memory Array Tile: MAT)이라고 한다. 이는 통상적으로 워드라인의 구동능력과 비트라인의 검출 능력에 의해 결정된다. 이들 MAT를 타일처럼 배치해서 원하는 저장 용량의 고용량 메모리를 만들 수 있다. 동일한 크기의 메모리를 만든다고 가정했을 때, MAT가 작을수록 더 큰 MAT를 사용할 때보다 메모리 레이아웃 상에서 더 많은 횟수를 반복해야 한다.

VLT 기술은 Metal 1에 구리를 사용하여 매립형 워드라인을 스트래핑하기 때문에 훨씬 더 긴 워드라인을 구동할 수 있다. 워드라인이 더 길어진다는 것은 MAT가 더 커질 수 있다는 것을 뜻한다.

각 MAT마다 워드라인 디코더와 드라이버 오버헤드가 필요하므로, MAT의 수가 적어지면 이 오버헤드 회로의 사용 횟수를 줄일 수 있어 어레이 효율을 높일 수 있다.

또한 VLT 메모리는 더 긴 비트라인을 지원할 수 있다. 셀 콘텐츠를 검출하기 위해 전하 공유(Charge Sharing)에 의존하지 않기 때문이다.

일례로, 기존 DRAM MAT는 620 kbit의 어레이 크기가 가능하다. VLT MAT 어레이 크기는 8 Mbit로 훨씬 크다. 이 VLT MAT의 전체적인 크기는 245.68 μm×110.22 μm, 다시 말해서 2만 7,079 μm2다. 8 Mbit의 경우, 비트셀 면적은 2만 938 μm2로서, 어레이 효율이 77%에 달한다. 기존 DRAM MAT는 비슷한 기술을 사용했을 때 효율이 65%인 것으로 알려졌다.

8 Gbit 메모리를 만들려면 기존 DRAM MAT는 1만 3,568개가 필요하지만, VLT MAT는 1,024개만 있으면 된다. 더 작은 비트셀과 더 큰 MAT를 사용해서 더 높은 효율을 달성함으로써 VLT 어레이 크기는 8.4 mm×4.6 mm, 즉 38.64 mm2다. 이에 비해 DRAM 8 Gbit 어레이는 크기가 9.7 mm×5.8 mm, 즉 56.26 mm2다. VLT 어레이가 기존 어레이보다 31%가 더 작다(그림 3).

.jpg)

위에서 계산한 어레이 효율은 단일 MAT에 대한 것이다. 전체적인 메모리 어레이 효율은 8Gbit에 해당하는 비트셀 수를 더한 다음, 전체 면적을 그 수로 나눔으로써 계산할 수 있다. 기존 DRAM은 총 비트셀 면적이 28.8 mm2로서, 효율은 51%다. VLT 비트셀은 총 비트셀 면적이 21.4 mm2이고, 효율은 55%다.

Metal 1

첫 번째 metal 층은 통상적으로 텅스텐이다. 텅스텐은 저렴한 소재이고 또한 패턴을 형성하기가 더 용이하다. 하지만 전도체로서는 성능이 떨어진다. VLT 메모리는 텅스텐 매립형 워드라인을 스트래핑하기 위해서 Metal 1에 구리를 사용한다. 구리는 약 3% 더 비싸다.

구리는 매립형 워드라인을 안정적으로 유지할 뿐 아니라 긴 라인과 최소한의 피치로도 텅스텐을 사용할 때보다 더 긴 워드라인을 구동할 수 있다. 따라서 이로 인한 어레이 효율 향상은 금속 공정에 필요한 추가 비용을 상쇄하고도 남는다.

공정 복잡성

기존 DRAM 공정은 복잡하다. 매립형 워드라인이 트랜지스터 회로를 밑에서 받치고, 그 다음으로 저장 커패시터가 트랜지스터 위로 올라온다. VLT 기반 메모리는 커패시터 기반 DRAM에 필요한 공정 단계 수의 2/3만을 사용한다. 저장 커패시터를 위한 추가공정 및 재료비가 총 DRAM 제조비의 60%를 차지한다고 한다.

반면 VLT 기반 메모리는 저장 커패시터를 사용하지 않으므로 이 비용을 절약할 수 있다.

2x-nm 공정 노드로 제조되는 기존 DRAM을 살펴보면 커패시터를 제조하기 위해서 다수의 특화된 공정 단계와 기술을 사용한다는 것을 알 수 있다. 이에 반해서 VLT DRAM 비트셀은 커패시터를 전혀 사용하지 않는다. 기존 DRAM에 의해 발생되는 복잡성들의 몇가지 예들은 다음과 같다.

· 저장 커패시터는 ZrO2/Al2O3/ZrO2(통상 ZAZ로 약칭)로 이루어진 원통형 층을 사용한다. 이것은 저장 커패시터에 사용되는 것을 제외하고는 통상적인 구조가 아니다.

· 첨단 공정 노드의 저장 커패시터는 측면을 따라서 에어 갭을 사용한다.

· 저장 커패시터를 형성하기 위해서는 최소한 2개의 추가적인 선택적 에피택시 단계가 필요하다.

· 이 커패시터는 종횡비(aspect ratio)가 매우 높기 때문에 기계적 스트레스를 일으킨다. 따라서 하나 이상의 MESH(Mechanically Enhanced Storage Node)를 사용해 이 스트레스를 줄이도록 해야 한다.

리프레시

DRAM은 동적 특성으로 인해서 저장노드가 누설을 일으키기 때문에 지속적으로 리프레시를 해야 한다. 또한 읽기 과정이 파괴적(destructive)이어서 읽기를 한 후에는 값을 복원해야 한다. 메모리에 쓰기를 하려면 페이지를 따라서 모든 셀이 올바른 값을 유지하도록 읽기-수정-쓰기 사이클을 거쳐야 한다.

비교적 간단한 상태기(state diagram)가 될 수도 있던 것이, 이러한 이유로 인해 지극히 복잡한 메커니즘을 수행하게 되면서 회로와 비용을 증가시키게 됐다. 〈그림 4〉는 기존 DRAM의 상태기 다이어그램을 나타낸 것으로, 리프레시와 관련된 상태들을 볼 수 있다.

.jpg)

VLT 기반 메모리는 LPDDR4 표준과 완벽한 호환성을 유지하면서 위의 상태기(state machine)를 〈그림 5〉와 같이 단순화할 수 있다.

이 상태기는 DDR 컨트롤러에 의해 실현되며, 이 컨트롤러는 메모리 어레이와 실제 물리적 I/O 모두에 연결된다. VLT기반 메모리 어레이에 표준 컨트롤러를 연결할 수 있지만 리프레시 관련 동작은 무시될 것이다.

.jpg)

이처럼 단순화된 상태기(state machine)는 컨트롤러 상에서의 가능한 효율적 운영을 보여준다. 최적화된 컨트롤러를 사용할 수 있으므로 더 적은 실리콘 면적을 사용할 수 있으며 전력 소비도 줄일 수 있다. 또한 리프레시 타임아웃을 없앨 수 있으므로 전반적인 대역폭(bandwidth)을 향상시킬 수 있다.

맺음말

결론적으로 VLT 기술은 LPDDR4 호환 DRAM에서 상당한 비용 절감 기회를 제공한다. 더 작은 비트셀, 더 큰 최대 기본 어레이(그로 인한 더 높은 어레이 효율), 더 단순한 공정(기존 장비 및 소재만을 사용)를 사용함으로써 기존 DRAM 기술에 비해서 메모리 어레이 제조 비용을 45%까지 줄일 수 있다.

뿐만 아니라 리프레시가 필요 없어 컨트롤러 회로를 추가적으로 줄일 수 있다. 이처럼 더 높은 어레이 효율을 달성함으로써 얻게 된 절감 비용이 구리 금속 1에 따른 비용이나 LPDDR4 플러그인 기능을 동일하게 구현하기 위해 사용되는 회로에 관련된 비용을 상쇄하고도 남는다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>