BER(Bit Error Rate)은 임의의 디지털 데이터를 전송하고 복조 시, 보낸 데이터에서 오류 데이터의 비율을 나타낸다. BER을 측정하기 위한 장치나 절차를 위해 BERT(Bit Error Rate Tester)가 필요하며 현재 많은 모델이 나와 있다. BERT(Bit Error Rate Tester)의 장점은 높은 유연성과 기능, 성능을 제공해 기업의 제품 개발 사이클을 단축시키고 검증 테스트 비용을 크게 줄여준다는 것이다.

텍트로닉스, 최고 28.6 Gb/s 테스트 지원

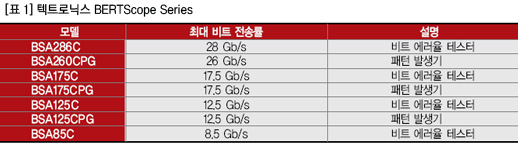

텍트로닉스는 최근 늘어나는 100G 테스트 요구에 대응하여 BERTScope 비트 에러율 테스터 시리즈를 대폭 확장했다. 새로운 비트 에러율 테스터 BSA286C BERTScope는 오류 검출과 패턴 생성, 클록 복구를 포함해 최고 28.6 Gb/s의 표준 적합성 테스트를 지원한다. 또한 업계 최고 수준인 300 fs 미만의 고유 지터 노이즈 플로어로 광학 통신 테스트 제품군에 정밀한 BER 테스트 및 PHY 원인 분석 기능을 제공한다. 디버깅 애플리케이션의 경우, 엔지니어는 BSA286C를 사용해 지터를 무작위/확정적 성분으로 정확히 분해할 수 있는 추가 기능으로 발생 가능성이 낮은 이벤트를 포함한 다양한 신호에 확실한 지터 측정을 수행할 수 있다. BERTScope는 BUJ(Bounded Uncorrelated Jitter)를 분리해 크로스토크와 관련된 잠재적인 설계 문제를 신속히 파악할 수 있는 지터 분해 모델이 적용됐다. 100G 테스트의 경우, 28.6 Gb/s BER(비트 에러율) 스트레스 리시버 테스트가 표준 적합성 및 성능을 보장하는 데 중요한 조건이다. 이 데이터 전송률은 100 GBASE-LR 및 ER-4의 25.78125 Gb/s 데이터 전송률과 함께 필요한 마진 검증 및 FEC(순방향 오류 정정)에 적합한 여유를 제공한다. BERTScope에서 제공하는 고속 패턴 생성과 오류 검출 기능의 조합을 활용하면 원인 분석 디버그와 관련된 복잡한 측정 시나리오에서 빠르게 해답을 얻을 수 있다. 텍트로닉스는 모든 범위의 100G 설계 과제에 대응하여 PHY TX, RX, 광학 변조에 대해 계측기 기능 및 측정 전문 지식을 제공한다.

안리쓰, 확장 가능한 모듈형 BERT

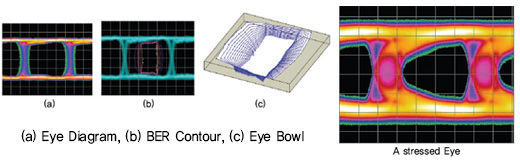

안리쓰의 MP1800A는 확장 가능한 플러그인 모듈 형태의 비트 에러율 테스터기다. MP1800A는 고품질, 고진폭 신호를 출력할 수 있는 펄스 패턴 발생기(PPG)와 배스텁 지터 및 아이 다이어그램(Eye Diagram) 측정과 같은 신호를 분석할 수 있도록 고입력 감도 오류 감지기(ED)가 내장됐다. 또한 SJ/RJ/BUJ/SSC 등의 다양한 지터를 생성하고 지터 내성 테스트를 지원하는 지터 변조 소스를 탑재했다.

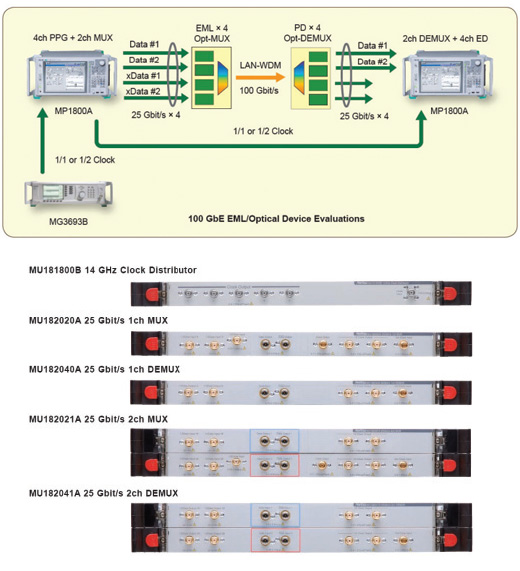

MP1800A는 100 GbE(25 G×4)와 OTU-4(28 G×4), 32 G DP-QPSK, CEI-28 G, 32 G FC, Infiniband EDR(26 G) 등 다양한 신호 무결성을 분석할 수 있도록 최대 32 Gbit/s(0.1 ~ 32.1 Gbit/s)의 비트 레이트를 제공한다. MP1821A 및 MP1822A를 함께 사용하면 최대 56 Gbit/s의 BER 테스트를 지원해 CEI-56 G-VSR을 포함한 차세대 R&D 연구에 적합하다. 1/2/4채널은 32 Gbit/s에서 최대 8채널의 다채널 동기화를 지원하는 PPG 또는 ED 모듈별로 선택이 가능하다. 이밖에도 AOC, QSFP+, CXP, CFP 모듈은 동시에 측정이 가능하며 크로스토크 및 스큐 내성을 평가할 수 있다.

한편 올인원 MP1800 시리즈는 EA 및 EML 모듈레이터 평가, 광 모듈레이터 R&D 및 라인 생산성과 품질 개선을 위해 고진폭 신호를 생성하며 광 인터페이스를 지원해 IEEE802.3-2005 10 GBASE-L 및 E 가압 리시버 적합성 시험에 이상적이다.

MP1800A의 주요 특징

- 최대 56 Gbit/s의 구성을 갖춘 0.1~32.1 Gbit/s의 넓은 대역폭

- 고품질, 낮은 지터 파형

- 최대 32.1 Gbit/s의 지터 내성 테스트(SJ, RJ, BUJ, SSC, 2-톤 SJ)

- 높은 입력 감도 및 넓은 위상 여유의 신호 품질 분석

- PON 버스트 측정 및 루프 회로 측정

- 광 인터페이스

- 다채널 구성을 사용한 크로스토크 테스트(8채널)

애질런트, 고성능 시리얼 BERT

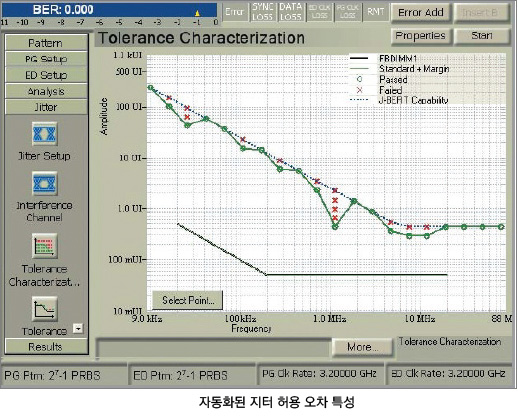

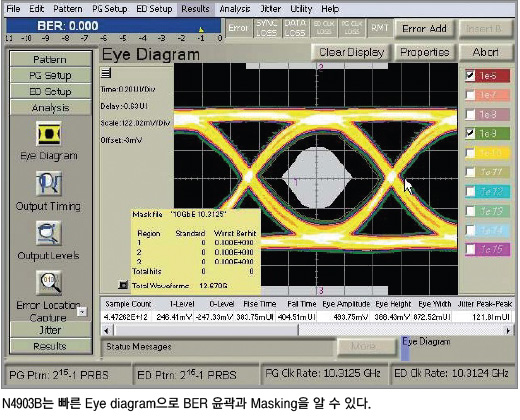

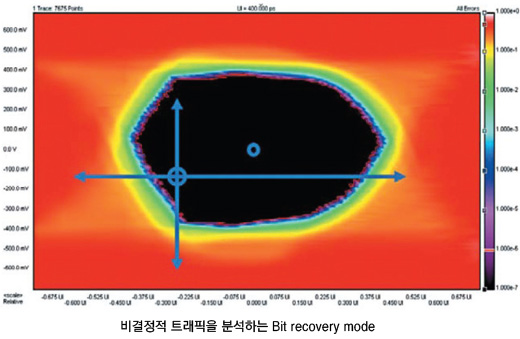

애질런트의 J-BERT N4903B 고성능 시리얼 BERT는 임베디드 및 포워드 클록킹 디바이스를 위해 완전한 지터 허용오차 테스트를 제공한다. 이 제품은 최대 7 Gb/s 또는 12.5 Gb/s의 시리얼 I/O 포트가 있는 칩 및 송수신기 모듈을 특성 분석하고 스트레스를 가하는 R&D 및 검증 팀에게 적합하다. 또한 수신기의 지터 허용오차를 특성 분석할 수 있으며 PCI Express, SATA/SAS, DisplayPort, USB SuperSpeed, 광섬유 채널, QPI, HyperTransport 등의 가장 보편적 시리얼 버스 표준 준수를 입증하도록 설계됐다. J-BERT N4903B의 특징은 매우 낮은 지터 및 초고속 전이 시간을 지원하는 패턴 발생기의 깨끗한 신호를 통해 정확한 특성 분석이 가능하다. 내장 교정 지터 소스를 통해 수신기의 지터 허용오차를 정확히 테스트할 수 있다. 또한 클록없는 비결정적 패턴을 분석하기 위해 차동 I/O, 대부분 출력에서의 가변 전압 레벨, 내장 지터 및 ISI, 패턴 시퀀서, 레퍼런스 클록 출력, 튜닝 가능한 CDR, 패턴 캡처 및 비트 복구 모드를 통해 최적으로 시리얼 버스 표준에 부응하도록 설계되어 테스트 셋업을 크게 간소화할 수 있다. 특히 J-BERT의 자동화된 지터 허용오차 테스트 토털 지터 측정을 통해 고속 테스트 실행이 가능하다.

N4903B의 주요 특징 및 사양

- 데이터 속도 150 Mb/s ~ 7 Gb/s 또는 ~12.5 Gb/s의 패턴 발생기 및 오류 검출기

- > 0.5 UI 교정, 호환 및 통합 지터 주입: RJ, RJ-LF, RJ-HF, PJ1, PJ2, SJ, BUJ, ISI, 정현파 간섭, SSC 및 잔여 SSC의 우수한 신호 성능 및 감도

- 튜닝 가능한 호환 루프 대역폭으로 내장 클록 데이터 복구

- 포워드 클록킹 디바이스를 위한 가변 듀티 사이클의 HR(half-rate) 클록킹

- RJ/DJ 분리, 아이 다이어그램, 아이 마스크, BER 컨투어, 자동화된 지터 허용오차, 패턴 캡처를 통해 BER, BERT Scan, TJ 측정

- 60블록 패턴 시퀀서를 사용한 PRBS 및 패턴

- 모든 옵션은 개조 가능하며 N4903A로부터 업그레이드 가능

한편, J-BERT N4903B 고성능 시리얼 BERT는 고객의 상황에 테스트 및 예산 요구사항에 맞게 구성할 수 있으며, N4903A 모델에서 업그레이드하고 나중에 테스트 요구 변화 시 모든 옵션 및 최대 속도의 개조도 가능하다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>