차세대 저항 메모리 원리와 응용

저항 메모리(Resistive Random Access Memory, RRAM)는 전기적 자극에 의해 저항 상태를 변화시키고, 그 상태를 비휘발성으로 유지하는 원리를 바탕으로 고속 연산 및 저전력 메모리를 구현할 수 있는 차세대 소자이다. 이번 기고에서는 저항 메모리의 기본 구조와 구동 원리를 설명하고, 인메모리 컴퓨팅(In-Memory Computing) 및 뉴로모픽 컴퓨팅 등 다양한 응용 분야에서 갖는 잠재력과 향후 발전 방향을 모색하고자 한다.

.jpg)

글/ 고려대학교 주병권 교수 연구실

주병권 (고려대학교 전기전자공학부 교수)

박준하 (고려대학교 전기전자공학부 석사 과정)

유성민 (고려대학교 전기전자공학부 석사 과정)

1. 서론

2. 저항 메모리 구조 및 동작원리

2-1. 저항 메모리 구조

2-2. 저항 메모리 동작원리

3. 저항 메모리 크로스바 어레이 및 누설 경로 전류

3-1. 저항 메모리 크로스바 어레이

3-2. 누설 경로 전류 문제 및 해결방안

4. 저항 메모리 어레이 응용 및 전망

4-1. 저항 메모리 기반 연산 방식

4-2. 이미지 분류에서의 저항 메모리 어레이 활용

4-3. 그 외 저항 메모리 어레이 응용 분야

5. 결론

6. 참고 문헌

1. 서론

최근 데이터 폭발과 인공지능, 사물인터넷(IoT) 등 신기술의 발전에 따라, 전통적인 폰 노이만(von Neumann) 아키텍처가 지니는 데이터 이동 병목 및 에너지 소모 문제가 두드러지게 나타나고 있다. 이러한 문제를 극복하기 위해 메모리 내에서 직접 연산을 수행하는 인메모리 컴퓨팅 기술이 주목받고 있으며, 그 핵심 소자로서 멤리스터(Memristor) 메모리 중 하나인 저항 메모리가 각광받고 있다.

저항 메모리는 전기적 자극에 의해 저항 상태를 변화시키고, 그 상태를 비휘발성으로 유지하는 원리를 바탕으로, 고속 연산과 저전력, 고집적화 메모리 구현이 가능하여 차세대 컴퓨팅 아키텍처의 혁신적 해결책으로 제안되고 있다

2. 저항 메모리 구조 및 동작원리

2-1. 저항 메모리 구조

저항 메모리는 일반적으로 금속-절연체-금속(Metal-Insulator-Metal, MIM) 구조로 구성된다. 이 구조에서 절연층은 주로 산화물 계열의 재료가 사용된다. 또한 저항 메모리는 상부와 하부 전극의 종류에 따라서 스위칭 메커니즘이 달라지게 된다. 전도성 필라멘트(conductive filament)가 산소 공공(oxygen vacancy)으로 이루어진 원자가 변화 메모리(Valence Change Memory, VCM)는 주로 상부, 하부 전극이 비활성 금속이다. 필라멘트가 금속 이온으로 이루어진 전기화학적 금속화 메모리(Electrochemical Metallization Memory, ECM)는 주로 상부 전극이 활성 금속, 하부 전극이 비활성 금속으로 사용된다.

그림 1. 저항 메모리의 구조 및 필라멘트 형성 모식도. [1]

2-2. 저항 메모리 동작 원리

절연층은 평상시에는 전류가 흐르지 않도록 고저항 상태(High Resistance State, HRS)이지만, 전압이 인가되어 이온들이 움직이면 전도성 필라멘트가 형성되어 전류가 흐를 수 있는 저저항 상태(Low Resistance State, LRS)로 전환된다.

그림 2. 저항 메모리 필라멘트 형성 및 분해 과정에 따른 전압-전류 그래프. [2]

초기 제작된 저항 메모리 소자는 일반적으로 고저항 상태에 있다. 외부로부터 전압이 인가되면 절연층 내에서 국부적인 절연 파괴(soft breakdown)가 발생하면서 전도성 필라멘트가 형성되는데, 이 과정을 형성(Forming)이라고 하며, 형성 이후 소자는 더 낮은 전압으로 스위칭이 될 수 있게 된다. 한 번 형성시키고 난 뒤, 전압을 인가하면 소자는 저저항 상태로 전환된다. 이 과정을 SET 과정이라고 하며 반대로, 소자에 역방향 전압을 인가하면 필라멘트가 끊어지고 고저항 상태로 돌아가는데, 이 과정을 RESET 과정이라고 한다.

투과 전자 현미경(Transmission Electron Microscope, TEM) 분석을 통해 실제 저항 메모리의 필라멘트를 관찰할 수 있다.

그림 3. (a) 소자 제작 직후의 초기 상태, (b) 형성 과정, 절연체 내에서 절연 파괴가 일어나 금속 이온들이 전도성 필라멘트 형성, (c) Reset 과정. [3]

그림 4. (h) Set 과정. 전도성 필라멘트가 형성되어 저저항 상태로 전환, (i) Reset 과정. 전도성 필라멘트가 끊어져서 고저항 상태로 전환. [3]

이러한 동적 변화는 이온이 전기장 방향으로의 표동(drift) 및 양극(anode)과 음극(cathode)에서 일어나는 산화-환원 반응으로 설명될 수 있다.

향후 저항 메모리 기술의 상용화를 위해서 스위칭 메커니즘에 대한 이해를 바탕으로 소자 간 균일성(uniformity) 확보, 내구성(endurance) 향상, 다중 저항 단계(multi-resistance level) 등이 개선되어야 한다.

3. 저항 메모리 크로스바 어레이 및 누설 경로 전류

3-1. 저항 메모리 크로스바 어레이

저항 메모리를 대규모 병렬로 집적시키기 위해서는 워드 라인(word line)과 비트 라인(bit line)의 교차점에 저항 메모리를 배치시키는 구조를 사용하게 된다.

일반적으로 크로스바 어레이(crossbar array)의 구조는 다음과 같다.

하나의 저항 메모리(1R) 크로스바 어레이: 단일 저항 메모리만 존재하는 구조이다. 외부 소자가 없어 호환성(compatibility) 문제가 없으며 대규모 집적이 가능하다. 하지만 누설 경로 전류(sneak path current)의 문제가 발생한다.

하나의 트랜지스터-하나의 저항 메모리(1T1R) 크로스바 어레이: 하나의 트랜지스터와 하나의 저항 메모리가 직렬 연결되어 교차점에 배치되며, 누설 경로 전류를 억제할 수 있지만 고집적도의 한계가 존재한다.

하나의 선택 소자(selector)-하나의 저항 메모리(1S1R) 크로스바 어레이: 선택 소자와 저항 메모리를 함께 사용하여 교차점에 배치되며, 누설 경로 전류를 억제할 수 있다. 고집적도를 달성할 수 있지만 저항 메모리와의 호환성 문제가 발생한다.

대규모 크로스바 어레이의 문제점 중 가장 큰 문제는 누설 경로 전류이며, 이에 관해서는 2-2 절에서 자세하게 논의된다.

3차원 적층 구조

집적 한계를 넘어서기 위해 크로스바를 3차원으로 적층한다.

수평 적층 구조(Horizontal-stacked structure): 2D 크로스바 층을 포토 공정으로 반복하여 수직으로 적층한다. 공정 호환성이 높지만 층 수가 늘어날수록 리소그래피(lithography) 비용이 증가한다.

수직 적층 구조(Vertical-stacked structure): 구동선을 90° 회전해 수직 기둥 전극과 수평 평면 전극이 교차하도록 설계, 동일 면적에서 더 많은 셀을 확보한다. 최근 8층 수직 적층 구조나 3차원 큐브 형식이 시연돼 고밀도 뉴로모픽 칩으로 확장 중이다.

그림 5. (a) 저항 메모리 크로스바 어레이, (b) 수평 적층 구조, (c) 수직 적층 구조. [4]

3-2. 누설 경로 전류 문제 및 해결 방안

그림 6. 저항 메모리 크로스바 어레이의 누설 경로 전류. [5]

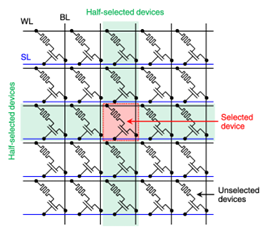

저항 메모리로만 이루어진 크로스바 어레이는 전류가 의도하지 않은 경로로 흐를 수 있는 구조적인 한계를 갖는다. 이때, 발생하는 전류를 누설 경로 전류라고 한다. 위

그림 6에서 선택 셀(selected cell, 1)을 읽을 때, 선택 셀에 인접한 부분 선택 셀(half-selected cell, 2, 4)과 비 선택 셀(un-selected cell, 3)을 통한 우회 경로에서 전류가 흐르게 된다. 이는 어레이에서의 부정확한 읽기 및 쓰기가 발생할 수 있다. 특히 저저항 상태를 가지는 누설 경로가 많을수록 전체 전류가 증가하고 원하는 셀의 전류보다 더 커지게 된다.

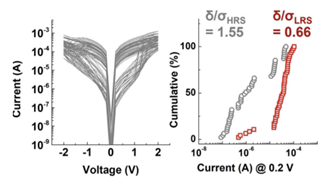

그림 7. 단일 멤리스터에 대한 전류-전압 곡선과 동작 주기(cycle)에 따른 누적 분포도(CDF). [7]

그림 8. 8x8 어레이에 대한 전류-전압 곡선과 동작 주기에 따른 누적 분포도. [7]

단일 멤리스터에 비해서 8x8 어레이일 때, 변동성(variation)이 더 커진 것을 확인할 수 있는데, 이는 누설 경로 전류 때문이다.

이러한 누설 경로 전류를 억제하기 위해서는 어떤 방법이 있을까?

크로스바 어레이에 트랜지스터를 부착하는 방법, 자가 정류(self-rectifying) 저항 메모리를 이용하는 경우가 있다.

그림 9. 하나의 트랜지스터-하나의 저항 메모리의 크로스바 어레이. [6]

그림 9를 보면 트랜지스터로 오직 선택 셀 만을 선택할 수 있어 누설 경로 전류가 흐르지 않게 된다. 이를 통해 읽기 및 쓰기 정확도를 향상시키며 대규모 어레이 구조에서도 안정적인 결과를 얻을 수 있게 된다. 하지만, 트랜지스터가 추가됨으로써 최소 셀 면적이 6 F

2로 증가하고, 고집적화를 달성하는데 한계가 존재한다.

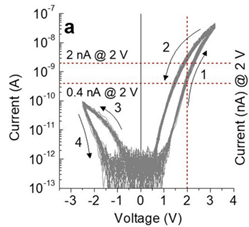

그림 10. 자가 정류 특성을 가지는 저항 메모리의 전류-전압 곡선. [8]

그림 10의 음의 전압에서 전류가 굉장히 억제되고 특성이 매우 비선형적(nonlinear)이며 비대칭적인(asymmetric) 특성을 가지는 것을 볼 수 있다. 이러한 소자를 자가 정류 저항 메모리라고 하며, 트랜지스터 없이 크로스바 어레이로 올리게 되면 셀 면적은 4 F

2로 매우 작고, 누설 경로 전류는 없어지며 대규모 어레이 구현이 가능하게 된다. 하지만 비선형적이고 비대칭적인 특성으로 시뮬레이션 및 회로 설계의 복잡도가 증가한다. 또한 그러한 다이오드와 같은 특성을 얻기 위해서 산화막 두께, 인터페이스를 정밀하게 조정해야 하므로 소자 제작에 어려움이 있다.

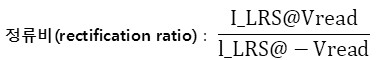

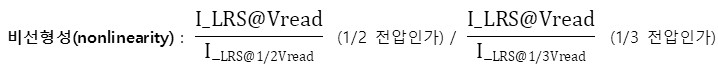

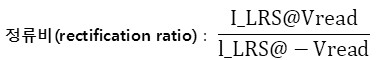

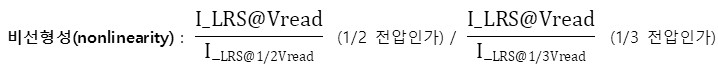

자가 정류 저항 메모리에서의 주요 파라미터는 다음과 같다.

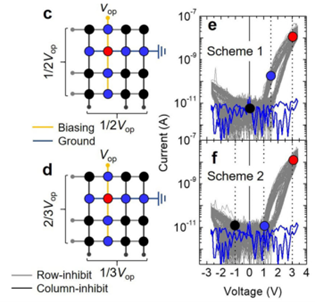

파라미터들은 소자 자체 특성 말고도 크로스바 어레이에서의 전압 인가(biasing) 기법을 통해서 조절할 수 있는데, 그 전압 인가 기법은 주로 1/2 전압 인가(half biasing)과 1/3 전압 인가(third biasing)가 있다.

그림 11. 전류-전압 곡선에서 선택 셀, 부분 선택 셀, 비 선택 셀에 인가되는 전위, (c), (e) 1/2 전압 인가, (d), (f) 1/3 전압 인가. [8]

이러한 전압 인가 방법들을 통해서 부분 선택 셀이나 비 선택 셀에 인가되는 전위를 조절할 수 있게 된다.

| |

1/2 전압 인가 |

1/3 전압 인가 |

| 선택 셀 (빨강) |

Vop |

Vop |

| 부분 선택 셀 (파랑) |

1/2Vop |

1/3Vop |

| 비 선택 셀 (검정) |

0 |

-1/3Vop |

표 1. 전압 인가 방법에 따른 셀들에 걸리는 전위

4. 저항 메모리 어레이 응용 및 전망

4-1. 저항 메모리 기반 연산 방식

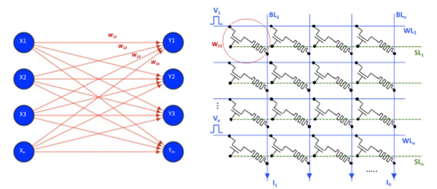

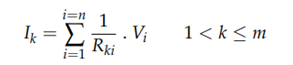

저항 메모리 크로스바 어레이는 벡터-행렬 곱셈(Vector-Matrix Multiplication, VMM) 연산을 아날로그 병렬 방식으로 구현하는데 활용될 수 있다. 크로스바 어레이 행에 입력 벡터(input vector)를 전압으로 인가하고 저항 메모리의 전도도(conductance)가 가중치(weight)에 해당하도록 미리 프로그래밍하면, 각 크로스바 셀에서 옴의 법칙에 의해 전류가 생성된다. 이 전류들은 같은 열을 통해 더해지는데, 키르히호프의 전류 법칙((Kirchhoff's current law)에 의해 해당 열의 모든 전류는 합해질 수 있다.

이는 입력 벡터와 가중치 행렬의 곱이 각 열의 아날로그 전류 형태로 나타남을 의미한다. 즉, 단 한 번의 입력 벡터의 전압 인가로 병렬 연산이 가능하다는 것이다.

전통적인 폰 노이만 아키텍처에서는 이와 같은 벡터-행렬 곱셈을 수행하려면 다수의 곱셈과 덧셈을 순차적으로 처리해야 하므로 연산 시간이 급격하게 증가하지만, 저항 메모리 크로스바 어레이에서는 하드웨어 상에서 병렬로 연산을 수행하여 연산 시간을 줄일 수 있다. 즉, 메모리와 연산 유닛 사이의 데이터 이동을 최소화하여 아날로그 인메모리 컴퓨팅의 핵심을 이룬다.

그림 12. 간단한 신경망(neural network)이 크로스바 어레이에 대응될 수 있다. [9]

수식 1. 특정 열에서 벡터-헹렬 곱을 통해 얻어진 총 전류[9]

4-2. 이미지 분류에서의 저항 메모리 어레이 활용

저항 메모리 기반 아날로그 메모리 소자는 이미지 분류와 같은 추론 작업을 가속화하기 위한 소자로 연구되고 있다. 특히 합성곱 신경망(Convolutional Neural network, CNN)이나 다층 퍼셉트론(Multi-layer Perceptron, MLP) 등 많은 MAC 연산을 필요로하는 알고리즘에서, 크로스바 어레이에서의 병렬 연산이 빠른 벡터-행렬 곱셈 특성이 유용하다.

연산이 많아질수록 저전력 특성 또한 중요한데, 저항 메모리 크로스바 어레이에서 190 fJ/MAC의 에너지 소비가 일어났다고 보도된 만큼 최근 저항 메모리 하드웨어의 중요성은 더욱더 입증되고 있다

[9]. 하나의 트랜지스터-하나의 저항 메모리 셀 면적의 한계는 6 F

2 로 알려져 있어 선택 소자와 같은 호환성 문제없이 대규모 집적 어레이를 구현할 수 있어 대형 이미지 분류가 가능해진다.

저항 메모리 크로스바 어레이는 아날로그 특성을 활용하여 밝기, 그레이 스케일 등 아날로그 입력 값을 직접 처리할 수 있다는 것도 큰 장점이다. 픽셀 밝기를 전압으로 변환하여 저항 메모리 크로스바에 직접 인가함으로써, 디지털 변환 없이도 아날로그 연산을 수행할 수 있다는 방식은 여러 연구에서 입증되고 있다. 따라서 저항 메모리 크로스바 어레이는 이미지의 아날로그 값을 직접 전압 신호로 받아 병렬 인메모리 컴퓨팅을 수행함으로써, 이미지 분류에서 디지털 회로보다 좋은 에너지 효율을 가지며 고속 추론이 가능한 차세대 하드웨어 솔루션이다.

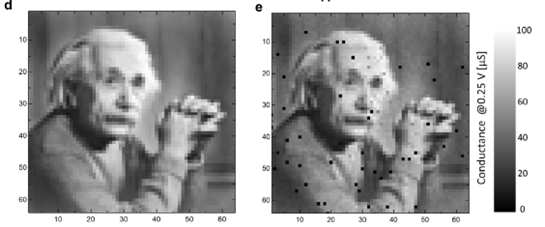

그림 13. (d) 64x64의 그레이 스케일로 양자화된 이미지의 목표 전도도 지도(map) (e) 목표 전도도로 대응된 크로스바 어레이의 전도도. [10]

그림 13의 왼쪽은 아인슈타인의 64x64 이미지의 픽셀 값에 대한 목표 전도도 지도이다. 오른쪽 그림은 실제로 대응된 결과인데 98% 이상의 셀에서 5% 이내 오차로 정밀하게 대응된 것을 볼 수 있으며, 차세대 아날로그 뉴로모픽 시스템을 위한 핵심 기술인 고집적이며 정밀한 아날로그 가중치를 구현했다고 볼 수 있다.

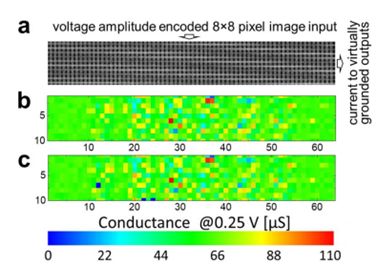

그림 14. Image 분류에 대한 실험 결과. [10]

이미지를 저항 메모리 크로스바 어레이에 아날로그 전압으로 인가하고, 크로스바 어레이에서의 벡터-행렬 곱셈 결과를 측정해 이미지 분류하는 과정이다. 사용한 신경망은 단일 계층 퍼셉트론(single layer perceptron)이다. 숫자 0~9를 분류하기 위해 출력 노드는 10개이다.

0부터 9까지의 손으로 쓴 숫자 이미지인 28x28 MNIST(Modified National Institute of Standards and Technology)를 8x8로 샘플 수 감소(down sample)를 한 후 64개의 입력 벡터로 전압을 인가하게 된다.

640개의 저항 메모리의 목표 전도도 지도이다.

실제 전도도가 조정(tuning)된 전도도 지도이다. 대부분의 셀이 5% 오차 이내로 목표 전도도에 조정된 걸 볼 수 있다.

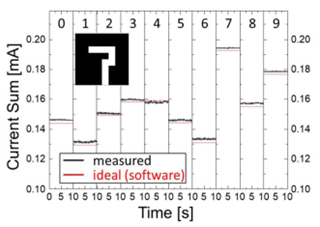

그림 15. 숫자 '7’에 대해 측정된 전류. [10]

숫자 7의 MNIST 이미지가 입력되었을 때 7번째 열에서 가장 큰 전류가 얻어진 것을 보아 이미지 분류가 성공적으로 얻어진 것을 확인할 수 있다. 이로써 저항 메모리 크로스바 어레이를 통해 실제 이미지 분류 업무에 적용이 가능한 하드웨어 플랫폼인 것이 입증되었다.

4-3. 그 외 저항 메모리 어레이 응용 분야

RF 시대에 각광받는 ‘초(超)스위치’

5G ~ 6G 무선 시스템은 수십 GHz 대역을 쓴다. 이때 신호 라우팅을 맡는 스위치에는 초고속, 저손실, 고절연이 필수다. 저항 메모리 기반 RF 스위치는 전원 없이도 상태를 유지하는 비휘발성 덕분에 저전력 특성을 갖는다.

최근 보고에 따르면 저항 메모리 스위칭 효율은 기존 비휘발성 스위치 대비 약 50배까지 향상될 수 있으며, 나노 초 미만의 전환 속도와 40 dB 이상 절연도를 동시에 달성했다. 특히 MoS₂·h-BN 단원자막(atomristor)으로 만든 RF-저항 메모리는 삽입 손실 0.2 dB 이하, 100 GHz 상위 대역까지 안정 동작을 보여 “프론트엔드 모듈의 게임 체인저”로 불린다.

[11]

‘물리적 복제 불가’한 보안 키

저항 메모리는 초기 형성·재형성 과정에서 필라멘트가 무작위로 자라며, 셀마다 고유한 저항 지문을 갖는다. 이 랜덤 변동성을 이용해 물리적 복제 불가능 함수(PUF)를 설계하면 칩마다 다른 보안 ID를 만들 수 있다. Ibrahim 등은 저항 메모리 PUF를 소자 256 개만으로 구현해 공정 변동성-내성, 저에너지 인증을 시연했다.

[12] 더 나아가 저항 메모리의 랜덤 스위칭을 아날로그 회로에 접목해 난수 발생기·카오스 암호화 소자도 연구 중이다. 서브-㎾ 전력으로 동작하는 집적형 카오스 회로가 2025년 보고됐으며, 보안 칩, 센서 네트워크 난수원으로 주목된다.

[13]

고감도 바이오센싱, 헬스케어

소형, 저전력, 비휘발성이라는 특성은 의료 현장에도 매력적이다. 영국-이란 공동 연구팀은 저항 메모리 어레이를 뉴로모픽 프로세서로 활용해 타액 시료 속 바이오 마커를 온칩에서 실시간 분류, COPD(만성 폐쇄성 폐질환) 조기 진단 정확도 89%를 달성했다. 센싱, 전처리, 추론을 하나의 칩에 통합함으로써 별도 서버-전송이 필요 없는 ‘랩-온-칩 AI’ 가능성을 열었다.

[14]

5. 결론

저항 메모리는 데이터 이동 병목과 높은 에너지 소모를 해소할 수 있는 차세대 핵심 소자로 각광받고 있다. 크로스바 어레이 구조를 이용하면 한 번의 병렬 연산으로 저전력·고속 인메모리 컴퓨팅을 구현할 수 있으며, 3차원 적층을 통해 초고집적 회로까지 확장 가능하다. 이러한 특성 덕분에 저항 메모리는 기존 비휘발성 메모리를 대체하는 것은 물론, 인공지능·뉴로모픽 연산 전용 메모리로도 무한한 잠재력을 지닌다.

물론 필라멘트 형성의 무작위성, 3D 적층으로 인한 열·신뢰성 문제 등 해결해야 할 과제도 남아 있다. 그러나 재료·공정·회로 전 계층에서 다각적인 연구가 이어지고 있어, 이러한 장벽이 해소된다면 저항 메모리는 차세대 컴퓨팅 생태계를 이끌 핵심 동력원이 될 것이다.

6. 참조문헌

[1] F. Zahoor, T. Z. A. Zulkifli, and F. A. Khanday, “Resistive Random Access Memory (RRAM): an overview of materials, 스위칭 mechanism, performance, multilevel cell (MLC) storage, modeling, and applications,” Nanoscale Research Letters, vol. 15, no. 90, pp. 1–26, 2020, doi: 10.1186/s11671-020-03299-9.

[2] “Structural and Electrical Characterization of Transition Metal Oxide-Based Memristors”, Bachelor’s Thesis, Advanced Research Lab, supervised by Prof. Dr. Lambert Alff.

[3] Y. Yang, P. Gao, S. Gaba, T. Chang, X. Pan, and W. Lu, “Observation of conducting filament growth in nanoscale resistive memories,” Nature Communications, vol. 3, no. 732, pp. 1–8, Mar. 2012, doi: 10.1038/ncomms1737.

[4] C. Wang, G. Shi, F. Qiao, R. Lin, S. Wu, and Z. Hu, “Research progress in architecture and application of RRAM with computing-in-memory,” Nanoscale Advances, vol. 5, no. 9, pp. 2492–2513, 2023, doi: 10.1039/D3NA00025G.

[5] T. Gao, J. Feng, H. Ma, and X. Zhu, “The ovonic threshold 스위칭 characteristics in SixTe₁?? based selector devices,” Applied Physics A, vol. 124, no. 10, pp. 1–7, Oct. 2018, doi: 10.1007/s00339-018-2153-9.

[6] T. P. Xiao, C. H. Bennett, B. Feinberg, S. Agarwal, and M. J. Marinella, “Analog architectures for neural network acceleration based on non-volatile memory,” Applied Physics Reviews, vol. 7, no. 3, Art. no. 031301, Jul. 2020, doi: 10.1063/1.5143815.

[7] K. Jeon, "Purely self-rectifying memristor-based passive crossbar array for artificial neural network accelerators," Nature Communications, vol. 15, no. 1, Article no. 308, Jan. 2024. doi.org/10.1038/s41467-023-44620-1

[8] K. Jeon, J. Kim, J. J. Ryu, S.-J. Yoo, C. Song, M. K. Yang, D. S. Jeong, and G. H. Kim, “Self-rectifying resistive memory in passive crossbar arrays,” Nature Communications, vol. 12, Art. no. 2968, May 2021, doi: 10.1038/s41467-021-23180-2.

[9] H. Aziza, “Image classification in memristor-based neural networks: A comparative study of software and hardware models using RRAM crossbars,” Electronics, vol. 14, no. 6, Art. no. 1125, Mar. 2025, doi: 10.3390/electronics14061125.

[10] H. Kim, M. R. Mahmoodi, H. Nili, and D. B. Strukov, “4K-memristor analog-grade passive crossbar circuit,” Nature Communications, vol. 12, Art. no. 5198, Aug. 2021, doi: 10.1038/s41467-021-25455-0.

[11] Shin-Chieh Chen, Yu-Tao Yang et al. “HfO2 Memristor-Based Flexible Radio Frequency Switches” ACS Nano 2025, 19, 1, 704–711 December 20, 2024, doi: 10.1021/acsnano.4c11846

[12] Hebatallan M. lbrahim, Heba Abunahla, Baker Mohammadm, Hoda AIKhzaimi “Memristor-based PUF for lightweight cryptographic randomness” Scientific Reports volume 12, Article no. 8633 (2022), doi : 10.1038/s41598-022-11240-6

[13] Barı? Karakaya, Arif Gülten, Mattia Frasca “A true random bit generator based on a memristive chaotic circuit: Analysis, design and FPGA implementation” Chaos, Solitons & Fractals, Volume 119, February 2019, Pages 143-149, doi : 10.1016/j.chaos.2018.12.021

[14] Pouya Soltani Zarrin, Finn Zahari, Mamathamba K. Mahadevaiah, Eduardo Perez, Hermann Kohlstedt & Christian Wenger “Neuromorphic on-chip recognition of saliva samples of COPD and healthy controls using memristive devices” Scientific Reports volume 10, Article number: 19742 (2020), doi : 10.1038/s41598-020-76823-7

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)

.png)

.png)

.png)

.png)

.png)

.png)

.png)