[연재 기고] 차세대 고밀도 디지털 전자 제품의 핵심, 다진법 기술은

2023-05-08 고려대학교 주병권 교수 연구실

다진법 (Multi-Valued Logic System) 기술의 동향

다진법(MVL, Multi-Valued Logic System) 관련 기술은 기존의 이진 논리 회로보다 더 많은 정보를 처리할 수 있어 집적 회로의 데이터 처리 능력을 향상시킬 수 있는 유망한 방법으로 많은 분야에 관심을 받으며 활발히 연구되고 있다.

다진법은 차세대 고밀도 디지털 전자 제품의 핵심 요소로 간주된다. 기존의 다진법 시스템에 대한 접근 방식은 단순히 회로 수준 설계 및 구현에 그치지만, 기술의 발전으로 인한 새로운 전자 재료 및 소자의 등장으로 인해 다진법이 회로 및 소자 간소화 등 다양한 분야의 응용의 가능성을 열었다. 이 글에서는 다진법 시스템의 개념에 대하여 설명하고, 보고된 여러 분야에 대한 최근 연구를 분류하여 살펴보고자 한다.

다진법(MVL, Multi-Valued Logic System) 관련 기술은 기존의 이진 논리 회로보다 더 많은 정보를 처리할 수 있어 집적 회로의 데이터 처리 능력을 향상시킬 수 있는 유망한 방법으로 많은 분야에 관심을 받으며 활발히 연구되고 있다.

다진법은 차세대 고밀도 디지털 전자 제품의 핵심 요소로 간주된다. 기존의 다진법 시스템에 대한 접근 방식은 단순히 회로 수준 설계 및 구현에 그치지만, 기술의 발전으로 인한 새로운 전자 재료 및 소자의 등장으로 인해 다진법이 회로 및 소자 간소화 등 다양한 분야의 응용의 가능성을 열었다. 이 글에서는 다진법 시스템의 개념에 대하여 설명하고, 보고된 여러 분야에 대한 최근 연구를 분류하여 살펴보고자 한다.

글/ 고려대학교 주병권 교수 연구실

주병권(고려대학교 전기전자공학부 교수)

한정훈(고려대학교 마이크로/나노시스템협동과정 석박사통합 과정)

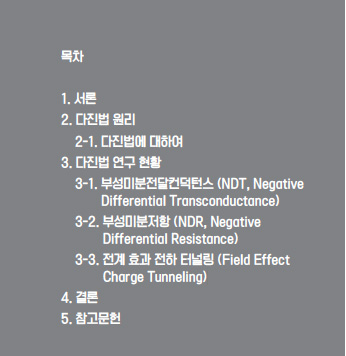

1. 서론

디지털 전자 공학의 특징은 확연한 분리된 정보를 사용하는 것이며, 이는 단순하고 신호 전달 중 오류 발생에 대한 우수한 내구성을 제공하여 하드웨어 구현에 있어 적합하다.

이러한 디지털 시스템을 구축하는 가장 간단한 방법은 두 개의 개별 데이터(“0”과 “1”)만 이용하여 처리하는 것이며, 이 '이진법' 논리 시스템은 현대 전자 산업과 우리의 일상 생활에 혁명을 가져왔다.

그러나 보다 소형의 전자 회로 및 제품에 대한 수요가 계속 증가함에 따라 단일 논리 게이트 또는 동일한 물리적 면적에서 더 큰 정보 처리 성능이 요구되기 때문에 다진법 로직을 실현하여 허용 가능한 데이터 레벨을 증가시키는 것은 점점 더 많은 관심을 받고 있다[1].

새로운 재료를 이용한 다진법 방식의 구현은 지난 몇 년 동안 극적인 진전을 보였다[2]. 다진법 연구에 있어 고전적인 회로는 가치 있는 전략으로 남아 있지만, 차세대 반도체 및 나노 재료의 특수 정렬 및 활용에 기반한 이러한 새로운 개념은 다진법 시스템의 적용 분야를 크게 확대할 것으로 예상한다. 대면적 저온 공정, 구조 제어, 기계적 유연성, 인터페이스 감도 등이 이러한 재료가 제공하는 다양한 이점이다.

다진법은 아직은 미지의 영역으로 명확하게 확립되거나 표준화된 프로토콜이 없기 때문에 다양한 재료 활용 및 구조가 활발하게 연구되고 있다. 이 글에서는 대표적인 소자의 구조적 특성과 작동 메커니즘에 따라 체계적으로 분류하고, 각각에 대해 알아보고자 한다.

2. 다진법 원리

2-1. 다진법에 대하여

이진법은 어떤 전기적 회로, 소자 등에서 두개(“0”, “1”)의 신호를 이용하여 연산을 하는 방법이다. 이에 반해 다진법은 세 개, 혹은 그 이상의 데이터 값을 이용하는 방법을 말한다.

예를 들면, 일반 시모스(CMOS, complementary metal-oxide semiconductor) 인버터(inverter)는 인가된 전압(VIN, input voltage)이 변동됨에 따라 출력 전압(VOUT, output voltage)에 따른 로직 값은 두 값으로 정해진다[2]. 반면 다진법 소자의 경우 출력 로직이 세 개 혹은 그 이상의 값으로 정해진다. 이를 연산해 보면 지배적으로 사용되던 이진법이었던 불 연산(Boolean logic)과는 대조되는 것을 확인할 수 있다.

어떤 진법에 해당하는 숫자를 n이라고 가정했을 때, 숫자 체계에서 n이 작아질수록 숫자 구분이 단순화되므로 계산 과정이 간단해지고 오류의 확률도 확연히 낮아진다. 따라서 이와 같은 이유로 “0”과 “1”으로 연산하는 이진법은 현재 대부분의 로직 시스템을 지배하고 있다. 하지만 이의 경우 숫자 밀도가 낮기 때문에 연산이 길어지는 단점이 있다. 로직 숫자를 의미했던 n을 늘리면, 연산 밀도가 기하급수적으로 높아지며 상당히 많은 정보를 더 적은 숫자로 표현하게 되어 연산의 간소화가 가능하다.

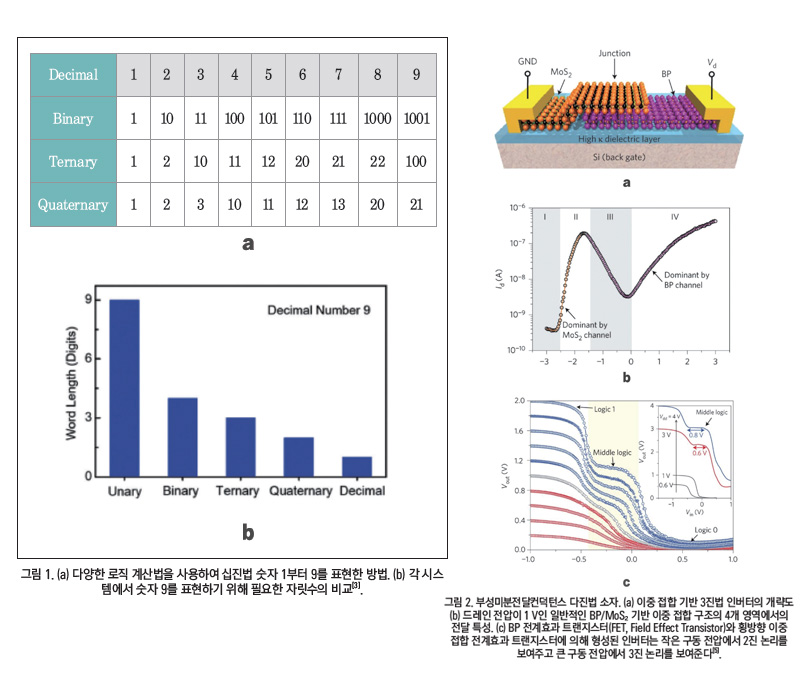

그림 1 (a), (b) 숫자 9를 예를 들면, 1진법(n=1) 또는 이진법(n=2)에서 3진법(n=3) 또는 4진법(n=4)으로 전환할수록 50% 이상의 숫자 크기의 감소가 발생하는 것을 확인할 수 있고 이는 다진법의 장점을 보여주고 있다. 하지만 위에 언급했듯이 n이 커질수록 회로의 노이즈 마진(noise margin)이 줄어드는 단점이 있다.

따라서 로직 진법이 높아질수록 노이즈 마진을 정확하게 계산하여 제어하는 것이 중요하다.

3. 다진법 연구 현황

3-1. 부성미분전달컨덕턴스 (NDT, Negative Differential Transconductance)

이중 접합 (Heterojunction) 트랜지스터는 채널에 두가지 재료를 이용하여 소스(Source)와 드레인(Drain) 사이에 접합을 해 놓은 차세대 구조이다[4]. 이러한 이중 접합 구조에서는 보편적인 트랜지스터 특51성과는 다른 특성이 발견되는데 그 중 하나는 부성미분전달컨덕턴스 현상이다.

소자의 컨덕턴스는 드레인 전압의 변화량을 게이트 전압의 변화량으로 나눈 값으로, 보통 양의 값을 갖는다. 하지만 이중 접합 소자에서는 컨덕턴스가 음의 값을 갖는 현상을 확인할 수 있다. 이는 게이트 전압이 증가 혹은 감소할 때 드레인 전압이 반대로 감소 혹은 증가하는 현상이다. 마치 n-형 소자가 p-형처럼, 혹은 그 반대로의 특성을 갖는 것이다.

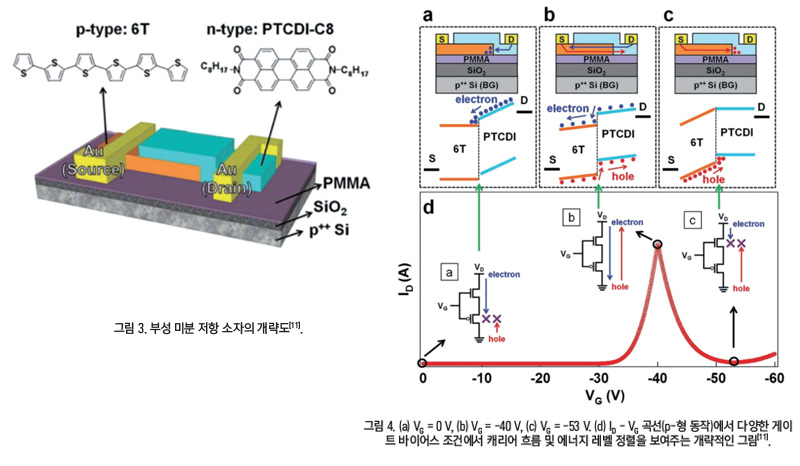

2017년, Huang 그 외 등은 부성 미분 전달컨덕턴스 특성을 보여주는 반 데르 발스(Van der Walls) 이중 접합 구조를 소개했다[5]. 이 저자들은 n-형 2D 물질인 이황화 몰리브덴(MoS₂)과 홀 지배적인 양극성(ambipolar) 수송 특성을 갖는 2D 물질인 흑린(BP, Black Phosphorus)을 반 데르 발스 이중 접합하였다(그림 2a). 전자는 소스로부터 주입되어 이황화몰리브덴 채널, 이중 접합 및 흑린 채널을 통해 드레인 전극으로 이동한다.

그림 2b에는 이 소자의 전달 특성을 4개의 구간으로 나눠서 나타내고 있다. 영역 I (게이트 전압 Vg < -2.5 V)의 경우 이황화몰리브덴 채널이 완전히 공핍되어 전체 채널이 꺼지고 가장 작은 드레인 전류 Id가 생성된다.

영역 II (-2.5 V < Vg < -1.5 V)에서 게이트 바이어스는 중첩되지 않은 이황화몰리브덴 채널 영역과 이중 접합부의 이황화몰리브덴 영역 모두에서 열리기 시작한다. 영역 III (-1.5V < Vg < 0V)에서 이중 접합이 완전히 켜지면 드레인 전류는 중첩되지 않은 흑린 및 이황화 몰리브덴 트랜지스터에 의해 지배되며, 여기서 공핍된 흑린 채널의 전류는 이황화 몰리브덴의 증가보다 더 빠르게 감소하기 시작한다. 양극 전환 지점인 Vg = 0 V에 도달하면 두 채널의 전류가 모두 증가하기 시작한다.

작은 드레인 바이어스에서 이중 접합부와 흑린 트랜지스터의 전달 특성은 게이트 전압 의존성이 큼으로 전압에 따라 차이가 크게 분산된다. 결과적으로, 좁은 밴드 간격인 흑린이 작은 VD일 때 이황화몰리브덴으로 충분한 양의 정공(hole) 주입을 제공하지 않기 때문에 이중 접합 전계효과 트랜지스터는 대부분 n-형 장치로 작동하는 반면 Vd를 증가시키면, 정공 장벽(hole barrier)을 극복하기 위한 강력한 에너지 이동을 동반하여 p-형의 특성이 나타나게 되고, 명확한 부성 미분 전달컨덕턴스 체제를 나타낸다.

3-3-2. 부성 미분 저항(NDR, Negative Differential Resistance)

3-3-2. 부성 미분 저항(NDR, Negative Differential Resistance)부성 미분 저항은 저항 값이 음의 값을 갖는 현상을 말하며, 바이어스 전압이 증가함에 따라 전류가 감소하는 비선형 캐리어(carrier) 전송 현상이다. 1958년 Leo Esaki에 의해 공진 터널(tunnel) 다이오드가 획기적으로 발명된 이래, 부성미분저항은 테라헤르츠 주파수에서 작동하는 고주파 발전기, 정적 랜덤 액세스 메모리, 고속 스위치, 다중값 논리 회로와 같은 기능적 기능 회로에서 사용되고 있다[6-10].

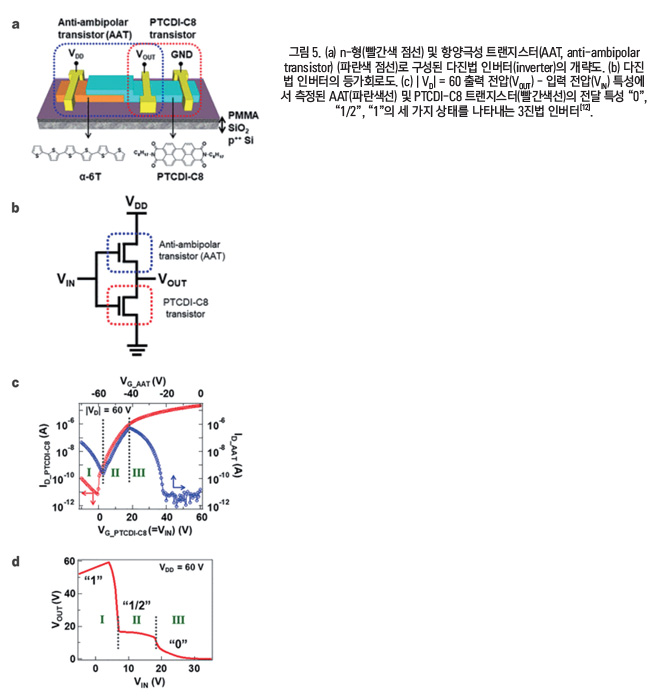

2017년, Kazuyoshi Kobashi 그 외 등은 높은 고저간(peak to valley) 성능을 나타나는 부성미분저항을 이용한 이중 접합 소자를 제시하였다[11].

이 소자는 p-형 및 n-형 유기막이 부분적으로 중첩된 영역으로 적층 된 것을 특징으로 하고 있다. 이 스태거드(staggered) 구성을 통해 p-n 이중 접합부를 가로지르는 캐리어의 이동을 모니터링할 수 있다.

p-형과 n-형 반도체로 각각 α-sexithopene(6T)과 N'-n'-dioctyl-3,4,9,10-perylenidic carboximide(PTCDI-C8)를 사용했다. 이 분자들은 층별 적층(layer by layer stacking)으로 2D 박막을 형성했고, 각 층의 분자들은 수직 방향으로 정밀하게 정렬되었다.

그림 4a-c는 p-형 작동에서 캐리어 흐름을 설명하는 개략적인 장치 그림과 에너지 레벨 다이어그램을 보여준다. 게이트 바이어스 전압은 초기 상태에서 (a) 0 V, (b) 피크 전류 위치에서 -40 V, (c) -53 V이다.

보다 VD와 VG의 차이 (VDG)가 우세하다. 결과적으로, 전위의 기울기가 유도되고 VDG에 의해 드레인 전극으로부터 전자가 주입되기 때문에 PTCDI-C8층은 전도성을 띄게 된다. ////

그림 5 a-b는 이러한 부성미분저항 특성을 이용하여 설계 한 다진법 인버터의 계략도와 등가회로도이다. 그림 5 a-c의 파란색 표시된 부분은 다진법 소자에 대한 정보, 빨간색 부분은 일반 n형 소자에 대한 정보이다.

일반적인 시모스 인버터는 VIN과 VOUT 사이에 반대되는 두 소자 (예를 들면 n-형과 p-형)로 구성이 되 있어 입력 값과 출력 값이 두 값 이상의 가지 수를 가질 수 없다[13].

반면에 그림 5c를 보면 인버터의 출력이 구간 1-3으로 동작 구간이 나뉘어져 있는 것을 확인할 수 있다. 음의 VIN 값을 가지는 구간 1부터 살펴보면, n-형 소자는 꺼져 있는(off) 상태, p-형 동작하는 다진법 소자는 켜져 있는(on) 상태이다. 이렇게 되면 그림 5b에서 VIN은 다진법 소자의 ID가 n-형 소자보다 월등히 크므로 VOUT으로 원활하게 흐를 수 있다.

또한, VIN 값이 매우 작은 경우 이 둘의 차이의 변화량은 작기 때문에 VOUT의 변화량도 비교적 작은 수치를 보여주고 있다. VIN이 점점 증가하면서 n-형 소자가 on 상태가 된 직후에 다진법 소자도 부성 미분 저항 특성을 보이면서 ID가 급격히 증가하는 것을 볼 수 있다. 이 때, 각각 증가양이 유사하여 인버터의 VOUT 값이 일정하게 유지되고 이것이 구간 2가 된다.

마지막으로 구간 3은 n-형 소자는 변함이 없는 반면에, 다진법 소자가 다시 꺼진 상태가 되어 ID가 급격히 줄어드는 구간이다. 이 때, 인버터를 보면 다진법 소자가 off 상태로 가기 때문에, VIN이 전부 다 접지(GND, ground)로 흘러 3번째 상태를 나타내는 것을 확인할 수 있다.

3-

3-3-3. 전계 효과 전하 터널링 (Field Effect Charge Tunneling)

전계 효과 터널링을 이용한 다진법 소자는 전계 효과 전하 이동(field effect charge transport)과 전계 효과 전하 터널링이 VG에 따라 연속적으로 일어나면서 두개의 구별되고 연속적인 문턱전압(threshold voltage) 값을 갖게 해 준다. 위에 소개된 방식보다 간단하게 제작이 가능하고 효과적이며, 미세 조정이 용이하다는 장점을 갖고 있다.

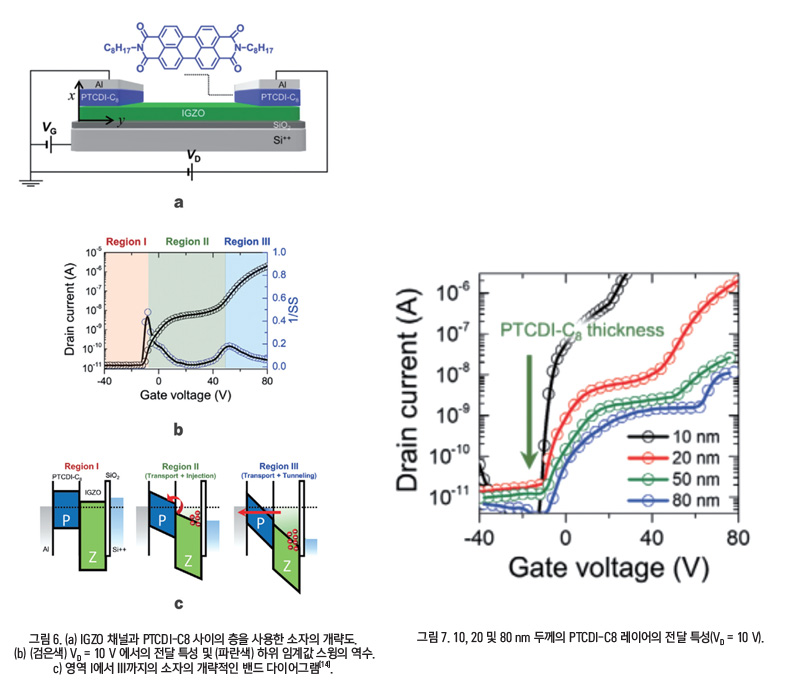

2021년, Dong Un Lim 그 외 등은 n-형 반도체인 IGZO (Indium-Gallium-Zinc-Oxide)와 PTCDI-C8의 이중 접합을 이용한 다진법 소자를 제시하였다[14].

이 소자는 안정적인 다진법 전기적 특성을 나타내기 위하여 기존 IGZO 채널 위에 추가적으로 PTCDI-C8 층을 추가하여 이 둘 사이의 이중 접합 계면을 형성하였다(그림 6a). 그림 6b에는 VG가 ?40 V 이하일 때 꺼져 있는 상태로 시작하여 (영역 I) 약 ?10 V 일 때 ID가 급격하게 증가하는 것을 확인할 수 있다(영역 II). 이는 주요 채널인 IGZO 채널이 1차적으로 작동하기 때문이다.

이때 PTCDI-C8 채널은 작동하고 있지 않는 상태이다. VG가 커질수록 포화(saturation) 상태로 수렴하다가, VG가 약 40 V에 도달하면 두 번째로 트랜지스터가 작동한다(영역 III). 이 구간은 IGZO 채널과 PTCDI-C8 채널이 모두 켜져 있는 상태이며 이 때 전하의 수송과 터널링이 모두 일어나게 된다. 결과적으로, 총 두 개의 문턱전압이 존재하는 것을 확인할 수 있다.

그림 7은 IGZO 채널 위 PTCDI-C8 채널의 두께를 다양하게 증착한 소자의 전달 특성이다. 첫 번째 소자가 켜지는 전압(VON) 값은 비슷하게 약 ?15 V에 위치하지만, PTCDI-C8 층이 얇은 소자는 더 높은 드레인 전류와 더 낮은 두 번째 VON을 보인다. 이것은 PTCDI-C8 층이 얇을수록 터널링이 발생할 확률이 더 높고, IGZO 층에서 ID가 포화된 직후에 전체 채널이 더 낮은 VG에서 완전히 꺼지기 때문이다.

10-nm 두께의 PTCDI-C8 층을 가진 장치와 달리, 20-nm 및 80-nm 두께의 PTCDI-C8 층을 가진 장치는 첫 번째 VON과 두 번째 VON 사이의 명백한 중간 상태를 나타낸다.

4. 결론

이진법을 뛰어넘기 위한 연구는 지난 몇 년 동안 다양한 연구 분야에서 꾸준하게 진행되었고 발전해왔다. 특히, 다진법을 활용55하면 회로의 밀도가 기하급수적으로 높아져 같은 면적에 처리할 수 있는 데이터의 양이 월등하게 높아지며, 이런 특성으로 인해 차세대 고밀도 전자 제품의 필수 기술로 평가받고 있다.

이 글에서는 다진법 소자의 개념에 대해 소개하고, 여러 방법과 재료를 이용한 다양한 기술에 대해 다루어 보았다. 다진법 기술은 아직 초기 단계이며 근본적인 핵심 기술에 대한 이해도는 여전히 발전의 여지가 남아있다.

재료의 선택, 접합 시 재료간 상호 작용, 박막 정보 등은 최종 소자의 특성에 영향을 많이 가해지는 것으로 알려져 있다. 다진법 소자가 일반 이진법 소자만큼 안정성이 향상된다면, 전 세계의 모든 전자기기에 새로운 패러다임이 열릴 수 있다고 기대해 본다.

5. 참고문헌

[1] Wakayama, Yutaka, and Ryoma Hayakawa. “Antiambipolar transistor: A newcomer for future flexible electronics.” Advanced Functional Materials 30.20 (2020): 1903724.

[2] Na, M. H., et al. “The effective drive current in CMOS inverters.” Digest. International Electron Devices Meeting,. IEEE, 2002.

[3] Yoo, Hocheon, and Chang-Hyun Kim. “Multi-valued logic system: New opportunities from emerging materials and devices.” Journal of Materials Chemistry C 9.12 (2021): 4092-4104.

[4] Yoo, Hocheon, et al. “Heterojunction Transistors: Negative Trans conductance Heterojunction Organic Transistors and their Application to Full?Swing Ternary Circuits (Adv. Mater. 29/2019).” Advanced Materials 31.29 (2019): 1970206.

[5] Huang, Mingqiang, et al. “Multifunctional high-performance van der Waals heterostructures.” Nature nanotechnology 12.12 (2017): 1148-1154.

[6] L. Esaki, Phys. Rev. 1958, 109, 603.

[7] S. Bhattacharyya, S. J. Henley, E. Mendoza, L. Gomez-Rojas, J. Allam, S. R. P. Silva, Nat. Mater. 2006, 5, 19.

[8] E. Alekseev, D. Pavlidis, Solid State Electron. 2000, 44, 941.

[9] J. P. A. Van Der Wagt, Proc. IEEE 1999, 87, 571.

[10] K. Ismail, W. Chu, A. Yen, D. A. Antoniadis, H. I. Smith, Appl. Phys. Lett. 1989, 54, 460. [1] L. E. Brus, J. Chem. Phys., 79, p5566, (1983)

[11] Kobashi, Kazuyoshi, et al. “Negative differential resistance transistor with organic p?n heterojunction.” Advanced Electronic Materials 3.8 (2017): 1700106.

[12] Kobashi, Kazuyoshi, et al. “Multi-valued logic circuits based on organic anti-ambipolar transistors.” Nano letters 18.7 (2018): 4355-4359.

[13] Bae, Woorham. “CMOS inverter as analog circuit: An overview.” Journal of Low Power Electronics and Applications 9.3 (2019): 26.

[14] Lim, Dong Un, et al. “Multi?State Heterojunction Transistors Based on Field?Effect Tunneling?Transport Transitions.” Advanced Materials 33.29 (2021): 2101243.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

본 기사의 전문은 PDF문서로 제공합니다.

(로그인필요)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

100자평 쓰기