많은 기존 ISP가 2개의 센서 출력을 처리할 수 있다. 핵심 문제는 알맞은 포맷으로 알맞은 버스를 통해 이미지들을 동기화하여 수신하는 것이다. 가장 비용 효과적인 설계 솔루션은 소형 FPGA와 프레임 버퍼 메모리를 사용하는 것이다. Lattice MachXO2와 같은 저비용 FPGA와 저가 LP SDRAM 디바이스를 활용함으로써 2개의 이미지 센서를 ISP에 연결할 수 있다.

많은 기존 ISP가 2개의 센서 출력을 처리할 수 있다. 핵심 문제는 알맞은 포맷으로 알맞은 버스를 통해 이미지들을 동기화하여 수신하는 것이다. 가장 비용 효과적인 설계 솔루션은 소형 FPGA와 프레임 버퍼 메모리를 사용하는 것이다. Lattice MachXO2와 같은 저비용 FPGA와 저가 LP SDRAM 디바이스를 활용함으로써 2개의 이미지 센서를 ISP에 연결할 수 있다.

2개의 이미지 센서를 사용하는 애플리케이션을 떠올려 보면, 첫 번째로 3D 카메라가 떠오를 것이다. 하지만, 2개의 이미지 센서로부터 제공되는 데이터를 사용하여 개선할 수 있는 설계는 매우 다양하다. 한 예로 일반적으로 백미러 부근에 설치되며 2개의 카메라를 통합하고 있는 차량용 블랙박스(Black Box Car Driver Recorder)를 들 수 있다(그림 1). 1개의 카메라는 전면 유리를 향하고 다른 카메라는 운전자를 향한다. 카메라 영상은 로컬 메모리 칩에 저장되고, 사고나 분쟁이 발생하면 검색할 수 있다.

2개의 카메라와 그 데이터를 사용하는 다른 애플리케이션으로는 차량을 위한 감시 및 보행자 감지를 위한 정밀 분석기가 있다. 이러한 설계의 경우, 2개의 카메라에서 제공되는 출력을 사용하여 거리 지각(depth perception) 등과 같은 알고리즘을 생성할 수 있다. 이러한 데이터를 이용하여 프로세서는 매우 정확하게 이미지를 “판독”하여 어둠 속의 사람이나 그 외 다른 대상들을 포착할 수 있다.

이러한 설계들은 모두 이미지 신호 프로세서(Image Signal Processor ,ISP)를 필요로 한다. 하지만, ISP에 대해 2개의 센서를 지원하는 것은 그리 간단치 않다. 대부분의 ISP가 2개의 이미지 센서 출력을 지원할 수 있지만, 대다수 ISP 디바이스들이 단지 1개의 센서와 인터페이스 할 수 있도록 설계돼 있다. 심지어 2개의 포트를 가지고 있는 ISP도 2개의 이미지를 통합하여 처리할 수 없거나, 할 수 있더라도 비용이 매우 높아지는 경향이 있다.

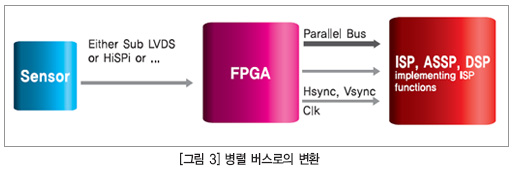

단지 1개의 이미지 센서만을 처리하도록 ISP 인터페이스가 제한되어 있을 뿐만 아니라, 이미지 센서의 해상도가 높아짐에 따라 또 다른 설계 과제가 부과된다. 역사적으로 720p30 해상도까지의 이미지 센서들 모두 단일 CMOS 병렬 버스를 통해 ISP에 연결된다(그림 2).

720p60 이상의 해상도에서 이미지 센서는 CMOS 병렬 버스를 통해 수용 가능한 품질로 전송을 할 수 없다. 병렬 버스 속도가 70 MHz 이상이어야 하기 때문에, 스위칭 잡음이 이미지 센서의 품질을 저하시키는 원인이 될 수 있다. 이러한 문제를 극복하기 위해서 이미지 센서 공급업체들이 데이터를 전송하는 데 병렬 버스 대신 직렬 버스를 도입하고 있다. 하지만, 많은 ISP 디바이스들이 병렬 버스용으로만 설계돼 있기 때문에 새로운 센서 직렬 버스를 이러한 병렬 버스로 변환해야만 한다(그림 3).

마지막으로 3D 알고리즘을 요구하는 애플리케이션의 경우에는 2개의 이미지 센서가 반드시 동기화되어야만 한다. 이것 역시 간단치 않은 데, 각 센서 제조업체들이 자체적인 방법론과 포맷을 사용하고 있기 때문이다. 예를 들어, 일부 이미지 센서는 트리거(triggering)를 위해 I/O 핀을 사용하지만, 다른 이미지 센서들은 I 2C 또는 SPI를 사용하거나 이 둘을 조합하여 사용하기 때문이다. 사실상 모든 ISP는 다양한 센서들이 동기화되도록 보장하기 위해서 다중 모드를 지원해야 한다는 설계 과제에 직면해 있다.

일부 ISP 공급업체들은 2개의 독립적인 인터페이스와 2개의 처리 엔진을 제공함으로써 2개의 이미지 센서를 지원하는 문제를 해결하려고 시도해 왔다. 하지만, 결과적으로 필요한 것보다 높은 이미지 성능을 포함해야 하기 때문에, ISP 디바이스의 비용이 매우 높아졌을 뿐만 아니라, 소프트웨어 개발자들이 설정하고 프로그램하는 것 역시 매우 복잡해졌다.

이러한 모든 듀얼 이미지 센서 관련 기술과제들을 2개의 센서를 정확하게 형식화할 수 있도록 지원하고 이들을 동기화하여 데이터를 ISP에 전송하기 전에 이를 올바른 포맷으로 통합한다면 극복할 수 있다.

앞서 언급한 바와 같이 많은 기존 ISP들이 2개의 센서 출력을 처리할 수 있다. 핵심 문제는 알맞은 포맷으로 알맞은 버스를 통해 이미지들을 동기화하여 수신하는 것이다. 가장 비용 효과적인 설계 솔루션은 소형 FPGA와 프레임 버퍼 메모리를 사용하는 것이다.

그림 4는 ISP에 적합한 포맷을 동기화하고 통합하여 출력하는 비용 효과적인 솔루션을 나타낸 것이다. Lattice MachXO2와 같은 저비용 FPGA와 저가 LP SDRAM 디바이스를 활용함으로써 2개의 이미지 센서를 ISP에 연결할 수 있다. FPGA 설계는 다음과 같은 성능들을 통합해야 한다. 우선 ISP를 통한 I 2C 또는 SPI 레지스터 구성 설정과 인터페이스 해야 한다. 이러한 구성 설정은 두 센서 모두 동일하다. 다음으로 FPGA는 직렬 구성 데이터(I 2C 또는 SPI)를 두 센서 모두에 전송하고 이들이 알맞게 구성되도록 보장해야만 한다. 이때 2개의 센서가 모두 동일하게 설정될 수 있지만, 여전히 동기화되어야만 한다. MachXO2 FPGA의 유연성이 특정 센서 제조업체 각각을 위해 필요한 독창적인 제어 기능을 구현할 수 있도록 지원한다. 각 센서를 구동하는 클록이 정확히 동일하도록 보장하기 위해서 FPGA가 두 센서에 대한 클록을 출력한다. 두 센서가 설정되고 동기화되면, 두 센서 모두가 이미지 데이터를 전송하기 시작한다.

다음으로 FPGA가 I/O 셀과 로직 패브릭의 고속 시리얼 이미지 데이터를 디시리얼라이즈(de-serialize)해야만 센서 데이터 스트림을 병렬 포맷으로 변환할 수 있다. 다음으로 MachXO2 FPGA가 알맞은 제어 문자(control character)를 찾아야만 각 센서의 프레임 시작과 라인의 시작을 인식할 수 있다. 이것은 일반적으로 제어 문자 또는 명령어 시퀀스를 찾음으로써 수행된다. 일단 센서 이미지 데이터가 감지되면 다음으로 FPGA가 로우(raw) 이미지 데이터를 추출하고 프레임을 저장하기 위해서 저전력 SDRAM 메모리를 사용하기 시작한다. 물론 이미지 데이터를 알맞게 판독하고 작성하기 위해서 FPGA 내에 LP SDRAM 메모리 컨트롤러가 필요하다. FPGA가 수행하는 다음 기능은 요구되는 출력 포맷으로 프레임을 정렬하는 것이다. 예를 들어, 일반적으로 사용되고 있는 포맷 중 하나가 톱 바텀 구성(top bottom configuration )이며, 다른 하나는 사이드-바이-사이드(side by side) 구성이다.

통합 센서 데이터를 전송하기 위해서는 FPGA의 센서 데이터가 바이에르(Bayer) 패턴 이미지 포맷으로 변환되어야만 한다. 이를 통해 정확한 RGB 색상이 ISP에 전달된다. 정확한 이미지와 알려진 출력 포맷 설정을 통해 MachXO2 FPGA는 병렬 버스의 형식화된 데이터를 ISP로 출력한다. 이전 프레임이 출력되고 있기 때문에 다음 프레임들을 버퍼링하는 데 외부 LP SDRAM를 사용한다. 일반적으로 LP SDRAM이 IPS에 대한 출력 클록만큼 빠르게 두 번 실행된다. ISP가 데이터를 판독하고 인식하도록 보장하기 위해서 FPGA 출력은 병렬 이미지 센서 출력을 모방할 수 있도록 설계돼 있다. 즉, FPGA가 클록, 유효 프레임, 유효 라인, 그리고 일반적으로 ISP에 대한 12 bit 데이터 버스를 생성한다.

이 설계는 래티스 반도체와 앱티나(Aptina)에 의해 이미 구현됐다. Lattice MachXO2와 2개의 Aptina 9MT024 이미지 센서를 사용하기 때문에 설계는 사실상 모든 ISP가 수용할 수 있는 매우 비용 효과적인 솔루션이다. 센서를 구성하고 동기화하고 출력 이미지 데이터를 알맞게 형식화는 데 필요한 모든 주요 기능들이 수행된다. 이 설계에 대한 보다 자세한 정보는 다음 사이트에서 확인할 수 있다. www.latticesemi.com/dualsensorbridge.

래티스|PLD 제품 최단 기간 100만 개 출하 래티스 반도체는 작년 12월 MachXO2 PLD의 전체 제품군을 생산 출시한 이후, 지난 3월까지 100만개 이상을 출하했다고 발표했다. 100만 개 출하 기록은 이 제품이 회사 역사상 가장 빠르게 소비자들에게 채택 받았다는 것을 의미한다. 100만 개 출하기록은 MachXO2 제품군이 생산 출시된 지, 4개월도 미치지 않는 기간이다. MachXO2 제품은 고객에게 ▲임베디드 플래시 기술 ▲사용 편의성 ▲유연성 ▲시스템 통합력 ▲저렴한 가격을 제공하여, 가전이나 통신 등의 다양한 분야에서 이용되고 있다. 래티스의 전략 마케팅 담당 이사인 샤킬 피이라(Shakeel Peera)는 “이처럼 짧은 시간에 100만 개가 넘는 디바이스를 출하했다는 것은 MachXO2 PLD가 획기적인 MachXO 제품군의 훌륭한 승계자라는 것을 증명한다”고 말했다. 래티스 반도체는 작년 12월 MachXO2 PLD의 전체 제품군을 생산 출시한 이후, 지난 3월까지 100만개 이상을 출하했다고 발표했다. 100만 개 출하 기록은 이 제품이 회사 역사상 가장 빠르게 소비자들에게 채택 받았다는 것을 의미한다. 100만 개 출하기록은 MachXO2 제품군이 생산 출시된 지, 4개월도 미치지 않는 기간이다. MachXO2 제품은 고객에게 ▲임베디드 플래시 기술 ▲사용 편의성 ▲유연성 ▲시스템 통합력 ▲저렴한 가격을 제공하여, 가전이나 통신 등의 다양한 분야에서 이용되고 있다. 래티스의 전략 마케팅 담당 이사인 샤킬 피이라(Shakeel Peera)는 “이처럼 짧은 시간에 100만 개가 넘는 디바이스를 출하했다는 것은 MachXO2 PLD가 획기적인 MachXO 제품군의 훌륭한 승계자라는 것을 증명한다”고 말했다. |

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>