모바일 기술이 새로운 애플리케이션으로 지속적으로 확대됨에 따라 모바일 관련 제품 설계자는 브리징 기술을 활용할 필요가 있다.

20여 년 전 임베디드 설계자들은 비용을 절감하기 위해 당시 대량의 광범위한 PC 아키텍처에 시선을 돌렸다. 임베디드 설계자들은 원래 PC 아키텍처를 위해 설계된 하드웨어와 소프트웨어로 전환함으로써 수백만 컨슈머 애플리케이션에서 이미 입증된 높은 신뢰성을 갖는 부품을 사용하여 개발 비용을 낮출 수 있었다. PC 버스는 전문적인 임베디드 애플리케이션에 매우 매력적인 저렴한 대안을 제공했다.

동시에 이를 통해 개발자는 다양한 업체에서 제공하는 사용이 편리한 설계 툴과 오픈 소스 운영 시스템들을 매우 익숙한 하드웨어 아키텍처에서 이용할 수 있게 됐다. 또한 PC 아키텍처로 마이그레이션함으로써 임베디드 설계자는 개발 사이클을 단축시킬 수 있었을 뿐 아니라 비용 절감의 혜택을 고객에게 제공할 수 있었다.

현재, PC 아키텍처는 더 이상 과거와 같이 대규모로 이용되지 않는다. 오늘날의 임베디드 시스템 개발자는 대규모 컨슈머 시장의 비용 편익을 이용하기 원할 때 스마트폰 시장에 시선을 돌린다. 매년 수십억 대의 스마트폰이 판매되는 가운데 다양한 분야의 설계자들은 오늘날 모바일 솔루션에 사용되는 주요 부품의 높은 성능과 낮은 가격을 이용하는 방법을 찾고 있다. 20년 전 PC 아키텍처와 마찬가지로 모바일 시장은 경쟁이 치열한 컨슈머 시장에서 성능이 입증된 익숙한 하드웨어 아키텍처와 애플리케이션을 제공한다.

핵심적인 표준 세트

현재 세대 휴대용 기기의 설계를 구동하는 것은 MIPI 얼라이언스(MIPI Alliance)에 의해 정의된 인터페이스와 버스이다. 2003년에 설립된 MIPI 얼라이언스는 모바일 및 모바일 관련 기기를 위한 포괄적인 일련의 규격들을 개발하기 위해 구성되었다. 협회의 목적은 디바이스 제조사가 혁신적인 모바일 제품을 개발하면서 제품 출시 기간을 단축하고 비용을 낮추는 데 필요로 하는 하드웨어 및 소프트웨어 인터페이스 규격을 제공하는데 있다. MIPI 얼라이언스는 핵심적인 표준 세트를 개발함으로써 모바일 기기 제조업체들이 다양한 벤더의 부품들을 소싱하고 설계 성능을 손쉽게 최적화할 수 있게 했다.

현재 MIPI 얼라이언스는 4개 사에서 수백 개 회원사로 성장했으며, 스마트폰 업계에서 확고한 명성을 유지하고 있다. 모든 주요 칩 제조사는 MIPI 얼라이언스 규격을 사용하며, 모든 스마트폰은 최소한 하나의 MIPI 얼라이언스 규격을 사용한다.

.jpg)

광범위한 영향

그러나 MIPI 얼라이언스의 영향력은 모바일 업계 너머까지 미친다. 모바일 커넥티비티가 일상의 모든 측면에 확산되면서 점점 더 많은 산업이 모바일 기술을 설계에 이용하려고 하지만, 적지 않은 장애에 부딪히고 있다. 많은 임베디드 시스템에 사용되는 카메라와 디스플레이는 현재 모바일 애플리케이션 프로세서(AP)에 사용되는 인터페이스 유형이나 수와 일치하지 않는다.

임베디드 설계자가 MIPI 시장에서 이용할 수 있는 가장 일반적인 부품은 애플리케이션 프로세서(AP)와 이미지 센서, 디스플레이이다. 현재 많은 모바일 설계는 디스플레이에 MIPI DSI(Display Serial Interface)를 사용하고, 이미지 센서에는 MIPI CSI-2(Camera Serial Interface)를 사용한다. DSI와 CSI-2는 둘 다 D-PHY 물리적 버스를 기반으로 한다. 1개의 차동 클럭과 1 ~ 4개의 차동 데이터 라인을 갖는 D-PHY 는 중앙 정렬, 소스 동기 인터페이스로 상승 및 하강 에지에서 모두 클럭킹된다. D-PHY의 고유 특징 중 하나는 차동 시그널링에서 단일 종단 시그널링(Single-Ended Signal)으로 ‘즉시’ 변경할 수 있다는 것이다.

임베디드 시장의 설계자가 대부분 레거시나 독자적인 디스플레이와 이미지 센서를 이용하는 설계에서 MIPI 시장의 수많은 이점을 이용하려면 어떻게 해야 할까? 산업용 시장을 예로 들어보자. 전통적인 임베디드 애플리케이션 설계자는 LVDS, RGB 또는 SPI 인터페이스를 사용하는 디스플레이에 의존해 왔다. 대부분의 임베디드 프로세서는 DSI 인터페이스를 포함하고 있지 않다.

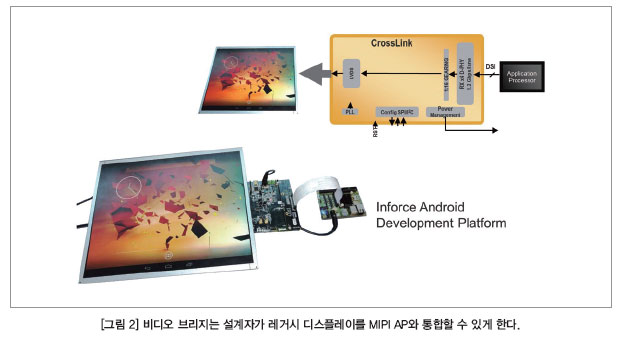

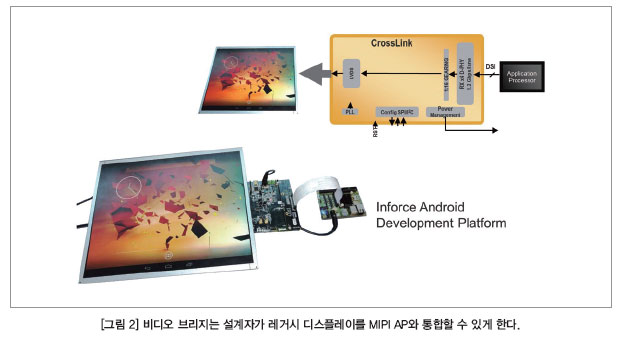

MIPI 프로세서와 애플리케이션을 이용하면서 전통적인 LVDS 디스플레이를 유지하고자 하는 산업 디자이너는 LVDS 디스플레이와 MIPI 지원 AP를 연결시켜주는 브리지를 필요로 한다. 이러한 문제를 해결하는 한 가지 방법은 OpenDSI, LVDS 또는 독자적인 인터페이스로부터 MIPI DSI로 변환시켜주는 비디오 브리지를 구성하는 것이다 (그림 2 참조).

마찬가지로 산업용 시장의 많은 설계자들은 최신 세대의 모바일 프로세서와 애플리케이션을 이용하면서 CMOS 카메라를 계속 사용하고 싶어한다. (그림 3)은 설계자가 어떻게 레거시 CMOS 병렬 출력과 MIPI AP의 CSI-2 입력을 상호 연결할 수 있는지를 보여준다.

.jpg)

자동차 산업에서도 MIP 지원 AP와 부품 사용이 증가하고 있다. 자동차 설계에서 첨단 운전자 지원 시스템(ADAS)과 인포테인먼트 같은 애플리케이션을 위해 탑재되는 카메라 콘텐츠와 수가 지속적으로 크게 증가함에 따라 비디오 브리징 기능에 대한 필요성도 높아지고 있다.

현재 카메라는 운전자가 후진 시 차량 후방을 보다 잘 볼 수 있게 하고. 사이드 미러를 대체하고 완전한 360도 시야를 제공하도록 도와줄 수 있으며, 차선 변경 추적, 사각지대 최소화와 같은 애플리케이션을 지원할 수 있다. 최신 자동차에서 설계자는 다수의 이미지 센서로부터 비디오 데이터를 취합하고 한데 합쳐, 이를 CSI-2 인터페이스를 통해 AP에 제공할 수 있다.

이러한 동일한 비디오 브리징 기능은 게이밍 애플리케이션에서 설계자가 여러 대의 카메라에서 생성되는 데이터를 한데 합치거나 다수의 디스플레이에 분할하기 원할 때 매우 유용하게 활용할 수 있다. 예를 들어 빠르게 발전하는 가상현실(VR) 시장에서 떠오르는 동향 중 하나는 한 대의 디스플레이로부터 절반의 대역폭으로 실행하는 듀얼 헤드 마운트 디스플레이로 마이그레이션하여 스테레오 영상을 제공하는 것이다. 하지만 AP가 단 하나의 DSI 인터페이스만 가질 때 설계자는 어떻게 영상 공급을 분할할 수 있을까?

.jpg)

(그림 4)는 설계자가 비디오 브리지를 이용해 AP로부터 발생하는 비디오 데이터를 단일 DSI 인터페이스를 거쳐 분배하고, 이를 각각 왼쪽 눈과 오른쪽 눈에 해당하는 2개의 DSI 인터페이스에 걸쳐 분할하는 것을 보여준다. 이 브리지는 레인당 최대 1.5Gbps I/O 속도로 2개의 HD 디스플레이 또는 1개의 QHD 디스플레이를 지원할 수 있다.

.jpg)

또 다른 적용 가능한 브리징 애플리케이션은 데이터를 단일 CSI-2 브리지로 합치는 것이다. (그림 5)는 드론 또는 VR 개발자가 어떻게 새로운 브리징 디바이스를 사용하여 여러 개의 이미지 센서 비디오 출력을 하나의 스트림으로 결합하여 AP의 인터페이스 요구사항을 만족하는지 보여준다. 이 브리지는 설계에서 AP가 이미지 센서 입력의 수를 지원하기에 충분한 인터페이스를 제공하지 못하거나 이미지 센서와 이미징 데이터 간 프로세싱 지연이 존재하는 애플리케이션에 이용할 수 있다. 이 경우 프로세서는 최소 지연으로 정확히 동일한 시간에 여러 개의 CSI-2 출력을 캡처해야 한다. 병합된 여러 비디오 스트림은 공통 클럭을 공유해야 하며, 일부 경우 개별적인 파워업 루틴이 필요하다.

적합한 솔루션 찾기

이와 같은 새로운 비디오 애플리케이션에 대처하기 위해 오늘날의 임베디드 비디오 설계자는 저전력, 초소형 풋프린트에 고성능을 제공할 수 있는 브리징 솔루션을 필요로 한다. 이상적으로는 카메라, 디스플레이, AP 사이에 호환되지 않는 인터페이스를 변환하고, 다수의 비디오 스트림을 단일 출력으로 결합하거나 단일 출력을 여러 인터페이스에 걸쳐 분할할 수 있게 하는 브리징 솔루션을 필요로 한다.

이러한 문제를 해결하는 한 가지 방법은 범용, 다중 채널 수동 스위치를 사용하여 회로 보드에서 신호를 여러 위치로 라우팅하는 것이다. 하지만 대부분의 mux/de-mux 솔루션은 설계자들이 필요로 하는 높은 성능이나 수준의 설계 유연성을 제공하지 않는다. 다른 옵션은 ASSP(Application Specific Standard Product) 또는 ASIC(Application Specific Integrated Circuit)을 기반으로 하는 브리징 솔루션에 투자하는 것이지만, 대부분의 브리징 애플리케이션은 범위가 너무 한정돼 있어 이러한 종류의 접근방법과 관련된 높은 초기 개발비(NRE)와 긴 개발 사이클을 정당화하지 못한다.

래티스 반도체가 1년 전부터 선보인 CrossLink FPGA는 설계 유연성과 빠른 타임투마켓을 제공하고 12Gbps 대역폭에서 최대 4K UHD 해상도를 지원하는 업계에서 가장 빠른 MIPI D-PHY 브리징 디바이스이다. AP, 이미지 센서, 디스플레이 간에 일치하지 않는 인터페이스 문제를 해결하도록 설계된 CrossLink는 저가의 초소형 브리징 솔루션으로 광범위한 최신 및 레거시 프로토콜을 지원한다.

각각의 CrossLink 브리지는 2개의 MIPI D-PHY 하드 블록을 멀티플렉싱, 병합, 디멀티플렉싱, 중재, 분할 및 데이터 변환을 비롯한 광범위한 비디오 기능을 지원할 수 있는 모바일 FPGA 패브릭과 연결한다. 디바이스의 각 MIPI D-PHY 블록은 최대 4개의 데이터 레인과 1개의 클럭을 갖추고 송/수신(Tx 및 Rx)을 지원한다. 2개의 프로그래머블 I/O 뱅크는 MIPI D-PHY, MIPI CSI-2, MIPI DSI뿐 아니라 CMOS, RGB, SubLVDS, SLVS, LVDS, Open LDI를 포함한 다양한 종류의 인터페이스를 지원한다.

인접한 FPGA 패브릭은 5,936개의 4-input LUT, 180kbits 블록 RAM, 47kbits 분산 RAM을 내장하고 있다. 논리 산술, RAM 및 ROM 기능을 위한 기본적인 빌딩 블록의 역할을 하는 PFU(programmable function unit)에서 LUT는 전용 레지스터와 나란히 배치된다. 프로그래머블 라우팅 네트워크는 PFU 블록을 연결한다. 프로그래머블 I/O 뱅크를 갖는 임베디드 블록 RAM(EBR), 임베디드 I2C 및 임베디드 MIPI D-PHY의 행은 PFU의 행 사이에 배치된다. 설계자는 래티스의 Diamond 설계 소프트웨어를 사용하여 PFU 블록을 구성하고 각각의 설계를 라우팅할 수 있다.

일반적인 개발 흐름

CrossLink 기반 인터페이스 브리지를 구성하기 위한 개발 흐름은 비교적 간단하다. 개발자는 사용하기 원하는 IP를 선택하여 시작하거나, 래티스의 Diamond FPGA 설계 소프트웨어 내에 포함된 래티스의 IP 구성 툴인 Clarity Designer에서 IP를 생성할 수 있다. Clarity Designer는 복수의 IP 블록을 구성하고, IP 블록 간 연결을 생성하고, 설계에서 IP 블록이 사용하는 리소스를 계획할 수 있게 한다.

IP가 생성되면, 개발자는 Aldec 시뮬레이터를 사용하여 시뮬레이션을 수행한다. 개발자는 Aldec 시뮬레이터를 열고 툴로 이동하여 마이크로 실행을 클릭하면 시작할 수 있다. 시뮬레이션이 완료되면, 개발자는 시뮬레이션 결과를 볼 수 있다. 설계 디버그는 래티스의 Reveal 온칩 디버그 툴을 사용하여 하드웨어에서 수행된다. 래티스의 Diamond FPGA 설계 소프트웨어에 통합된 Reveal은 단일 버튼 작동, 향상된 트리거 기능, 원본 설계를 수정할 수 있는 간단한 흐름 및 최근 성능이 강화된 로직 분석기 파형 기능을 갖추고 있다.

시스템 개발을 가속화하기 위해 래티스는 CrossLink LIF-MD6000 마스터 링크 평가 보드를 제공한다. 이 보드는 81-ball csfBGA 패키지에 CrossLink-MD6000 디바이스를 포함한다. CrossLink 디바이스 외에도 평가 보드는 미니 USB 타입B 커넥터-FTDI와 SPI를 사용하는 FTDI-CrossLink 회로를 포함하고 있다. 또한 키트에는 2개의 인터페이스 보드가 추가되었다.

결론

20년 전 지배적인 PC 아키텍처가 광범위한 시장에서 개발을 주도했다면, 오늘날 날로 성장하는 모바일 시장은 산업, 자동차, 의료 등 다양한 분야에서 유사한 영향을 미치고 있다. 모바일 기술이 새로운 애플리케이션으로 지속적으로 확대됨에 따라 모바일 관련 제품 설계자는 브리징 기술을 활용하여 모바일 시장이 갖는 규모의 경제와 모바일 프로세서, 디스플레이, 이미지 프로세서의 비용 및 성능 장점을 완벽하게 이용할 필요가 있다.

(이 기사의 원문은 2017년 9월 28일자 EE Catalog에서 확인하실 수 있습니다)

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)

.jpg)

.jpg)

.jpg)