글|로버트 브래넌(Robert Brennan), RF 애플리케이션 엔지니어, 아나로그디바이스

오랫동안 합성기 업계를 주도해 왔던 PLL과 VCO는 별개의 디스크리트 솔루션으로 존재해 왔다. 하지만 디스크리트 솔루션 방식은 보드 공간의 비효율성, 좁은 VCO 출력 주파수 범위 등이 문제였다. 이를 해결하기 위해 등장한 것이 통합 PLL/VCO이며, 2014년말에는 2세대 통합 PLL/VCO가 출시됐다.

사실상 거의 모든 RF 및 마이크로파 시스템에는 주파수 합성기가 필요하다. 주파수 합성기는 국부 발진기(local oscillator) 신호를 발생시켜 믹서, 변조기(modulators), 복조기(demodulators) 등 다양한 RF 및 마이크로파 소자를 구동한다. 종종 시스템의 핵심으로 여겨지는 합성기를 만드는 방법 중 하나가 PLL 주파수 합성기를 사용하는 것이다.

원래는 간단한 PLL을 기준 신호(reference signal)와 비교해 전압제어 발진기(Voltage Controlled Oscillator, VCO) 출력 주파수로 나눈 뒤, VCO가 전압을 제어하도록 조정해 출력 주파수를 수정한다. 수년 간 PLL과 VCO는 별도의 칩, 즉 디스크리트 솔루션으로 존재했다. VCO는 실제 출력 신호를 생성했고 PLL은 출력 신호를 모니터링하고 VCO를 조정해 VCO를 알려진 기준 신호에 대해 고정시킨다.

디스크리트 솔루션의 장단점

PLL과 VCO가 디스크리트 솔루션으로 남아있을 때 여러 장점이 있다.

- 각 디스크리트 칩이 가능한 최고의 성능을 가지도록 설계할 수 있다.

- PLL과 VCO 간의 물리적 거리가 교차 결합(cross coupling) 효과를 줄여주고 출력 상에 발생할 수 있는 원치 않는 스퓨리어스 신호(spurious signals)를 최소화할 수 있다.

- 루프의 칩 하나가 손상되었을 때 교체해야 할 소자의 수가 줄어든다.

디스크리트 솔루션 방식은 오랫동안 합성기 업계를 주도했지만 단점도 있었다. 한가지 중요한 문제는 디스크리트 솔루션 방식이 두 개의 칩과 이를 지원하는 모든 소자를 담아야하기 때문에 보드 공간이 많이 필요하다는 것이었다. 이로 인해 최종 제품의 크기가 더 커지고 더 많은 비용이 들었다.

디스크리트 솔루션 방식의 또 다른 중요한 문제는 기존 VCO의 출력 주파수 범위가 좁다는 것이었다.

VCO의 대역폭은 50~500 MHz(typ)이며 최대 2 GHz까지 높일 수 있지만, 대역폭을 높이려면 능동 필터 기반의 연산증폭기가 필요했다. 이는 넓은 주파수 범위를 필요로 하는 시스템을 구현하려 할 때 상당한 문제가 된다.

더 넓은 주파수 범위의 합성기를 제작하려면 여러 PLL과 VCO, 지원 소자(supporting components), 필터링 부품, 스위치, 전원공급 장치가 필요한데, 이 경우 필요한 보드 공간과 설계 비용은 기하급수적으로 늘어나기 때문이다. 디스크리트 솔루션 방식은 보드 설계 방식에 영향을 미칠 뿐만 아니라 각 장치의 품질을 보장하고 그에 해당하는 소프트웨어를 제작하고, 재고를 관리하는 데 간접적으로 들어가는 업무량도 상당하다.

VCO 아키텍처 및 통합 VCO로의 전환이 가져온 변화

약 10년 전, PLL 기반 합성기 업계에 엄청난 혁신이 있었다. 처음으로 통합 PLL/VCO가 시장에 등장했던 것이다.

이 커다란 발전으로 인해 보드 크기가 작아지고, 비용은 절감됐으며, 간접 업무도 크게 줄어들었다. 통합 솔루션을 사용한다는 것은 VCO 아키텍처를 변형시켜 하나의 소자로부터 광대역 합성기를 만들 수 있게 된다는 의미이기도 했다. 이제 VCO 아키텍처 및 통합 VCO로의 전환이 합성기 성능에 가져온 변화를 살펴보자.

기존의 VCO는 단순한 장치였다. VCO 상의 동조핀(tuning pin)에 전압이 인가되면 특정 주파수가 출력된다.

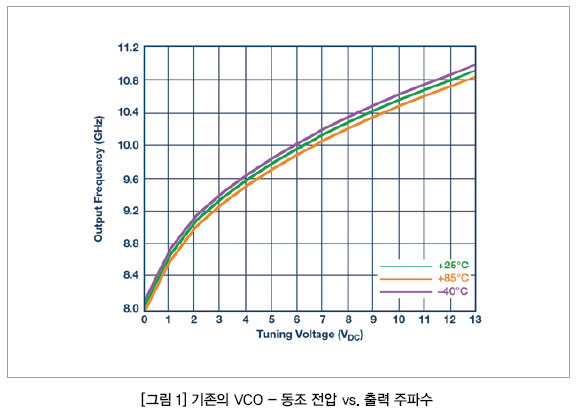

전압이 증가하면 출력 주파수도 증가하고, 전압이 감소하면 출력 주파수도 감소한다. 〈그림 1〉은 GaAs MMIC VCO의 동조 전압(tuning voltage)과 출력주파수의 관계를 보여준다. 동조 전압 13V 범위에서는 능동 필터나 고전압 충전 펌프가 내장된 PLL이 필요하다.

통합 PLL/VCO 솔루션 방식에는 기존의 아키텍처를 기반으로 하는 다른 유형의 VCO 아키텍처가 사용된다. 통합 PLL/VCO는 기존의 VCO 몇 개를 효과적으로 나란히 결합해 놀라울 정도로 넓은 대역폭을 가지는 VCO를 만들어낸다. 각각의 개별 VCO는 커패시터를 끄고 켜서 생성하며 대역(band)이라 불린다. PLL과 VCO가 하나의 칩에 통합되어 있기 때문에 다중대역 아키텍처가 가능해진다.

사용자가 새로운 주파수에 고정시키고 싶을 때마다 장치는 VCO보정 과정을 초기화한다. 이 VCO 보정 과정 동안 칩은 VCO 대역을 빠르게 정렬하고 필요한 출력 주파수에 사용될 최적의 대역을 선택한다. 일단 VCO 대역이 선택되면 PLL은 루프를 고정하고 원하는 주파수로 출력을 유지시킨다.

이 중에서 1세대 PLL/VCO 칩은 4GHz 이상의 대역폭을 제공했다.

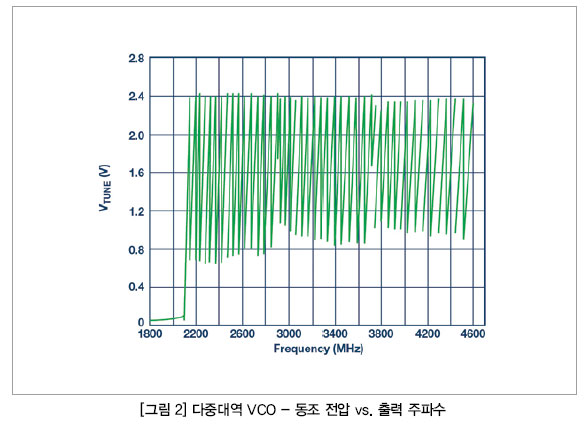

디스크리트 솔루션에서의 100~300 MHz대역폭과 비교해보자. 아주 작은 칩 하나로 이 정도의 주파수 범위가 가능해졌다. 이전의 디스크리트 솔루션에서 PLL, VCO, 필터, 스위치를 여러 개 쌓아야 했던 것과 비교할만하다. 〈그림 2〉는 다중대역 PLL/VCO의 동조 전압과 출력 주파수 관계를 나타낸 것이다. 이 예에서 기본(fundamental) VCO의 출력 범위는 2,200~4,400 MHz로 나타나 있다.

이러한 칩 내부의 VCO 출력뒤에는 신호를 최소 35 MHz까지 낮출 수 있는 주파수 분주기가 여러 개 추가된다. 따라서 4 GHz를 초과하는 대역폭도 모두 하나의 5 mm × 5 mm 패키지로 가능하다.

이 혁신적인 기술은 주파수 범위, 보드 공간, 비용, 별도로 필요한 작업 분야에서 커다란 진전을 이끌어냈지만, 통합 솔루션이 디스크리트 솔루션을 완전히 뛰어넘을 수 없도록 만드는 단점들은 여전히 존재했다. 많은 애플리케이션에서 주파수 범위 다음으로 가장 중요한 성능 사양은 위상 잡음이다.

왜 위상 잡음이 그렇게 중요할까?

신호가 깨끗한 대기를 통해 송신되도록 하는 시스템이 있다고 해보자.

송신 안테나에서 송신되는 신호의 SNR(signal-to-noise ratio)이 50 dB라고 해보자. 이는 수신기가 받아야 하는 신호가 송신된 신호, 즉 해당 주파수보다 조금 더 높거나 낮은 주파수 중 한쪽에서 발생하는 잡음보다 50 dB 더 강력하다는 뜻이다. 신호 세기가 잡음 수준으로 낮아져서 송신이 끊어질 때까지 16 km(10 마일)를 이동할 수 있다고 해보자.

이제, 합성기의 위상 잡음이 3 dB만큼 향상됐다고 하자. 이렇게하면 송신되는 신호의 SNR이 53 dB이 된다. 그 결과 송신되는 신호의 세기는 이전의 16 km 범위 신호의 두 배가 되며 따라서 잡음 수준으로 낮아질 때까지 더 먼 거리를 이동할 수 있다. 더 먼거리를 이동할 수 있다는 것은 필요한 리피터(repeater)나 송신기 수가 줄어들기 때문에, 비용을 절감할 수 있다는 의미다.

이러한 통신 관련 사례 외에도 전자테스트 및 측정 업계에서도 더욱 뛰어난 위상 잡음 성능을 필요로 한다. 통신 업계에서 어떤 위상 잡음 성능을 사용하더라도 전자 테스트 및 측정 기기에는 그보다 더 뛰어난 위상 잡음 성능이 필요하다. 그래야 기기에서 통신 프로토콜을 측정할 수 있기 때문이다.

여러 솔루션이 디스크리트 부품에서 통합 부품으로 옮겨갈 수 있었고, 그 과정에서 엄청난 비용을 절감했지만, 1세대 PLL/VCO의 위상 잡음 성능은 저위상 잡음 요건이 필요한 여러 애플리케이션을 대체할 수 있을 정도로 뛰어나지 않았다. 위상 잡음 성능뿐 아니라 주파수 범위도 디스크리트 PLL과 VCO를 필요로 하는 많은 애플리케이션과 비교해 여전히 꽤 낮다.

주파수 범위 문제는 주파수 2배기(doubler)와 기타 배율기를 사용해 어느 정도 해결할 수 있지만 이들 부품은 전력을 많이 잡아먹고 솔루션의 비용과 보드 공간을 늘리게 된다.

다행히 이러한 통합 솔루션이 출시되고 있는 동안에도 새로운 IC 프로세스로 이동하려는 움직임이 이미 진행되고 있었으며, 이는 훨씬 수요가 많은 위상잡음과 주파수 범위 성능 향상을 염두에 둔 것이었다.

2세대 통합 PLL/VCO

따라서 이 시점에서 2세대 통합 PLL/VCO를 위한 장이 마련됐다. 요건은 다음과 같다.

- 4.4 GHz보다 큰 출력 주파수

- 디스크리트 솔루션 방식에 견줄만한 위상잡음 성능

- 하나의 소형 패키지에 PLL과 VCO 통합

- 디스크리트 솔루션 방식보다 저렴한 비용

2014년 말 처음으로 위의 요건을 갖춘 2세대 통합 PLL/VCO가 출시됐다.

출시된 제품은 이전보다 훨씬 넓어진 10 GHz 출력 주파수 범위와 디스크리트 VCO에 견줄 정도의 위상 잡음, 5 mm × 5 mm 패키지에 비슷한 사양의 디스크리트 PLL 및 VCO 솔루션보다 낮은 가격까지 갖추고 있었다(그전에는 주파수 범위가 훨씬 좁았다).

이로써 사용자는 디스크리트 솔루션이 가지는 위상 잡음 성능의 장점은 모두 갖추고 있으면서도 기타 통합 솔루션의 장점까지 추가된 제품을 사용할 수 있게 됐다. 추가된 장점만큼 PLL 기술은 지난 수년간 발전했으며 그로 인해 2세대 PLL/VCO 장치의 다양한 PLL 성능 역시 개선됐다.

1세대 PLL/VCO의 경우 PLL 블록은 약 32 MHz의 최대 위상 주파수 검출기(Phase Frequency Detector, PFD) 주파수와 약 12비트의 분수분주형 분주기(fractional-N divider) 해상도를 가진다. 이러한 조합으로 인해 채널 해상도가 수십 킬로헤르츠(typ) 수준이다. 2세대 PLL/VCO는 100 MHz 이상의 최대 PFD 주파수와 25비트, 또는 최대 49비트의 분수분주형 분주기 해상도를 가진다. 이 경우 장점이 크게 두 가지 있다.

첫째, PFD 주파수가 더 높아져서 PLL 위상 잡음도 더 낮아진다(PFD 주파수를 모두 2배로 하면 사용되는 분수분주형 분주기 수가 절반이 될 수 있어서 N 분주기의 잡음 기여(noise contribution)가 3 dB까지 떨어진다).

둘째, 25비트 이상의 해상도에서는 정확한 주파수 생성을 가능하게 하고 Hz미만의 채널 간격을 허용한다.

스퓨리어스 성능

통합 PLL/VCO에는 논의가 필요한 중요한 측면이 있다. 위에서 열거한 디스크리트 솔루션의 장점 중 하나가 두 칩간의 물리적 절연으로 인해 PLL과 VCO사이의 교차 결합(cross coupling)이 줄어들고, 그 결과 원치 않는 스퓨리어스 신호의 세기를 줄일 수 있다는 것이다. 그러다 보니 PLL과 VCO가 통합됐을 때, 스퓨리어스 성능이 저하되는 것은 불가피하다.

시장에서 판매되던 일부 부품은 이러한 성능 저하를 가급적 아주 낮은 수준으로 유지해서 PLL/VCO의 스퓨리어스 성능이 놀랄 정도로 뛰어나다. 다른 PLL/VCO 부품의 경우, 일부 고성능 제품에 맞는 수준으로 스퓨리어스 성능을 향상시키려면 별도의 애플리케이션 작업을 필요로 한다.

PFD 주파수를 변경해 IBS(Integer Boundary Spur) 제거하기

이를 해결하는 한 가지 방법은 주파수 설계 알고리즘(frequency planning algorithm)을 사용하는 PLL의 PFD 주파수를 변경하는 것이다. 이렇게 하면 PFD 블록으로 인해 생성되는 스퓨리어스 신호를 그 영향이 약하게 미치는 곳으로 이동시켜 사실상 제거할 수 있다.

PLL과 VCO 절연하기

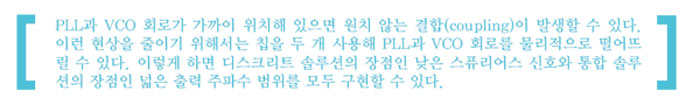

위에서 말한 것처럼 PLL과 VCO 회로가 가까이 위치해 있으면 원치 않는 결합(coupling)이 발생할 수 있다. 이런 현상을 줄이기 위해서는 칩을 두 개 사용해 PLL과 VCO 회로를 물리적으로 떨어뜨릴 수 있다. 이렇게 하면 디스크리트 솔루션의 장점인 낮은 스퓨리어스 신호와 통합 솔루션의 장점인 넓은 출력 주파수 범위를 모두 구현할 수 있다.

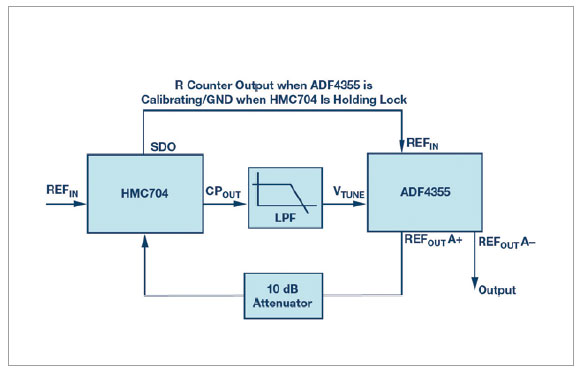

이처럼 칩 두 개를 사용하는 아키텍처를 구현하기 위해 통합 PLL/VCO의 RF 출력은 외부 PLL의 RF 입력에 공급돼야 한다. 외부 PLL의 충전 펌프출력은 루프 필터로 가며, 루프 필터의 출력은 다시 VCO의 동조 포트(tuning port)에 있는 통합 PLL/VCO로 돌아간다. 처음에 PLL/VCO는 루프를 고정하지만, 그런 다음 통합된 영역의 PLL이 비활성화되고 외부 PLL이 루프를 고정시킨다. 이런 방식으로 PLL과 VCO를 물리적으로 절연시키면 원치 않는 스퓨리어스 결합을 줄일 수 있다는 이점이 생기며, 외부 PLL의 성능이 더 뛰어난 경우 이러한 향상을 출력에서 확인할 수 있다.

결론

매년 점점 더 많은 통합 PLL/VCO 장치가 출시되고 있으며 각 세대를 넘어설수록 주파수 동작(frequency operation)이 향상되고, 대역폭이 넓어지며, 위상 잡음과 스퓨리어스가 줄어드는 등 전반적인 성능이 향상된다. 이전에 디스크리트 솔루션이 필요했던 어플리케이션들이 통합 PLL/VCO 솔루션으로 구현되는 경우도 점차 늘어나고 있다. 이로 인해 비용과 보드 공간이 절약되고, 무엇보다도 RF 설계자들의 작업이 수월해진다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>