글|클라렌스 마이요트(Clarence Mayott), 애플리케이션 엔지니어, 혼성신호 제품 리니어 테크놀로지(Linear Technology Corp.)

LTC2123과 LTC6430을 활용하여 설계한 시스템은 낮은 잡음, 높은 선형성과 함께 저전력 소모, 소형 솔루션 크기를 구현하므로 오늘날의 통신 수신기에 이상적인 솔루션이 될 수 있다.

오늘날의 통신 시스템에서 입력 네트워크에 잡음을 제거할수록 수신기는 더 민감한 시스템이 될 수 있다. 시스템의 수신기 부분은 외부로부터 들어오는 잡음에 매우 민감하다. 이러한 외부 잡음은 FPGA나 전원장치 또는 ADC 자체의 디지털 신호에 영향을 미칠 수 있다.

초소형 솔루션을 설계할 때 이러한 외부 잡음과 아날로그 입력 사이에 장벽(barrier)을 삽입하면 입력 네트워크로 들어오는 잡음을 감소시키고 시스템 감도를 향상시킬 수 있다.

그러나 시스템 감도를 위해 4W의 전력이나 소모하는 고전력 증폭기를 사용하면서 초소형 솔루션을 구현하기는 어려울 것이다. 원하는 감도를 유지하려면 시스템의 잡음 성능을 향상시키면서 높은 선형성을 가지며 민감한 ADC로 신호를 전달할 수 있는 저잡음 증폭기가 필요하다.

새로운 JESD204B 표준과 같이 ADC 설계에 달성된 여러 향상들은 설계자가 수신기 감도를 제한했던 예전의 설계 과제들을 해결하는데 도움을 준다. 이러한 향상을 새로운 저전력 증폭기와 결합하면, 궁극적으로 시스템 잡음 성능을 향상시킬 수 있다.

증폭기 설계 과제

전통적으로 고주파 애플리케이션은 갈륨비소(GaAs)나 인듐인화물(InP) 이득 블록을 사용하여 높은 선형성과 낮은 잡음을 달성했다. 이러한 이득 블록은 9-12V 사이의 전압을 필요로 하며, 수신기 채널당 2-4와트의 전력 소모가 발생한다.

이에 따라 수신기 보드를 냉각시켜야 하는 까다로운 과제가 뒤따르며, 이를 적절히 관리하지 못할 경우 시스템 성능을 저하시킬 수 있다. 배터리로 동작하거나 낮은 전압의 애플리케이션의 경우 전통적인 이득 블록은 높은 전력 소모로 인해 문제가 될 수 있다.

또한 일부 이득 블록은 관심 있는 주파수 범위에 따라 변화할 수 있는 입력 또는 출력 정합 회로를 필요로 한다. 이는 단일 네트워크가 수신할 수 있는 전체 대역폭을 감소시키고, 입력 네트워크를 정합시키는 데 필요한 설계 시간을 증가시킨다.

이 밖에 이러한 이득 블록은 대부분 단일 종단형(Single Ended)이므로, 본질적으로 비평형적(imbalanced)이다. 모든 시스템에서 비평형 상태는 짝수차 고조파를 발생시키고, 이러한 짝수차 고조파는 우수한 선형성을 달성하기 위해 필터링을 필요로 한다.

많은 경우 2차항은 필터 감쇄가 낮은 통과대역의 가장자리에 가까울 수 있다. 이러한 경우 2차항 고조파 왜곡은 감쇄되지 않으므로 수신기 감도가 떨어진다. 처음부터 차동 이득 블록을 사용하면 평형적 네트워크를 설계할 수 있으며, 2차 고조파 왜곡 문제도 완화할 수 있다.

증폭기 솔루션

GaAs 이득 블록의 전력 소모를 낮추고 우수한 선형성과 잡음 성능을 유지하려면 기존과 다른 저전력 공정이 필요하다. LTC6430은 극히 적은 전력으로도 고전력 이득 블록의 선형성과 잡음 성능을 최소화하는 저전력 실리콘 게르마늄(SiGe) 공정으로 설계된 차동 이득 블록이다. LTC6430은 5V 전원으로 동작하며, 단 160mA의 전류만 소모하므로 전력 소모를 1W 미만으로 낮춘다.

LTC6430은 이와 같이 전력 소모가 낮아 열을 쉽게 발산시킬 수 있어 기존의 이득 블록을 적용하기에 적합하지 않았던 저전력, 배터리 구동 애플리케이션이나 열에 민감한 애플리케이션에 사용할 수 있다.

LTC6430은 단일한 정합 네트워크로 어떠한 조건에서도 안정적이어서, 필요한 외부 부품은 DC 블록킹 커패시터와 RF 바이어스 초크뿐이다. 이는 단일 회로에서 LTC6430이 25MHz ~ 1600MHz 범위의 주파수를 수신할 수 있게 한다.

또한 입력 네트워크 설계 시간을 단축시켜 주므로 시스템의 다른 핵심적인 부분에 더 많은 시간을 할애할 수 있다. LTC6430 정합 회로는 단순하여, 필요한 부품이 적을 뿐 아니라 ADC와 증폭기 사이의 네트워크 복잡성도 감소돼 장벽과 비아에 더 많은 회로 보드 공간을 이용할 수 있어 시스템 성능을 향상시킬 수 있다.

LTC6430은 짝수차 고조파를 자연적으로 억제하는 차동 증폭기이다. LTC6430의 평형 특성은 짝수차 고조파를 제거하고 시스템의 전반적인 선형성을 향상시킨다. 또한 이 평형 특성은 증폭기와 ADC 사이에 위치하는 출력 필터의 감쇄 요구사항을 낮춰준다. ADC와 증폭기 사이를 평형 네트워크로 가장 간단하게 연결할 수 있어 장벽이나 비아(via) 사용에 더 많은 공간을 사용할 수 있으므로 ADC와 증폭기 사이에 상호작용이 감소되며, 이로 인해 최상의 결과를 달성할 수 있다.

네트워크는 필터 요구사항을 완화시키기 때문에 더 적은 부품을 사용할 수 있고, ADC와 인터페이싱 하는 단순한 회로를 제공한다. LTC6430은 차동 출력 네트워크를 가지므로 발룬(balun) 없이 차동 ADC를 구동할 수 있어, ADC의 입력 네트워크를 더욱 간소화한다. 또한 ADC와 증폭기 사이에 필요한 부품이 적어 레이아웃이 더 간편해지고, 네트워크의 향상된 평형 상태는 ADC의 성능을 극대화할 수 있다.

ADC 과제

수신기의 잡음은 증폭기와 채널 잡음에만 국한되지 않는다. 문제가 되는 신호로부터 보드에 존재하는 잡음은 ADC 입력 네트워크와 결합돼 ADC에 의해 디지털화될 수 있다. 적절한 레이아웃 기법을 사용하면 다른 잡음원의 크기를 줄일 수 있지만, 일부 잡음은 불가피하다. 시스템에 존재하는 잠재적 잡음원의 하나는 ADC 자체의 디지털 출력이다.

디지털 출력 신호는 큰 전압 스윙과 높은 주파수 성분으로 아날로그 입력과 결합해 다시 디지털 신호로 나오는 디지털 피드백을 생성할 수 있다. 디지털 피드백은 잡음 플로어에서 최대 20dB의 국지적 피크 잡음을 생성할 수 있다. 단일 종단 CMOS 시그널링은 높은 전압 스윙으로 디지털 피드백을 더 악화시키므로 최악의 디지털 피드백을 생성한다.

디지털 라인은 공간 제약이라는, 보다 눈에 띄는 문제를 일으킨다. 보드 공간이 중요한 경우 많은 수의 출력 라인을 갖는 멀티채널 ADC는 귀중한 보드 공간을 차지한다. 이러한 디지털 신호 버스는, 특히 레퍼런스나 클록 또는 입력 네트워크와 같은 잠재적으로 민감한 회로에 가깝게 라우팅할 때 골칫거리가 된다. 디지털 버스가 민감한 회로에 가까이 있을수록 디지털 잡음이 시스템 성능을 저하시킬 가능성이 증가한다.

CMOS 및 LVDS 트레이스 또한 다른 한계를 갖는다. 이들은 DC 평형이 달성되지 않는다. 이는 평균 DC 값을 유지할 수 있는 방법이 없다는 것을 의미한다. 평균 전압이 달라질 수 있다는 사실은 CMOS와 LVDS 신호를 트랜스포머, 광커플러, DC 블록킹 커패시터 및 기타 고역 통과 디바이스와 같은 절연 장벽을 통해 전달할 수 없다는 것을 의미한다.

최근의 통신 시스템에서는 수신기에서 다중 안테나 기술을 사용하기 위해 안테나 어레이를 이용한다. 안테나 어레이는, 특히 약한 신호나 사라지기 쉬운 신호에 대한 신호 수신을 향상시킨다. 그러나 어레이에 안테나를 추가할 때마다 또 다른 완벽한 수신기 체인을 필요로 한다. 안테나 수를 증가시키면 ADC 채널의 수도 증가시켜야 한다.

이들 ADC는 최대 성능을 위해 동기화할 필요가 있는데, 이는 간단한 작업이 아니다. 클록 신호의 편차는 데이터의 부정확한 해석을 초래하고 시스템 성능을 떨어뜨린다. 최고 성능의 클록 팬아웃 디바이스를 사용하는 경우에도 여전히 다양한 클록 경로 간에 스큐가 존재해 디지털 데이터에서 왜곡을 초래할 수 있으며, 이는 디지털 영역에서조차 가려내기 쉽지 않다.

ADC 솔루션

데이터 라인의 수를 줄이고 디지털 시그널링을 사용하면 그라운드 플레인에 주입되는 잡음이 현저히 줄어든다. JESD204B 표준은 CML 데이터 라인 쌍을 사용해 고주파수 직렬 데이터를 전송한다. 샘플 레이트에 따라서는 단 한 쌍의 라인만 필요하다.

이러한 전송 라인 쌍은 차동 특성을 가지므로 필드의 자연적 제거가 가능해, 그라운드 플레인에 결합되는 잡음의 영향을 감소시킨다. 데이터 전송은 직렬 방식이며 8B/10B 인코딩 되므로, 그라운드 플레인에서 아날로그 입력에 나타나게 되는 주파수 성분을 생성할 수 있는 데이터의 반복적인 패턴도 없다.

이는 시스템에서 디지털 피드백의 가능성을 크게 줄여준다. 그라운드 플레인에서 잡음과 고주파수 성분이 적을수록 아날로그 입력에 결합되는 에너지도 감소되므로 디지털 피드백 가능성이 낮아진다.

데이터를 직렬 데이터 쌍으로 전송할 경우, 연결해야 하는 선이 줄어들게 되므로 병렬 데이터의 전체 버스를 라우팅 하는 것보다 더 간편하다. 데이터는 단지 하나 또는 두 쌍의 전송 라인을 사용하여 전달되기 때문에 문제가 되는 신호를 피하는 경로를 선택하기가 훨씬 쉽다. 전송 라인 쌍은 보드 상에서 민감한 영역을 피해 라우팅 할 수 있다.

라우팅 영역이 작을수록 전송 라인 주위에 더 많은 비아를 허용하므로, 잡음이 디지털 트레이스에 결합되거나 디지털 트레이스로부터 발생하는 잡음이 다른 민감한 회로에 결합될 가능성이 더욱 낮아진다.

8B/10B 인코딩을 사용하는 또 다른 이점은 DC 평형이다. 이 방식은 RD(running disparity)를 사용하여 2개의 택일적 코드 그룹에서 동일한 수의 1과 0을 유지하므로 신호의 DC 평균은 통계적으로 영(0)이다. 따라서 단일 쌍의 전송 라인을 트랜스포머, 광커플러, DC 블록킹 커패시터 및 기타 고역 통과 디바이스와 함께 사용할 수 있다. 또한 DC 커플링 방식이므로 절연 장벽 반대쪽 그라운드 플레인을 절연하는 트랜스포머나 광커플러를 통해 신호를 절연 장벽을 통과해 전송할 수 있다.

이에 따라 민감한 수신기 섹션을 잡음이 있는 FPGA 섹션으로부터 전기적으로 절연시킬 수 있게 되므로 보드의 수신기 섹션의 잡음이 감소돼 수신기 감도가 향상된다. 이는 또한 수신기 섹션을 안테나와 물리적으로 가깝게 배치할 수 있게 하고, 광 연결을 사용하면 FPGA 섹션을 더욱 멀리 떨어뜨릴 수 있으므로 FPGA로부터 수신기로 결합되는 잡음을 감소시킨다.

JESD204B 표준의 중요한 장점은 여러 개의 ADC를 동기화할 수 있어 복수 디바이스에서 동시 샘플링을 수행할 수 있다는 점이다. 동기화는 SYSREF 신호를 각 ADC 및 FPGA에 보내는 클록 관리 디바이스를 통해 수행된다(그림 1).

SYSREF 신호가 선언되면, 각각의 ADC 및 FPGA는 SYSREF 신호에 스스로 정렬하고, 각 ADC에서 발생하는 데이터는 FPGA 내부에서 정렬된다. 이는 서로 다른 ADC에서 발생하는 ADC 데이터의 복수 채널에 대한 동시 샘플링을 가능하게 한다.

이 기법은 ADC 데이터와 샘플 클록을 정렬해 동기화를 훨씬 간편하게 한다. ADC를 동기화하면 복수의 안테나로부터 데이터를 간단히 수신할 수 있으므로, 더욱 민감한 수신기 설계가 가능하다.

실제 솔루션

LTC2123은 JESD204B 인터페이스를 탑재한 듀얼 250Msps 14비트 ADC이다. LTC2123은 1250MHz의 입력 대역폭을 가지므로 LTC6430와 함께 사용하면 1GHz 이상의 주파수를 수신할 수 있는 탁월한 언더 샘플링 수신기를 구현할 수 있다. LTC2123은 JESD204B 출력 섹션을 포함하고 있어 보드 레이아웃을 간소화하고 그라운드 플레인에 결합되는 잡음을 줄여주며, 수신기를 시스템의 잡음이 존재하는 디지털 부분으로부터 절연할 수 있다.

또한 JESD204B 회로가 내장돼 보다 쉽게 여러 개의 ADC를 동기화하고 다중 안테나 애플리케이션을 위한 대형 안테나 어레이를 구성할 수 있다. LTC6430의 잡음 지수는 3dB에 불과하므로 ADC와 증폭기 간 인터페이스를 최소화할 수 있다.

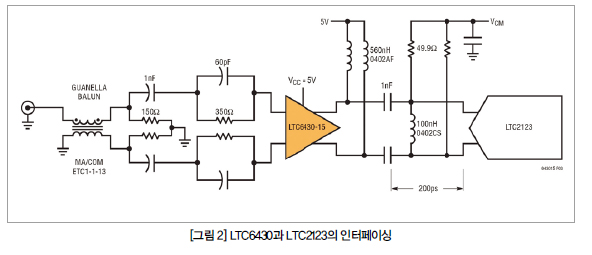

LTC6430 및 LTC2123의 일반적인 회로는 그림 2에 나와 있다. 회로는 ADC와 증폭기 섹션을 초소형으로 구현할 수 있어 입력 네트워크 주변에 더 많은 장벽을 구현함으로써 입력 네트워크로 삽입될 수 있는 잡음을 더욱 줄일 수 있다.

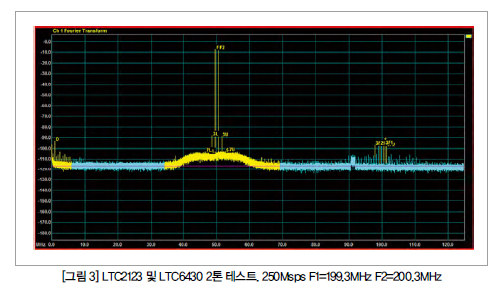

이러한 결합의 결과는 그림 3에서 볼 수 있다. 250Msps에서, 톤이 199.3MHz 및 200.3MHz에서 존재할 때, 3차 상호변조 왜곡 곱은 -87dBFS에 존재하며, SNR은 68dBFS이다. 이러한 성능은 JESD204B 인터페이스와 저전력 소모를 특징으로 갖는 LTC2123와 LTC6430을 이용해 초소형 공간과 다중 수신기에서 달성할 수 있다.

결론

LTC2123 ADC와 LTC6430 증폭기의 결합은 수신기에서 최대 감도를 보장하면서 초소형 시스템 설계를 구현할 수 있게 한다. 전력 소모와 디지털 라인 수를 줄여 전체 솔루션 크기를 줄이고, 입력 네트워크의 민감한 영역 주변에 장벽을 구축할 수 있다. LTC2123에 사용되는 JESD204B 표준은 소수의 전송 라인 쌍과 저전압 CML 시그널링을 사용하여 그라운드 플레인에 삽입되는 잡음을 감소시킨다.

이 표준은 또한 복수 ADC의 동기화를 제공해 다중 안테나 기술을 위한 대형 안테나 어레이를 지원한다. LTC2123과 LTC6430을 사용하여 설계된 시스템은 낮은 잡음, 높은 선형성과 함께 저전력 소모, 소형 솔루션 크기를 구현하므로 오늘날의 통신 수신기에 이상적인 솔루션이 될 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>