오늘날 복잡한 무선 통신 환경으로 다양한 애플리케이션이 등장하고 있다. 그 중에서도 소프트웨어 정의 무선 애플리케이션은 소프트웨어 조작으로 간단하게 무선 장치와 서비스를 제공할 수 있어 각광받는 기술 중 하나이다. 이 글에서는 이득과 타이밍 부정합 오류를 복잡하지 않은 디지털 신호 처리 알고리즘을 통해 새로운 보정 방법을 소개한다.

개요

무선 데이터가 폭발적으로 증가함에 따라 통신 인프라의 더 높은 용량과 가용성을 제공할 수 있는 새로운 수신기 아키텍처가 필요하다. 소프트웨어 정의 무선 시스템은 전력 효율적인 RF A/D 컨버터(RF-ADC)를 기반으로 안테나에서 샘플링하는 동시에 높은 동적 범위를 제공한다[1]. 하지만 이러한 아키텍처는 시변(time-varying) 부정합 오류[2] 문제가 발생하며 실시간 보정이 필요하다.

2채널 TIADC의 부정합 오류(Mismatch error)

ADC의 속도를 두 배로 높이는 효과적인 방법은 위상이 다른 샘플링 클록을 사용하는 두 대의 ADC를 병렬로 작동시키는 것이다. 하지만 이 과정에서 서브 ADC의 전송 기능 간에 부득이한 작은 부정합 오류가 발생한다. 결과적으로 획득할 수 있는 동적 범위를 크게 훼손시키는 스퓨리어스 톤을 발생시킨다. 이런 종류의 ADC에서 발생할 수 있는 오류는 다음과 같다.

1. DC 오프셋 오류(DC offset error)

2. 정적 이득 오류(Static gain error)

3. 타이밍 오류(Timing error)

4. 대역폭 오류(Bandwidth error)

사실 DC 오프셋 오류는 디지털 보정을 사용하면 처리하기가 아주 수월하다. 대역폭 오류는 처리하기 가장 어렵지만, 많은 경우 주의를 기울여 설계하고 배치하면 오류를 줄일 수 있다. 반면 정적 이득 오류와 타이밍 오류 보정이 동적 범위 손실에 큰 영향을 주는 요소이므로 이 글에서는 이 두 오류에 대해 초점을 맞출 예정이다.

제안된 보정 방법

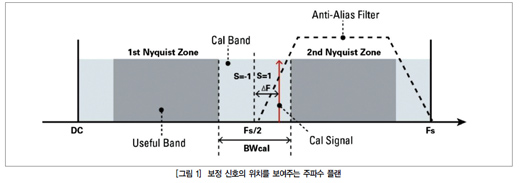

ADC의 나이퀴스트(Nyquist) 대역폭은 충분히 사용되는 경우가 별로 없다. 보통 나이퀴스트 대역폭 중 일부가 안티 앨리어싱 필터의 롤오프(roll-off)에 할당된다. 사용되지 않는 나머지 대역은 제한 교정 신호를 삽입하는 데 사용된다. 보정에는 사인파가 사용되며 설정하려는 두 가지의 주요 제약조건에 대해 높은 스펙트럼 순도를 생성하기 쉽기 때문이다.

1. 진폭은 평가의 정확성을 보장하면서도 동적 범위에 영향을 미치지 않을 정도로 작게 유지된다. 여러 차례 실험 결과에 따르면 14비트 ADC의 경우 -40 dBFS에서 -35 dBFS 사이 수준의 범위가 최적의 결과를 제공한다.

2. 주파수는 디지털 신호 처리 알고리즘을 단순화하기 위해 다음 개별 값들로 제한된다.

.jpg)

(등식 1)

Fs가 TIADC 샘플링 주파수라고 할 때, P와 K는 부호 없는 정수이며 S는 나이퀘스트 영역의 가장자리에 대한 보정 신호의 위치에 따라 +-1의 값을 가진다(그림 1 참조). 이 신호는 ADC의 클록을 기준 신호로 사용하는 분수-N PLL로 칩 위에 발생시킬 수 있다. K를 충분히 높게 설정하면 보정 신호의 고조파가 필터링 조건을 낮추는 데에 사용되는 대역 외부에 앨리어싱 현상이 나타난다. 스윙 조정은 PLL 외부에 위치한 프로그램할 수 있는 감쇠기를 통해 가능하다.

만약 x0와 x1이 보정 신호를 입력으로 하는 두 개의 서브 ADC의 출력을 나타내면 등식 1을 사용해 이 두 신호를 연결할 수 있다(잡음은 무시).

![]() (등식 2)

(등식 2)

이 선형 필터링 공식의 계수 h0과 h1은 다음의 식에 의해 이득 오류 g 및 타이밍 오류 Δt와 관계된다.

.jpg)

(등식 3)

이러한 비선형 방정식은 선형화될 수 있고 부정합 오류가 의도적으로 낮게 유지가 된다는 사실을 고려하면 일차 근사를 사용해 도치시킬 수 있다.

추정 알고리즘은 세 가지 단계로 구성된다.

1. 보정 신호를 추출하고 LMS 알고리즘을 사용해 서브 ADC의 출력에서 제거되며 개별 시간 신호인 x0과 x1을 넘겨준다. 이 알고리즘에는 보정 주파수에서 디지털 코사인/사인 기준 신호 참조가 필요하다. 코사인 신호는 크기 4 K(실제로 K 쫅 64)의 작은 LUT(look up table)로 생성된다. K를 지연하는 것만으로 코사인에서 사인 신호를 얻을 수 있다.

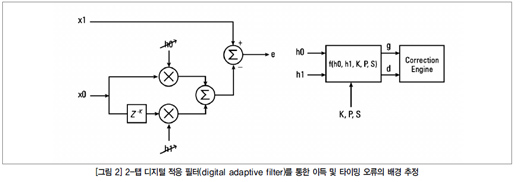

2. 계수 h0와 h1는 그림 2에서처럼 LMS 알고리즘을 사용해

추출된 x0과 x1 신호에 따라 추정한다.

3. 이득 및 타이밍 오류는 등식 3에서 도출된 1차 방정식을 사용해 계산할 수 있다.

일단 추정이 끝나면 이득 및 타이밍 오류는 디지털 보정 엔진에 사용된다. 이득은 간단한 디지털 배율기(multiplier)를 사용해 보상된다. 타이밍 오류는 수정된 분수 지연 필터를 사용해 보정할 수 있다[3]. 다상 및 대칭의 경우 필터를 구현할 때 복잡성을 줄이기 위해 사용한다. 추정과 보정 엔진 모두 서브 ADC 샘플링 비율에서 작동한다. 다운 샘플링은 최적화를 증가시키기 위한 추정에 사용될 수 있다.

개념 증명

테스트용 합성 신호는 다음과 같이 구성된다:

300 MHz 중심의 TM3.1, 20 MHz LTE 반송파

S=1, K=8, P=2K에 상응하는 253.44 MHz, -35 dBFS 보정 사인파

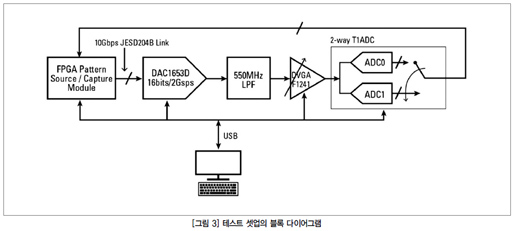

위의 신호는 그림 3의 테스트 셋업을 사용해 생성됐다. 저잡음과 고선형 D/A 컨버터[4] 및 DVGA[5] 덕분에 이러한 셋업으로 광역 동적 범위를 제공할 수 있다. 여기서 시판 중인 14 Bits/500 Msps TIADC를 사용해 조정할 수 있는 고해상도 이득 및 타이밍 오류를 통합한다. ADC 원시 데이터는 FPGA로 포착했으며 매트랩(Matlab)짋을 사용한 보정 알고리즘을 통해 처리됐다. TIADC의 이득 및 타이밍 오류는 최악의 경우를 시뮬레이션하기 위해 각각 약 0.5 dB과 5 ps로 설정됐다.

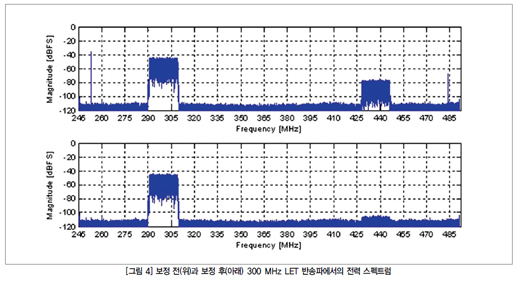

그림 4는 보정 전후의 데이터 전력 스펙트럼을 보여준다. 보정 전 -80 dBFS에서 시작한 LTE 반송파 영상은 보정 후에 약 30 dB 낮은 -110 dBFS 수준으로 줄어든다. 보정 신호와 그 영상은 추출 및 무효화 알고리즘을 통해 완전히 제거된다. 이 성능은 약 200 us의 수렴 시간 이내에 달성된다.

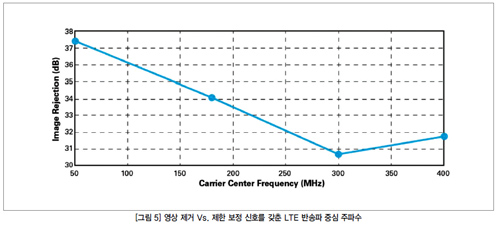

보정 신호는 변화 없이 유지됐으며 LTE 반송파 중심 주파수는 주파수 변화를 평가하기 위해 50 MHz에서 400 MHz까지 스위프(sweep)시켰다. 그림 5의 이미지 제거 결과를 보면 적어도 30 dB의 개선된 동적 범위가 두 개의 첫 나이퀴스트 영역에서 유지된다. 예상대로 이미지 제거는 보정되지 않은 대역폭 오류로 제한된 주파수에 따라 줄어든다.

결론

RF 샘플링 A/D 컨버터는 차세대 소프트웨어 정의 무선 시스템의 주요 부품이다. 타임 인터리브드 아키텍처를 사용하면 동적 범위가 줄어드는 대신 샘플링 비율을 크게 높이고 전력 소모를 낮출 수 있다. 유용한 대역의 제한된 교정 신호를 삽입하면 이득 오류와 타이밍 오류에 대한 교정 알고리즘을 낮출 수 있어 동적 범위를 상당히 증가할 수 있다는 것을 보여줬다.

14비트/500 Msps 시제품을 사용해 측정한 결과 두 개의 첫 나이퀴스트 영역에서 동적 범위가 30 dB 증가한 것을 알 수 있었다. 제안된 방법은 이득 및 타이밍 부정합 오류 모델이 유효한 한 고속 애플리케이션에도 사용될 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>