시스템 레벨과 디바이스 레벨 ESD 현상의 차이점을 설명하고 일상적인 ESD 이벤트를 보호하는 것을 목표로 하는 시스템 레벨 설계 기법을 소개한다.

기술이 발전함에 따라 모바일 전자 기기도 사람들의 삶과 문화의 중요한 부분으로 자리잡았다. 태블릿 및 스마트폰용 햅틱 기술의 발명은 이러한 디바이스 간의 상호작용을 증진시켰고, 피부 표면에서 디바이스로 ESD(정전기 방전) 위험이 발생할 수 있는 완벽한 환경이 조성되었다. 예를 들어 소비가전의 경우 ESD는 사용자 손가락과 태블릿 USB나 HDMI 커넥터 사이에 발생하여 대기 전류의 스파이크 또는 영구 시스템 장애 등 태블릿에 회복 불가능한 피해를 줄 수 있다.

시스템 레벨 vs. 디바이스 레벨 EDS 보호

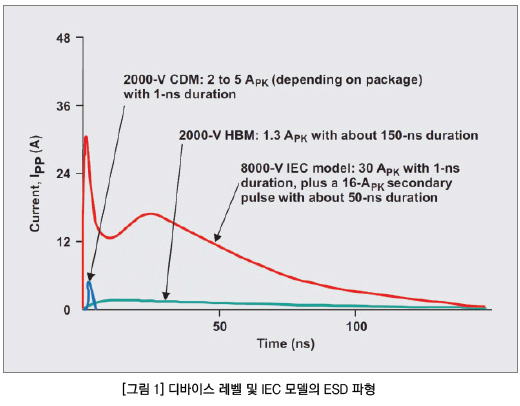

어셈블리부터 보드 레벨 납땜, 엔드 유저와 상호작용까지 IC에 대한 ESD 피해는 언제라도 발생할 수 있다. ESD 관련 피해사고는 반도체가 처음 개발된 시기부터 제기돼 왔으며, 고집적 IC용 마이크로칩과 박막 게이트 산화막 FET가 도입된 1970년대에 문제가 수면 위로 떠올랐다. 모든 IC는 제조 단계에서 ESD 이벤트로부터 IC를 보호하는 내장형 디바이스 레벨 ESD 구조를 가지고 있다. 이러한 이벤트는 서로 다른 3개의 디바이스 레벨 모델, HBM(인체 모델), MM(기계 모델) 및 CDM(대전 디바이스 모델)으로 시뮬레이션 한다. HBM은 휴먼 핸들링으로 인해 발생한 ESD 이벤트를, MM은 오토 핸들링으로 인한 ESD 이벤트를, 그리고 CDM은 제품 대전/방전으로 인한 ESD 이벤트를 시뮬레이션하기 위한 것이다. 이러한 모델은 ESD 스트레스 레벨을 디바이스가 노출된 수준으로 제한하는 통제된 ESD 환경에서 조립, 최종 시험 및 보드 레벨 납땜이 실행되는 제조 환경에서 시험용으로 사용된다. 제조환경에서 IC는 일반적으로 2 kV HBM까지 ESD의 충격을 견딜 수 있도록 규격이 지정되지만 최근 낮은 지오메트리 디바이스의 규격은 500 V까지 낮춰졌다.

디바이스 레벨 모델은 일반적으로 공장 현장의 통제된 ESD 환경에 충분하다. 하지만 시스템 레벨 테스트에는 전혀 적합하지 않고, 전압과 전류로 인한 ESD 충격 레벨은 최종 사용자 환경에서 훨씬 크다. 이 때문에 업계는 IEC 61000-4-2 표준이 정의한 시스템 레벨 ESD 시험 방법을 사용한다. 디바이스 레벨 HBM, MM 및 CDM이 제조 공정에서 IC의 내구성만을 보장하기 위한 것이라면, IEC 61000-4-2 규정의 시스템 레벨 시험은 실제 상황에서 최종 사용자가 ESD 이벤트를 시뮬레이션하기 위한 것이다.

| [표 2] 디바이스 레벨 모델과 IEC 시스템 레벨 모델 비교 |

| HBM(인체 모델) | MM(기계 모델) | CDM (대전 디바이스 모델) | IEC 61000-4-2 모델 | |

| 정의 | 누적된 정전기를 방전하는 인체 | 누적된 정전기를 방전하는 로봇 팔 | 접지된 대전 디바이스 | 실제 ESD 이벤트 |

| 시험 레벨(V) | 500 - 2000 | 100 - 200 | 250 - 2000 | 2000 - 15000 |

| 펄스 폭(ns) | ~ 150 | ~ 80 | ~ 1 | ~ 150 |

| 2kV 적용 시 피크 전류(APK) | 1.33 | - | ~ 5 | 7.5 |

| 상승 시간 | 25 ns | - | < 400 ps | < 1 ns |

| 전압 스파이크 개수 | 2 | 2 | 2 | 20 |

IEC는 두 가지 시스템 레벨 시험, 접촉 방전과 공기 간극 방전에 대해 규정했다. 접촉 방전법에서 시험 시뮬레이터 전극은 DUT(시험 대상 디바이스, Device Under Test)와 접촉한다. 공기 간극 방전에서는 시뮬레이터의 대전된 전극이 DUT에 접근하고 DUT에 대한 스파크가 방전을 유도한다.

표 1은 각 방법에 대해 IED 61000-4-2가 규정한 시험 레벨 범위를 나타낸 것이다. 각 시험 레벨의 강도는 두 방법 사이에서 동일하지 않다는 점에 주목해야 한다. 스트레스 레벨은 일반적으로 실패 지점까지 각 방법의 공식 최고 레벨인 레벨 4 이상, 점진적으로 시험한다.

표 2에서 볼 수 있듯이, 디바이스 레벨 모델과 시스템 레벨 모델 사이에는 뚜렷한 차이점이 몇 가지 있다. 표 2의 마지막 세 파라미터, 전류, 상승 시간 및 전압 스파이크 개수가 특히 중요하다.

- 전류의 차이점은 ESD에 민감한 디바이스가 ESD 충격을 견딜 수 있는지 여부를 결정할 때 중요하다. 높은 전류 레벨이 접합부 피해 및 게이트 산화막 피해를 일으킬 수 있기 때문에 8 kV HBM(피크 전류 5.33A) 보호 칩이 2 kV IEC 모델(피크 전류 7.5 A)의 충격으로 인해 파괴될 수 있다. 따라서 설계자는 HBM 정격을 IEC 모델 정격과 혼돈하지 말아야 한다.

- 또 다른 차이점은 전압 충격 상승 시간에 있다. HBM에 규정된 상승 시간은 25 ns이다. IEC 모델에서 펄스의 상승 시간은 1 ns 미만으로 에너지의 대부분을 처음 30 ns로 방출한다. HBM 등급 디바이스가 대응하는 데 25 ns가 걸린다면 디바이스는 보호회로가 작동하기 전에 파괴될 수 있다.

- 시험 중 사용하는 충격 횟수는 모델마다 다르다. HBM은 양극 1회 및 음극 1회 충격만 시험하는 반면, IEC 모델에서는 양극 10회 및 음극 10회 충격을 사용한다. 첫 번째 충격을 견딘 디바이스가 첫 번째 충격에서 입은 피해로 인해 후속 충격에 파괴될 수 있다. 그림 1은 CDM, HBM 및 IEC 모델의 ESD 파형 예제를 보여준다. IEC 모델의 펄스가 각 디바이스 레벨 모델의 펄스보다 에너지가 확연히 높다.

TVS가 ESD 이벤트로부터 시스템을 보호하는 방법

ESD 보호 통합 구조 대신 IEC 61000-4-2 표준이 규정한 모델은 일반적으로 별도의 독립형 TVS(과도 전압 억제) 다이오드를 사용한다. 전원 관리 또는 마이크로컨트롤러에 통합된 ESD 보호 구조와 비교하여 독립형 TVS는 비용이 저렴하며, 그림 2와 같이 시스템의 I/O 커넥터에 가까이 설치할 수 있다.

TVS는 양방향 TVS와 단방향 TVS가 있다(그림 3 참조). 텍사스 인스트루먼트의 TPD1E10B06은 시스템 레벨 ESD 보호용 일반 데이터 라인에 설치할 수 있는 양방향 TVS의 예이다. 양방향 및 단방향 TVS는 모두 정상 동작 조건에서 개방 회로를 구성하고 ESD 이벤트 중 접지로 간략하게 설계되어 있다. 양방향 TVS의 경우, I/O 라인의 전압 신호는 D1 또는 D2가 파괴 영역으로 들어가지 않는 한 접지 초과 및 미만 사이를 움직일 수 있다. ESD 충격(양극 또는 음극)이 I/O 라인을 타격하면 한 다이오드는 정방향으로 바이어스되고 다른 다이오드는 파괴되어 ESD 에너지가 즉시 접지될 수 있는 경로를 생성한다. 단방향 TVS의 경우 전압 신호는 D2나 Z1이 파괴 영역으로 들어가지 않는 한 접지 위로 변동할 수 있다. 양극 ESD 충격이 I/O 라인을 타격하면 D1이 정방향으로 바이어스가 되고 D2 전에 Z1이 파괴 영역으로 들어가서 D1과 Z1 사이에 접지 경로가 생성되어 ESD 에너지가 방출하게 된다. 음극 ESD 충격이 타격하면 D2가 정방향으로 바이어스되고 ESD 에너지가 D2를 통해 접지되어 방출된다. D1과 D2가 기생 커패시턴스보다 작을 수 있기 때문에 단방향 다이오드는 고속 분야에 사용되고 D1과 D2는 교대로 큰 제너 다이오드 Z1을 “감춘다.” 여기서 Z1은 파괴 영역에서 전류를 더 많이 처리하기 위해 크기가 크다.

시스템 레벨 ESD 보호용 핵심 디바이스 파라미터

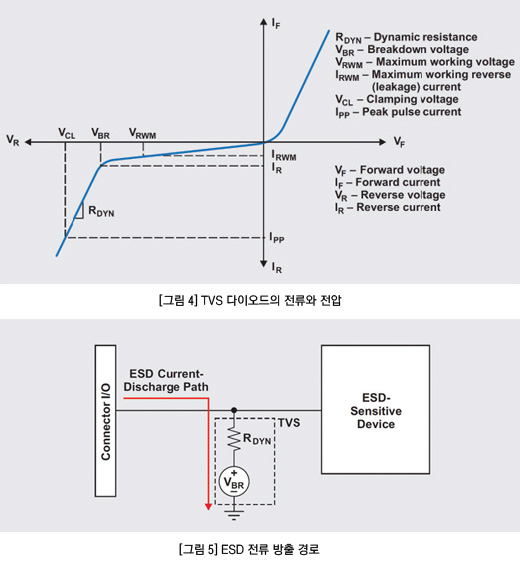

그림 4는 TVS 다이오드의 전류와 전압의 특징을 보여준다. TVS의 구조는 간단하지만 시스템 레벨 ESD 보호 설계 시 여러 중요한 파라미터를 고려해야 한다. 그러한 파라미터에는 파괴 전압 VBR , 동적 저항 RDYN , 클램프 전압 VCL 그리고 커패시턴스가 있다.

파괴 전압

적절한 TVS를 선택하는 첫 번째 단계로 파괴 전압(VBR)을 살펴보아야 한다. 예를 들어 최대 동작 전압 VRWM이 보호 I/O 라인에서 5 V이면 TVS는 이 최댓값에 도달하기 전에 파괴 영역에 들어가면 안 된다. 일반적으로 TVS 데이터시트에는, 특정 누설전류에 VRWM이 포함되어 있어 올바른 TVS를 쉽게 고를 수 있다. 그렇지 않을 경우 보호 I/O 라인의 VRWM보다 VBR(min)이 몇 볼트 더 높은 TVS를 선택하면 된다.

동적 저항

ESD는 나노초 단위로 발생하는 초고속 이벤트다. 이렇게 짧은 시간 동안 접지하여 TVS 전도 경로가 순간적으로 구축되며, 이 경로에는 약간의 저항이 존재한다. 동적 저항(RDYN)이라고 알려진 이 저항을 그림 5에 나타내었다.

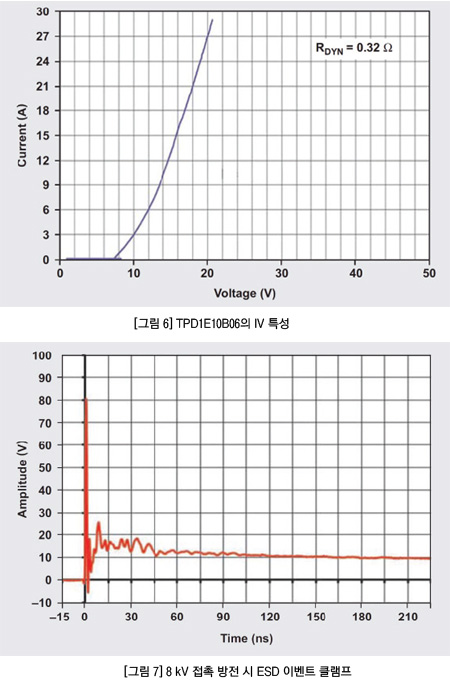

이상적으로 RDYN이 0이 되어 I/O 라인의 전압이 가능한 VBR와 같게 클램프되어야 하나 이는 불가능하다. RDYN의 업계 전류 표준 값은 1 Ω 미만이다. RDYN은 전송 라인의 펄스 측정법으로 파악할 수 있으며, 여기서 대전 전압이 TVS를 통해 방전되고 해당 전류가 측정된다. 서로 다른 전압으로 대전된 많은 데이터 포인트를 캡처한 후 그림 6과 같은 IV 곡선을 그릴 수 있으며 기울기는 RDYN이다. 그림 6은 TPD1E10B06의 RRDYN으로 일반적으로 이 값은 ~0.3 Ω이다.

클램프 전압

ESD는 찰나에 발생하는 이벤트이기 때문에 I/O 라인의 전압은 순간적으로 클램프되지 않는다. 그림 7에서 볼 수 있듯이 IEC 61000-4-2 표준에 따라 수천 볼트의 전압이 수십 볼트로 클램프된다. 식 1에서 RDYN이 낮을수록 클램프 성능이 우수하다.

VCL = VBR + IPP × RDYN + IParasitic × dIPP /dt (1)

여기서 IPP는 ESD 이벤트 중 피크 펄스 전류이며, IParasitic는 커넥터에서 TVS를 통해 접지로 배출되는 트레이스의 기생 인덕턴스이다.

클램프 전압 파형 아래 영역을 에너지라고 상상해보자. 클램프 성능이 좋을수록 보호 상태의 ESD 민감 디바이스가 ESD 이벤트 동안에 피해를 덜 받는다. 클램프 전압이 불량하기 때문에 일부 TVS는 IEC 모델의 8 kV 접촉 방전을 견디지만 “보호 대상” 디바이스는 파괴된다.

커패시턴스

정상 작동 조건에서 TVS는 개방 회로로 작동하고 기생 커패시턴스 션트가 접지되어 있다. 설계자는 신호 대역폭 예산에서 이 커패시턴스를 고려해야 한다.

결론

IC 공정 기술 노드가 소형화됨에 따라 제조 공정 및 최종 사용자 환경에서 모두 ESD 피해에 더욱 취약해졌다. 디바이스 레벨 ESD 보호는 시스템 레벨의 IC를 보호하기에 충분하지 않다. 따라서 독립형 TVS를 시스템 레벨 설계에 사용해야 한다. TVS를 선택할 때 설계자는 VBR, RDYN, VCL 및 커패시턴스와 같은 파라미터에 주의를 기울여야 한다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>