이 글에서 제시한 접근방식은 최상위 레벨에서 계층적 설계를 통해 신호 라우팅 혼잡을 해결하는 솔루션이다. 여기에는 파티션 크기를 가상으로 축소하고 ECO 모드에서 서브파티션 작업을 완결하는 새로운 개념이 도입됐다. 이를 통해 사이클 시간과 노력을 절감할 수 있다.

글 | 구린더 싱 바그리아(Gurinder Singh Baghria) 디자인 엔지니어

쿠샤그라 코왈(Kushagra Khorwal) 수석 디자인 엔지니어

나빈 쿠마르(Naveen Kumar) 선임 디자인 엔지니어

Freescale semiconductor, India Pvt Ltd.

경쟁이 심한 반도체 업계에서는 대부분의 기업이 단일 설계에 다수의 애플리케이션과 기능을 통합하려고 노력한다. 까다로운 다기능 설계에 대응할 수 있도록 SoC는 점점 더 복잡해지고 있으며, 계층적인 설계를 수행해야 할 필요성이 부각되었다. deep sub-micron 기술 노드에서 계층적 설계를 수행하는 데 가장 커다란 과제는 엄청난 수의 파티션이 있는 최상위 레벨에 대한 신호 라우팅 클로저와, 파티션의 대상 표준 셀 이용률을 결정하는 것이다. 설계 사이클의 초기 단계에서는 계층적 하위 블록/파티션의 표준 셀 이용률을 예측하는 것이 매우 어렵다. 서브파티션 사이의 영역을 할당할 때 예측/계획이 과다 또는 부족할 경우 각각 다이 면적 낭비 또는 사이클 시간 히트(cycle time hit)로 이어지게 된다. 정시에 설계를 완결하고 이 글에서 설명하는 유연하고 혁신적인 파티셔닝 전략을 배포하려면 복잡한 설계에 대해 효율적인 계획이 필요하다. 또한 서브파티션의 가상 영역 감소를 사용한 반복적인 공정에 진입하지 않고도 최상위 레벨의 라우팅 혼잡과 같은 후기 단계의 예기치 못한 상황을 줄일 수 있다.

계층적 설계에는 부모 계층 구조(parent hierarchy) 내에 다수의 서브파티션이 포함된다. 원활한 설계 완결이 이루어지려면 이러한 파티션이 설계 사이클의 초기 단계에서 계획되어야 한다.

아키텍처 레벨에서 파티션은 다음과 같은 하위 요소에 따라 결정된다.

- 애플리케이션/기능

- 전력 도메인 의존

- IP/소프트 모듈 딜리버리 날짜

구현 레벨에서는 파티셔닝을 해야 할 이유가 아주 많다.

- EDA 도구의 한계, 예를 들어 특정 게이트 수에 한정된 처리 용량

- 구현되어야 하는 특별한 절전 기법(바이어싱, 파워 게이팅, SRPG 등)

- 연결성 제한 요소

- 특별한 클로킹 제한 요소

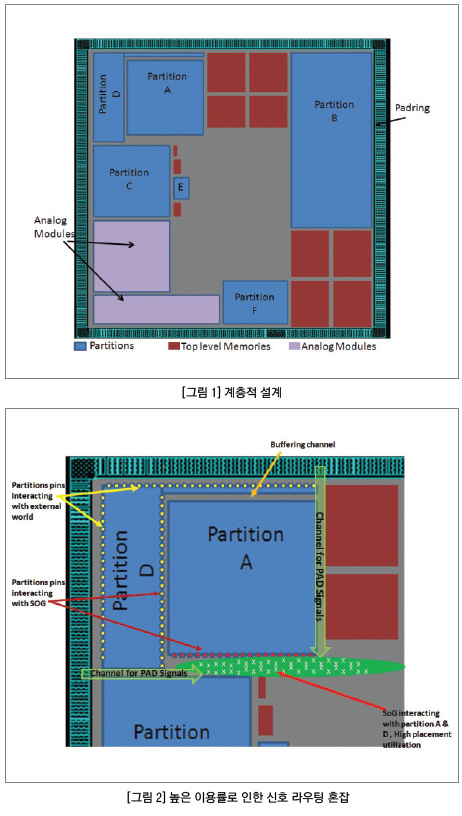

그림 1에 부모 계층 구조 내에 A, B, C, D, E, F란 이름의 서브파티션이 있는 계층적 설계가 나와 있다. 각 파티션은 단일 기능 또는 집합적인 기능 중 한 가지를 지원한다. 최상위 레벨 로직은 이러한 서브파티션과 함께 PMU, ADC, PLL, 발진기, 패드 링과 같은 아날로그 모듈로 구성된다. 다이의 중앙 위치는 대부분 더 빠르고 양호한 물리적 클로저가 가능하도록 최상위 레벨 SoG(Sea of Gates) 전용으로 사용된다.

문제 정의

계층적 설계에서는 블록들이 최상위 레벨에 통합된 후에 평면도의 품질이 분석된다. 이는 불필요한 반복 작업, 리소스 시간 낭비, 긴 사이클 시간 등으로 이어질 수 있으며, 결과적으로 시장 기회의 상실을 초래할 수 있다. 노드가 작아지는 기술 추세에 따라 표준 셀의 크기는 줄어들었지만 핀 수는 그대로 유지되고 있다. 따라서 높은 이용률로 설계를 완결하고 다이 면적을 절감하려면, 설계 내의 어딘가에 라우팅 혼잡이 일어나는 상황에 이르게 된다. 이용률이 주파수, 절전 기법, 게이트 수 등의 다양한 요소에 따라 결정되므로 초기 단계에서 이용률을 적절하게 예측하는 것은 매우 중요하면서도 어려운 일이다. 계획에 노력을 기울인 후에도 설계 프로세스에 일부 약점이 남아 있을 수 있으며, 이는 라우팅 혼잡을 포함하여 후기 단계의 예기치 못한 상황으로 이어진다. 이 글에서는 일반적으로 설계 내의 최상위 신호 라우팅 혼잡과 관련해 최고의 예가 될 수 있는 두 가지 사례를 다루며, 서브파티션의 배치와 라우팅이 완결되면 최상위 레벨 배치 또한 적절한 시기에 완결된다.

사례 1

최상위 레벨에 2개의 파티션을 나란히 배치해야 하는 시나리오를 가정해보자(그림 2 참조). 파티션 A와 D가 나란히 배치되는 상황이다.

파티션 D는 외부 세계와 그리고 칩 내부적으로 통신하기 위해 두 패드 링 모두와 직접 상호작용한다. 패드 링과 통신하려면 외부 세계와 상호작용하는 파티션 "D"의 핀을 위쪽 또는 왼쪽에 배치해야 한다(그림 2 참조). 최상위 레벨 SoG(Sea of Gates)와 상호작용하는 핀은 더 나은 타이밍을 확보할 수 있도록 오른쪽에 배치된다.

파티션 A 또한 최상위 레벨 SoG와 상호작용해야 하므로 원활한 SoG 상호작용에 최상의 핀 배치 위치는 파티션 A의 아래쪽이다(그림 2에 빨간색으로 표시).

이러한 시나리오에서 두 파티션 모두와 상호작용하는 최상위 레벨 게이트는 타이밍 사양을 만족할 수 있도록 경계 쪽으로 당겨져야 하며, 그 결과 녹색으로 표시된 영역의 배치 밀도가 높아진다. 이러한 상황은 신호 혼잡으로 이어진다. 이 문제를 해결하는 기존의 방법은 서브파티션의 크기를 줄여 최상위 레벨에서 리소스를 늘리는 것이었다. 이러한 조치가 설계 사이클의 후기에 수행된다면 생산 지연이 일어난다. 서브파티션의 크기를 줄이려면 파티션을 처음부터 완결해야 하며, 이는 복잡한 작업이고 서브파티션 클로저에 추가적인 리소스가 필요하게 된다.

사례 2

두 파티션이 그림 3과 같이 배치되어 있는 시나리오를 고려해보자. 시스템의 핵심 역할을 하는 파티션 E는 크기가 작으며 설계에 포함된 거의 모든 파티션과 상호작용한다. 따라서 여러 서브파티션이 손쉽게 액세스할 수 있도록 설계의 중앙부에 배치되어야 한다. 파티션 E를 파티션 C의 오른쪽에 배치하면 파티션 C의 작은 일부에만 겹치므로, 핀에 대한 타이밍 조건을 만족하려면 파티션 E로 가려지는 영역에서 파티션 C의 핀에 일종의 버퍼링 채널이 필요하다.

최상위 레벨 SoG의 배치 단계에서 파티션 C와 E는 일반적으로 타이밍 사양을 만족할 수 있도록 핀에 더 가깝게 배치되는 것이 바람직하다. 설계자는 라우팅 혼잡을 피할 수 있도록 배치의 제한을 시도할 수 있다. 그럼에도 셀의 높은 핀 수로 인해 파티션 E의 노치에서 라우팅 혼잡이 발생한다. 이 문제를 해결하려면 설계자에게 면적과 라우팅 측면에서 더 많은 리소스가 필요하다. 여기에는 블록 크기를 축소하여 최상위 레벨에서 일부 면적을 풀어내고 축소된 크기로 처음부터 블록 클로저 작업을 다시 진행하는 반복적인 프로세스가 필요하다.

접근 방식 제안

이러한 한계의 해결책은 이 글에 요약된 계층적 설계를 위해 유연하고 혁신적인 파티셔닝 전략을 도입하는 데 있다. 파티션의 속성은 COVER 셀로 정의할 것이다. 파티션의 배치 및 라우팅(Placement and routing)은 최상위 레벨 배치의 변경 없이 ECO(설계 변경 지시서) 모드에서 재완결 된다. 제시된 클로저 기법은 최상위 레벨(배치 동결) 및 블록 레벨(ECO 모드) 구현으로 세분된다.

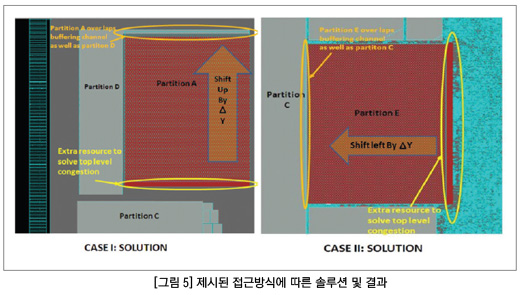

사례 1의 블록 레벨 구현을 다시 검토해보자. 최상위에서 결합되었을 때 파티션 A의 아래쪽에서 혼잡이 발견됐다. 이러한 혼잡을 해결하려면 설계자가 최상위 면적과 관련하여 일부 리소스를 풀어내도록 파티션 A를 조작해야 한다. 앞서 논의한 대로, 파티션의 크기를 줄이면 전체 블록 클로저 작업이 재설정되며 재완결에 추가 리소스가 필요하게 된다. 제시된 접근방식은 블록 크기의 가상 축소를 기반으로 한다. 이는 실제 블록 폭/높이를 변경하거나 블록 레벨의 배치 및 라우팅을 크게 변경하지 않으면서 블록에서 면적을 확보하고 혼잡 영역에서 최상위에 일부 공간을 할당함을 의미한다. 이는 표준 셀이 배치되지 않으며 신호가 라우팅되지 않는 배치 및 라우팅 차단 구역을 사용하여 블록 내에 빈 공간을 생성함으로써 가능하다.

파티션 A의 평면도가 그림 4에 나온 것과 유사한 것으로 가정하자.

파티션 A의 아래쪽을 따라 핀이 배치되어 있으므로, 여기에서는 할 수 있는 조치가 없다. 파티션 A에서 일부 영역을 확보하려면 남아있는 유일한 옵션은 메모리와 일부 로직 셀이 배치된 파티션의 위쪽뿐이다. 위쪽에서 영역을 확보하려면 파티션 A의 위쪽에 배치 및 라우팅 차단 구역을 형성하고 메모리를 이러한 차단 구역 밖으로 옮겨야 한다(그림 4에 나온 것처럼 아래로 이동). 이제 처음부터 전체 클로저 작업을 다시 수행하는 것이 아니라, 차단 구역 내에 있는 표준 셀의 배치 및 라우팅만이 재배치 및 재라우팅되도록 ECO 모드에서 배치 및 라우팅 작업을 수행한다. 그러면 위쪽에 흰색 공간이 생기며, 블록을 Y에서 Y = Y - 위쪽에서부터 ΔY 만큼 가상으로 축소한 것으로 볼 수 있다.

사례 2와 유사하게 핀 배치는 파티션 E의 오른쪽, 위쪽, 아래쪽에 이루어진다. 오른쪽에서는 할 수 있는 조치가 없다. 이 파티션에서 영역을 확보하려면 파티션 A에서 수행했던 것과 같은 절차를 파티션 E의 왼쪽에서 수행해야 한다. 그러면 파티션 E의 왼쪽으로 약간의 흰색 공간이 생기게 되며, 이는 블록을 X에서 X - 왼쪽에서부터 델타 X 만큼 가상으로 축소한 것으로 볼 수 있다.

블록 레벨 구현이 완료되면 블록에서 확보한 영역을 최상위 레벨에 활용할 수 있다. 제시된 이 방식으로는 블록에서 확보한 영역을 최상위 레벨 혼잡 해결에 직접 활용할 수 없다. 최상위 레벨 배치를 변경하지 않고 이 영역을 최상위 레벨에 활용하려면 몇 가지 지능적인 최상위 레벨 구현이 필요하다.

사례 1에서는 파티션 A의 위쪽에서 약간의 면적을 끌어내 최상위 레벨에 활용했다. 아래쪽에 있는 혼잡 영역 내에서 리소스를 사용할 수 있도록 만들려면 파티션 A를 위쪽 방향으로 이동해야 한다. 그렇게 하면 파티션 A가 인접한 두 채널 사이의 버퍼링 채널 또는 다른 파티션과 겹치게 된다. 해당 파티션은 비어 있으므로 이러한 이동 조치로 인해 최상위 레벨 또는 다른 파티션과 DRC가 발생하지는 않는다.

사례 2도 마찬가지다. 혼잡을 해결하려면 블록을 왼쪽으로 이동해야 한다.

이 방식을 사용하면 최상위 레벨에서 혼잡을 해결하는 데 상당히 많은 영역을 사용할 수 있다. 라우팅 혼잡이 해결된 후, 마지막으로 동적 전력 안정성과 N-well 연속성을 유지하려면 설계 내에 DECAP 및 FILLER를 배치해야 한다. 이러한 파티션에서는 버퍼링 채널이었던 영역에 DECAP 및 FILLER를 배치할 수 없으며, 블록이“MACRO” 속성을 가지지만 최상위 레벨 배치를 변경하지 않았으므로 해당 영역에 일부 버퍼링 로직이 그대로 배치되어 이동으로 인해 파티션 아래로 숨겨지게 된다. FILLER 및 DECAP을 삽입하지 않으면 버퍼링 영역에서 비연속 NWELL에 DRC가 생성된다. 버퍼링 채널을 배치 가능하게 만들려면 파티션 속성을 “MACRO”에서 “COVER”로 변경해야 한다. 또한 파티션을 MACRO 셀에서 COVER 셀로 변환하면 파티션 사이에 DECAP 및 FILLER를 배치할 수 있게 된다. 블록 내부에서 영역 내의 최상위 레벨 배치가 활용되는 것을 방지하려면, 파티션 아래에 배치 차단 영역을 삽입하여 버퍼링 채널(일체의 변경 전에 파티션이 초기 배치되는 곳)을 제외한 블록 내부의 배치 가능 영역을 복제해야 한다. 제시된 접근방식에 따라 파티션 크기를 가상으로 축소하고 덜 반복적인 방법으로 혼잡을 해결하면서 설계를 완결할 수 있었다. ES

저자 소개

구린더 싱 바그리아(Gurinder Singh Baghria)는 Freescale semiconductor, India Pvt Ltd에서 설계 엔지니어로 근무하고 있으며 SOC 물리 설계 업무와 관련하여 2년 이상의 경력을 가지고 있다. 쿠샤그라 코왈(Kushagra Khorwal)은 인도 Freescale Semiconductor, Noida에서 SOC 물리 설계 문야의 수석 설계 엔지니어로 근무하고 있다. 나빈 쿠마르(Naveen Kumar)는 Freescale semiconductor, India Pvt Ltd에서 선임 설계 엔지니어로 근무하고 있으며 SOC 물리 설계 업무와 관련하여 4년 이상의 경력을 가지고 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>