MPC574x와 같은 프리스케일 32비트 쿼리바(Qorivva) 마이크로컨트롤러에 구현된 기능안전성 기능에 대해 소개한다. 이러한 기능 구현을 통해 최종 소비자는 자동차(ISO26262) 및 산업(IEC61508) 표준의 안전 준수를 달성할 수 있다.

글 | 아룬 미쉬라(Arun Mishra) 주임 설계 엔지니어,

마커스 바우마이스터(Markus Baumeister)

세이프티 아키텍트, 프리스케일 반도체

오늘날 자동차 업계에서는 차량 전장부의 결함으로 인한 시스템 고장 발생 위험을 최소화하기 위해 안전 조치를 강화하고 있다. 최근의 자동차는 ABS, 전자 조향 제어, 에어백 센서, 레이더 센서 및 기타 MCU에 크게 의존하는 섀시 관련 애플리케이션 등 다양한 핵심 안전 애플리케이션을 활용한다. 이러한 핵심적인 자동차 동작 요소에 사용되는 안전 MCU의 대부분은 그 안전 작동 여부가 인체 및 사회적 안전에 직접적으로 연결되므로 ISO26262(ASIL-D) 또는 IEC61508(SIL3) 표준을 준수해야 한다.

이 글에서는 MPC574x와 같은 프리스케일 32비트 쿼리바(Qorivva) 마이크로컨트롤러에 구현된 기능안전성 기능에 대해 소개한다. 이러한 기능 구현을 통해 최종 소비자는 자동차(ISO26262) 및 산업(IEC61508) 표준의 안전 준수를 달성할 수 있다.

기능안전성 요구사항

기능안전성은 결함이 있는 시스템으로 인해 발생하는 위험을 최소화하는 것과 관련이 있다. 시스템의 결함은 영구적 또는 일시적일 수 있는 하드웨어 및 소프트웨어 오류로 인해 발생한다. 다음은 오류가 발생했을 때 일어날 수 있는 반응이다.

ㆍ장애-위험(Fail-dangerous) : 장애가 발생하면 위험할 수 있는 경우

ㆍ장애-불일치(Fail-inconsistent) : 제시되는 결과가 장애 사례와 확연히 일치하지 않는 경우

ㆍ장애-정지(Fail-stop) : 장애가 발생하면 자체적으로 완전히 정지되는 경우

ㆍ장애-방지(Fail-safe) : 장애가 발생해도 안전한 상태로 유지 또는 복귀되는 경우

ㆍ장애-작동 가능(Fail-operational) : 장애가 발생해도 계속 정상적으로 작동하는 경우

ㆍ장애-무관(Fail-silent) : 장애가 발생해도 아무에게도 방해가 되지 않는 경우

ㆍ장애-표시(Fail-indicate) : 속한 환경에 장애가 발생했음을 알리는 경우

시스템 내에서 기능안전성의 구현은 일반적으로 장애를 전체 시스템 또는 운전자가 처리할 수 있는 예상된 반응으로 매핑하여 시스템 장애로 인한 위험을 최소화하는 것을 의미한다.

다음 절에서는 시스템 장애가 발생하는 경우 이러한 매핑(대부분 장애-표시)을 수행하는 프리스케일 시스템온칩(System-on-chip)에 구현된 다양한 기능안전성 요소에 대해 소개한다.

MCU 설계에서 핵심적인 안전 구현

자동차 안전 애플리케이션용으로 설계된 프리스케일 디바이스가 제공하는 몇 가지 핵심적인 안전 기능에 대해 심층적으로 설명한다.

코어 록스텝(Core Lockstep)

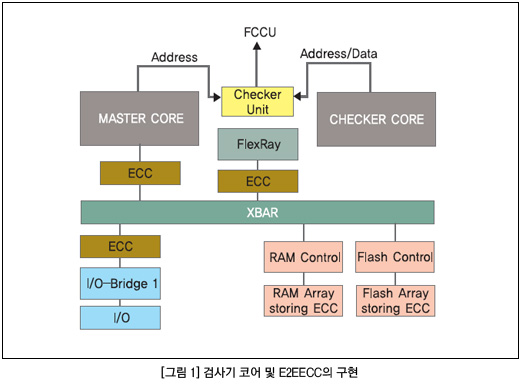

SoC 내에 코어의 안전한 동작을 보장하는 것은 기능안전성에서 가장 중요한 요구사항 중 하나이다. 쿼리바(Qorivva) 마이크로컨트롤러 MPC

574x의 경우, 마스터 코어와 록스텝으로 실행되는 검사기 코어(checker core)를 구현하여 이에 대응한다. 이는 검사기 코어가 마스터 코어와 동일한 명령을 실행하고, 검사기 유닛 내에서 각 코어의 주소와 데이터 버스를 비교하여 동작 상 편차를 감지하는 것을 의미한다. 감지된 오류는 FCCU(Fault Collection and Control Unit: 오류 수집 및 제어 장치)에 보고된다(그림 1 참조). 소프트웨어 측면에서 보면, 록스텝으로 인해 두 코어 모두 단일 코어처럼 동작하므로 SW 구현이 쉬워진다. 그림 1에 블록도가 나와 있다.

코어를 제외하고 eDMA, 인터럽트 컨트롤러, 캐시 등과 같은 또 다른 안전 관련 모듈은 시스템 내에서 복제할 수 있다. 이러한 복제는 다이(die) 상에서 물리적인 분리 상태를 유지하게 하여 CCF(Common Cause Faults: 공통 원인 오류)가 두 집합체의 동작에 유사하게 영향을 주는 일이 없도록 해야 한다.

메모리 내에서 E2ECC(End to End ECC) 구현

모든 메모리 저장 작업은 Hamming distance 4의 SECDED(Single Error Correct and Double Error Detect: 단일 오류 정정 및 이중 오류 감지)가 포함된 ECC(Error Correction Code: 오류 정정 코드)를 통해 보호된다. ECC는 데이터 및 주소 신호에 구현되며 쓰기 작업 도중 데이터와 함께 메모리에 저장된다. 읽기 작업이 시작되면 수신된 데이터와 요청된 주소에서 ECC가 재계산되며 저장된 ECC와 비교 검증된다.

쿼리바 MPC574x 디바이스의 경우, ECC가 메모리에만 국한되지 않으며 버스 마스터와 버스 클라이언트 사이의 모든 데이터 경로에서 최소 99% 이상의 유효 범위로 데이터 손상을 감지할 수 있는 E2ECC가 구현돼 있다. 그 메커니즘은 다음과 같다.

1) 마스터에서 나온 데이터가 ECC-SECDED 코드를 사용해 인코딩된다. 이 데이터 인코딩에는 주소 정보의 범위가 포함된다.

2) 경로 상의 개별 모듈에는 제어 데이터의 정확한 전송과 정확한 주소 디코딩을 보장하는 등의 로컬 메커니즘이 포함된다.

위와 같은 접근 방식은 데이터 경로에서 데이터 손상이 없음을 보장할 수 있다. 그 다음 마스터에서 제공한 ECC를 RAM과 플래시에서 사용하므로 메모리에 대한 추가적인 ECC 계산이 필요하지 않으며 ECC가 종단(버스 마스터)에서 종단(메모리)까지 적용된다.

시스템에는 SRAM, 주변기기 시스템 RAM, 플래시 메모리에 사용된 ECC 로직과 관련된 오류 이벤트를 수정하고 보고하는 중앙 MEMU(Memory Error Management Unit: 메모리 오류 관리 장치)가 있다. 수정 가능한(단일 비트) 오류 또는 수정 불가능한(멀티 비트) 오류가 발생하면 MEMU는 오류 신호를 수신하며 오류 주소가 기록되고 해당하는 오류 플래그가 설정되며 FCCU에 보고된다. 이는 수정된 수가 필요하거나 소프트웨어에 있는 오류를 추가로 분석하고자 하는 경우에 활용할 수 있다.

오류 수집 및 제어 장치(FCCU)

FCCU는 프로그래밍 가능한 장치로서 마이크로컨트롤러의 무결성 상태를 모니터링하며, 디바이스에 장애가 있을 경우 오류를 수집하고 통제 하에서 디바이스를 안전한 상태로 유도함으로써 유연한 안전 상태 제어 기능을 제공한다. 수집 및 제어 작업에는 CPU의 개입이 필요하지 않다.

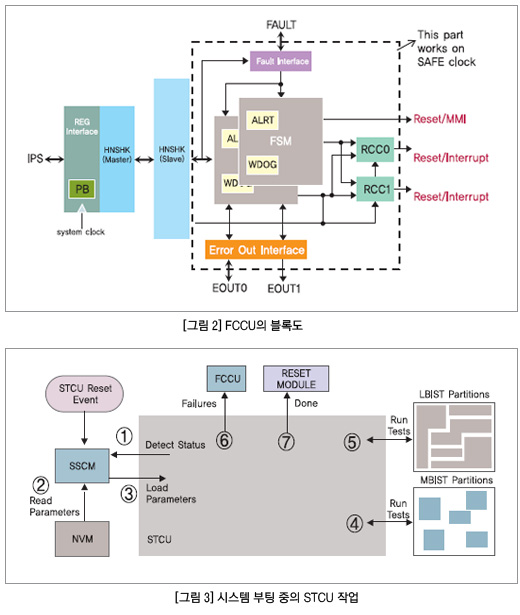

FCCU의 간략한 블록도가 그림 2에 나와 있다.

FCCU는 시스템 내에서 발생하는 오류와 그에 대한 조치/무조치를 기준으로 한 상태에서 다른 상태로 전환되는 유한 상태 머신을 구현한다. 오류 구성에 따라 FCCU는 리셋, 마스크 가능/마스크 불가능한 인터럽트, 외부 장애 표시를 트리거하거나 아무런 반응도 일어나지 않도록 한다. 외부 표시의 경우 다양한 정적 또는 토글 형태의 프로토콜에서 시스템 내에 발생한 오류에 대해 외부 환경과 통신할 수 있도록 SoC에 2개의 핀(EOUT0/1)이 제공된다.

자체 테스트 제어 장치

애플리케이션 실행 도중 작업을 손상시킬 수 있는 잠재적인/휴지 중인 오류가 디바이스에 존재하지 않음을 보장할 수 있도록 부팅/종료 시기에 실행되는 자체 진단 기능이 있다(그림 3 참조). 일반적으로 자체 테스트는 디지털 로직(LBIST라 부름)과 임베디드 메모리(MBIST라 부름)에서 실행되며 시스템에 필요한 SIL(안전 무결성 수준)을 충족하는 데 충분한 적용 범위를 가진다.

1. STCU 리셋 이벤트 후에 SSCM은 디바이스의 자체 테스트가 아직 실행되지 않았음을 감지한다.

2. SSCM은 비휘발성 플래시 메모리(NVM)에서 자체 테스트 매개변수를 읽어온다.

3. SSCM은 자체 테스트 매개변수를 STCU에 로드하고 STCU에 제어권을 넘긴다.

4. STCU는 MBIST를 관리하고 내부 상태를 업데이트한다.

5. STCU는 LBIST를 관리하고 내부 상태를 업데이트한다(다른 LBIST 및 MBIST의 순차 또는 병렬 실행도 가능함).

6. 오류가 감지되면 STCU는 테스트 장애를 FCCU에 보고하거나 디바이스를 리셋한다.

7. 자체 테스트가 완료되면 STCU는 리셋 모듈에 신호를 전달하고 부트 시퀀스가 다음 단계로 진행된다.

클록 감독 및 보조 클록

안전 작동 중에 외부 및 내부 클록 회로 내의 장애를 감지할 수 있도록 기본 클록이 보조 클록에 의해 감독(그림 4 참조)된다. 이 보조 클록은 디바이스가 리셋에서 빠져나오는 즉시 사용 가능하게 되는 내부 RC 발진기에 의해 제공된다. 이 클록이 사용 가능함에 따라 어떠한 이유로든 내부 PLL에 장애가 생기더라도 안전 메커니즘 대부분을 구동하여 계속 작동되도록 할 수 있는 클록이 시스템에 확보된다. 이 IRC 발진기는 PVT(프로세스, 전압, 온도) 전반에서 클록 일관성을 유지할 수 있도록 트림(trim) 가능하다.

쿼리바 MPC574x 디바이스의 경우, ECC가 메모리에만 국한되지 않으며 버스 마스터와 버스 클라이언트 사이의 모든 데이터 경로에서 최소 99% 이상의 유효 범위로 데이터 손상을 감지할 수 있는 E2ECC가 구현돼 있다. 그 메커니즘은 다음과 같다.

클록 모니터 장치(CMU)

CMU(Clock Monitor Unit)은 시스템 PLL 출력 주파수를 감시하고, 클록 손실이 있거나 모니터링 대상 클록이 상한 또는 하한 주파수 경계를 벗어나면 장애, 리셋 또는 인터럽트 신호를 보내는 모듈이다. CMU는 보조 클록(위 참조)을 레퍼런스로 사용하여 클록을 모니터링하며, 외부 크리스털 발진기와 대조하여 보조 클록을 모니터링하는 수단도 제공한다.

CMU의 간략한 블록도가 그림 4에 나와 있다.

그림 4에 나타낸 바와 같이, CMU는 모니터링 대상 클록에서 발진기 클록 손실 이벤트 또는 주파수 높음/주파수 낮음 이벤트가 발생하는 경우 리셋 모듈과 FCCU 모듈에 신호를 보낸다. 리셋 모듈에 대한 경로는 FCCU가 일정 시간 동안 반응을 보이지 않을 경우에만 활성화된다. 따라서 리셋 모듈과 FCCU 모듈 양쪽에 대한 신호 경로는 FCCU에 장애가 발생해도 모든 장애 보고가 차단되지 않도록 하는 예비 장애 표시 경로를 MCU 내에서 구성한다. FCCU 모듈에 적용된 구성에 따라 이벤트가 인터럽트 또는 리셋을 발생시킬지 여부가 결정된다.

전원 관리 컨트롤러(PMC)

쿼리바 MCU에 구현된 PMC(Power Management Controllers)는 전압 모니터링 회로와 BIST를 사용한다. 또한 LVD(저전압 감지)와 HVD(고전압 감지)의 두 가지 전압 모니터 유형이 구현되어 있다. 모든 안전 관련 전압은 내부적으로 전압이 범위를 벗어나지 않도록 관리된다.

PMC에 구현된 BIST는 시동 시 또는 소프트웨어를 통해 PMC의 주요 밴드갭(bandgap) 전압 및 기타 기능을 테스트한다.

안전 관련 전압의 장애는 MCU의 장애 표시 메커니즘이 반응하기 전에 이를 비활성화 할 수 있으므로, 전압 오류 표시는 FCCU의 개입 없이 디바이스가 직접 장애 방지(fail-safe) 상태(리셋 확정)로 전환되도록 만든다.

결론

디바이스에 기능안전성을 구현하려면 MCU에 리던던시 기능을 갖춰야 하며, 이는 소비 전력과 다이 크기의 증가로 이어질 수 있다. 하지만 강력한 하드웨어 시스템과 관련된 장점(MCU가 자체적으로 장애 방지, 장애 무관 또는 장애 표시 상태를 제공할 수 있음)이 있으며, 특히 소프트웨어의 복잡성을 낮추는 측면에서 그러하다. 지금까지 프리스케일 쿼리바 MCU에 구현된 다양한 안전 설계에 대해 소개했다. 디바이스에 이러한 안전 기능을 구현함으로써 애플리케이션에 ASIL/SILx 규정 준수를 달성할 수 있다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>