FPGA를 사용해 대규모 테스트 데이터 세트를 처리하면, 엔지니어가 신속하게 알고리즘을 평가하고 상반 관계를 구성할 수 있다. 또한 HDL 시뮬레이션에 따르는 시간적인 불이익 없이 실제 시나리오에 따라 설계를 테스트할 수 있다. MATLAB 및 Simulink를 통해 FPGA 프로토타입을 제작하는 모범 사례를 설명한다.

글 | 스테판 반 베크(Stephan van Beek)*, 애플리케이션 엔지니어

수디르 샤마(Sudhir Sharma), 제품 마케팅 매니저

수딥파 프라카시(Sudeepa Prakash)***, 제품 마케팅 매니저

매스웍스

칩 설계 및 검증 엔지니어는 실리콘에서 구현되는 RTL 코드의 모든 라인에 많게는 10개 라인의 테스트벤치 코드를 작성해야 하는 경우가 많다. 이들은 설계 주기의 50% 이상을 검증 작업에 소모한다. 이러한 노력에도 약 60%의 칩에 기능적 결함이 발생하고 re-spin이 필요하게 된다.1 HDL 시뮬레이션은 시스템 수준 오류를 파악하는데 충분하지 않기 때문에, 칩 설계자들은 이제 FPGA를 활용해 알고리즘 작성과 프로토타이핑을 가속하고 있다.

FPGA를 사용해 대규모 테스트 데이터 세트를 처리하면, 엔지니어가 신속하게 알고리즘을 평가하고 상반 관계를 구성할 수 있다. 또한 HDL 시뮬레이션에 따르는 시간적인 불이익 없이 실제 시나리오에 따라 설계를 테스트할 수 있다. MATLAB 짋 및 Simulink 짋와 같은 시스템 수준 설계 및 검증 도구는 엔지니어가 신속하게 FPGA에서 알고리즘을 프로토타이핑함으로써 이러한 이점을 실현할 수 있게 돕는다.

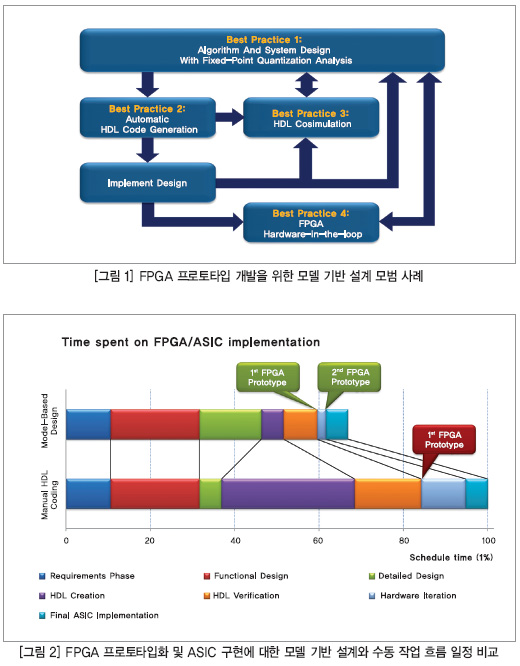

이 글은 MATLAB 및 Simulink를 통해 FPGA 프로토타입을 제작하는 모범 사례를 설명한다. 모범 사례는 아래 목록에 열거했으며 그림 1에 강조해서 표시되어 있다.

(1) 고정소수점 양자화의 효과를 설계 과정 초기에 분석하고 워드 길이(word length)를 최적화해 보다 규모가 작고 전력 효율적인 생산을 구현

(2) 자동 HDL 코드 생성을 사용해 더욱 빠르게 FPGA 프로토타입 생산

(3) HDL 통합 시뮬레이션을 통해 시스템 수준 테스트벤치를 재사용해 시스템 수준 매트릭으로 HDL 구현을 분석

(4) FPGA-in-the-loop 시뮬레이션을 통해 검증 가속

FPGA에서 프로토타입을 개발하는 이유

FPGA에서 알고리즘을 프로토타이핑하면, 엔지니어는 자신의 알고리즘이 실제 구현될 때 예상대로 작동하리라는 것을 보다 확신할 수 있다. 또한 테스트 벡터와 시뮬레이션을 고속으로 실행할 뿐만 아니라, 엔지니어는 FPGA 프로토타입을 사용해 소프트웨어 기능과 RF, 아날로그 서브시스템 등의 인접 시스템 수준 기능을 실행할 수 있다. 또한 FPGA 프로토타입은 더욱 빠르게 실행되고 더 큰 데이터 세트를 사용할 수 있기 때문에, 시뮬레이션 모델로는 발견하기 어려운 버그를 발견할 수 있다.

HDL 코드 생성을 사용한 모델 기반 설계는 그림 2와 같이 엔지니어가 효율적으로 FPGA 프로토타입을 생산할 수 있게 한다. 그림 2는 엔지니어가 개발 일정을 준수할 수 있도록 하기 위해서 상세 설계 단계를 축소하고 하드웨어 개발의 실질적인 시작을 앞당기는 현실을 보여준다. 이에 대한 결과로서 엔지니어는 고정소수점 알고리즘이 시스템 요구사항을 충족시키지 못함을 종종 발견하게 되어 HDL 작성 단계 중 상세한 설계 단계를 다시 검토해야 한다. 이러한 중복 작업은 긴 보라색 막대로 표현한 것처럼 HDL 작성 단계를 길어지게 만들고 글루 로직(glue logic) 또는 설계 패치와 같은 타협으로 이어질 수 있다.

엔지니어는 자동 HDL 코드 생성이 수동 코딩보다 빠르기에, 절감된 시간을 상세한 설계 단계에서 더 높은 품질의 고정소수점 알고리즘을 만드는 데 투자할 수 있다. 이러한 접근방식은 엔지니어가 더 높은 품질의 FPGA 프로토타입을 수동 워크플로에 비해 빠르게 생산할 수 있게 한다.

디지털 다운 컨버터 사용 사례

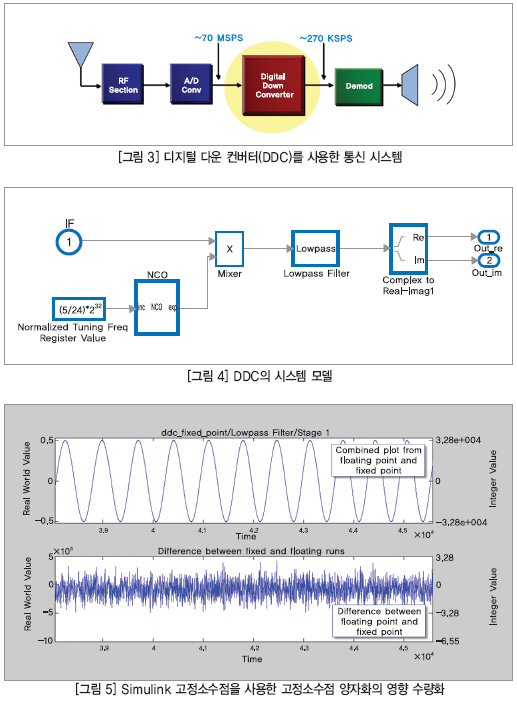

디지털 다운 컨버터(Digital Down Converter, DDC)는 모델 기반 설계를 사용한 FPGA 프로토타이핑 모범 사례를 설명하기 위한 유용한 사례 연구이다. DDC는 다양한 통신 시스템에서 공통적인 빌딩 블록이다(그림 3 참조).이것은 낮은 샘플 속도 클록을 사용해 처리할 수 있도록 고속 통과대역 입력을 저속 베이스밴드 출력으로 변환하는 데 사용한다. 따라서 전력과 리소스 요구사항이 낮은 하드웨어 구현이 가능하다.

DDC의 기본 구성요소(그림 4 참조):

- 수치 제어 발진기(NCO)

- Mixer

- 디지털 필터 체인

사례 #1 - 설계 프로세스 초기에 고정소수점 양자화의 영향 분석

엔지니어는 일반적으로 부동소수점 데이터형을 사용해 새로운 아이디어를 테스트하고 초기 알고리즘을 개발한다. 하지만 FPGA와 ASIC에서 하드웨어를 구현하려면, 고정소수점 데이터형으로 변환해야 하기에 양자화 오류가 발생하는 경우가 많다. 수동 워크플로에서 고정소수점 양자화는 일반적으로 HDL 코딩 프로세스 중에 이뤄진다. 해당 워크플로에서 엔지니어는 고정소수점 설계를 부동소수점 참조 설계와 비교해 고정소수점 양자화의 영향을 쉽게 수량화하기 어렵다. 또한 오버플로에 대한 HDL 구현을 분석하기도 쉽지 않다.

필요한 소수점 이하 자릿수(fractional length)에 대한 현명한 의사결정을 위해서는 HDL 코딩 프로세스를 시작하기 전에 엔지니어가 부동소수점 시뮬레이션 결과를 고정소수점 시뮬레이션 결과와 비교하는 방법이 필요하다. 소수점 이하 자릿수를 늘이면 양자화 오류가 줄어든다. 하지만 워드 길이 또한 늘어나야 한다(칩 면적과 전력 소모 증가).

예를 들어, 그림 5는 DDC 필터 체인에서 저역통과 필터 1단계에 대한 부동소수점과 고정소수점 시뮬레이션의 결과 차이를 설명한다. 이러한 차이는 고정소수점 양자화로 인한 것이다. 상단 그래프는 부동소수점과 고정소수점 시뮬레이션 결과의 중첩을 보여준다. 하단 그래프는 플롯의 모든 지점에서 양자화 오류를 보여준다. 설계 사양에 따라 엔지니어는 양자화 오류 수를 줄이기 위해 소수점 이하 자릿수를 늘여야 할 수도 있다.

소수점 이하 자릿수 선택뿐 아니라, 엔지니어는 워드 길이를 최적화해 전력 소모가 낮고 공간 효율적인 설계를 실현해야 한다.

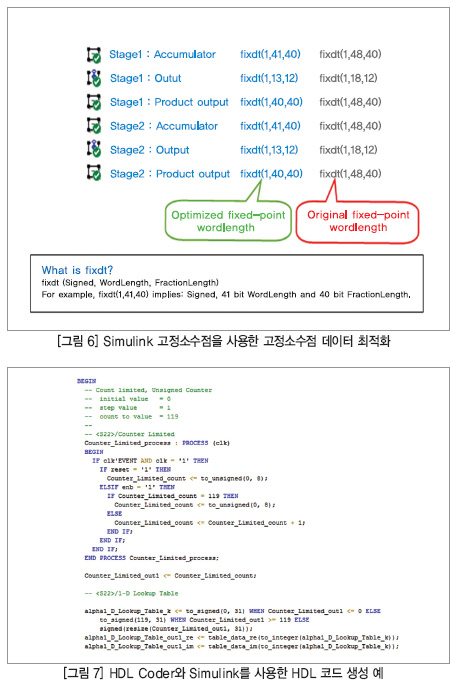

DDC 사례 연구에서 엔지니어는 Simulink Fixed Point™을 사용해 디지털 필터 체인 일부의 워드 길이를 최대 8비트만큼 줄여야 한다(그림 6 참조).

DDC 사례 연구에서 엔지니어는 Simulink Fixed Point™을 사용해 디지털 필터 체인 일부의 워드 길이를 최대 8비트만큼 줄여야 한다.

사례 #2 - 자동 HDL 코드 생성을 사용해 더욱 빠르게 FPGA 프로토타입 생산

FPGA 프로토타입을 만들기 위해서는 HDL 코드가 필요하다. 그 동안 엔지니어는 Verilog 또는 VHDL 코드를 수동으로 작성했다. 이에 대한 대안으로 HDL Coder™를 사용해 HDL 코드를 자동으로 생성하는 것은 몇 가지 중요한 이점을 제공한다. 엔지니어는 다음과 같은 일을 할 수 있다.

- 알고리즘을 하드웨어에서 구현할 수 있는지 빠르게 평가

- 다양한 알고리즘 구현을 신속하게 평가하고 최적의 구현을 선택

- 더욱 빠르게 FPGA에서 알고리즘을 프로토타이핑

DDC 사례 연구에서 55초 만에 5,780개의 라인의 HDL 코드를 생성했다. 엔지니어가 코드를 읽고 즉시 이해할 수 있다(그림 7 참조). 엔지니어가 자동 코드 생성을 통해 시스템 수준 모델에서 변경을 하고 HDL 코드를 다시 생성함으로써 몇 분 만에 업데이트된 HDL 구현을 생산할 수 있다.

HDL 시뮬레이션은 디지털 파형 출력만 제공하지만, HDL 통합 시뮬레이션은 HDL 코드에 대한 완벽한 가시성은 물론 Simulink의 모든 시스템 레벨 분석 툴에 대한 액세스를 제공한다.

사례 #3 - HDL 검증을 위한 통합 시뮬레이션으로 시스템 수준 테스트벤치 재사용

기능 검증

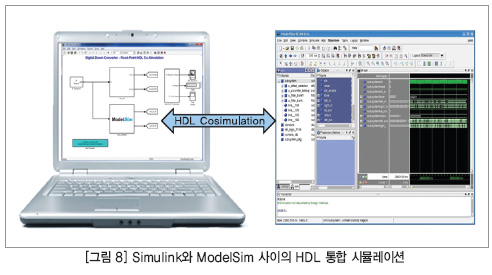

HDL 통합 시뮬레이션은 엔지니어가 Simulink 모델을 재사용해 HDL 시뮬레이터로의 입력을 유도하고 대화식으로 시뮬레이션 출력의 시스템 수준 분석을 수행할 수 있게 한다(그림 8).

HDL 시뮬레이션은 디지털 파형 출력만 제공하지만, HDL 통합 시뮬레이션은 HDL 코드에 대한 완벽한 가시성은 물론, Simulink의 모든 시스템 레벨 분석 툴에 대한 액세스를 제공한다. 엔지니어가 예상 결과와 HDL 시뮬레이션 결과의 차이점을 발견했을 때 통합 시뮬레이션은 이러한 불일치가 갖는 시스템 수준 영향을 더욱 잘 이해할 수 있도록 돕는다.

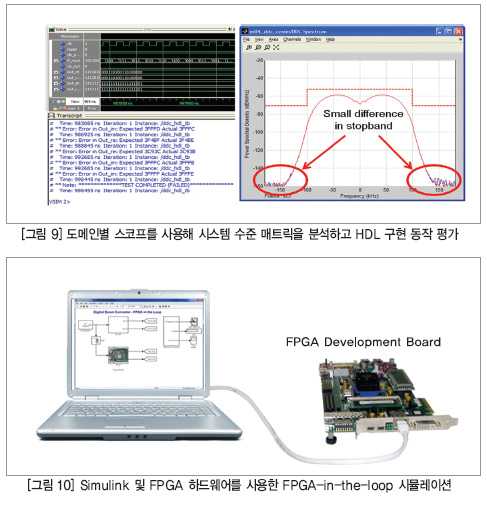

예를 들어 그림 9에서 Spectrum Scope 표시창은 불일치점이 저지 대역(Stop Band)에 위치하므로, 그러한 정보에 입각해 엔지니어가 예상 결과와 HDL 시뮬레이션 결과의 불일치를 무시하도록 결정할 수 있게 한다. 반면 디지털 파형 출력은 예상 결과와 HDL 시뮬레이션 결과의 불일치를 오류로 표시할 뿐이다. 엔지니어가 얻은 결론은 같을 수 있지만 필요한 분석을 수행하는 데 더 많은 시간이 걸릴 것이다.

테스트 커버리지

엔지니어는 HDL Verifier, Simulink Design Verifier 및 ModelSim/Questa를 사용해 코드 커버리지 분석을 자동화할 수 있다. 이 워크플로에서 Simu

link Design Verifier는 모델 커버리지에 대한 테스트 케이스를 생산한다. HDL Verifier는 이러한 테스트 모음을 통해 자동으로 ModelSim/Questa를 실행해 생성된 코드의 전체 분석에 대한 코드 커버리지 데이터를 수집한다.

사례 #4 - FPGA-in-the-Loop 시뮬레이션을 통해 검증 가속

시스템 레벨 시뮬레이션과 HDL 통합 시뮬레이션을 사용해 DDC 알고리즘을 검증했다면, 이제 DDC 알고리즘을 FPGA 타깃 플랫폼으로 배포할 수 있다. 알고리즘의 FPGA 기반 검증(FPGA-in-the-loop 시뮬레이션이라고도 함)을 통해 실제 구현에서 알고리즘의 작동을 더욱 확신할 수 있다. 따라서 엔지니어가 호스트 기반 HDL 시뮬레이션에 비해 더욱 빠르게 테스트 시나리오를 실행할 수 있다.

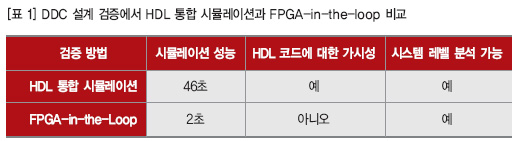

DDC 알고리즘에 대해 Simulink 모델을 사용해 FPGA 입력을 유도하고 FPGA 출력을 분석할 수 있다(그림 10). HDL 통합 시뮬레이션과 마찬가지로 언제나 분석을 위해 Simulink에서 결과를 확인할 수 있습니다.

표 1은 DDC 설계에 사용되는 HDL 통합 시뮬레이션과 FPGA-in-the-loop 시뮬레이션의 두 가지 검증 방식을 비교한 것이다.

이 경우 FPGA-in-the-loop 시뮬레이션은 HDL 통합 시뮬레이션보다 23배 빠르다. 이처럼 빠른 속도는 엔지니어가 더욱 광범위한 테스트 케이스를 실행하고 설계에 대해 회귀 테스트를 수행할 수 있게 한다. 따라서 보다 상세한 분석으로 필요한 문제 영역을 파악할 수 있다.

HDL 통합 시뮬레이션은 느리지만 HDL 코드에 대한 더 많은 가시성을 제공한다. 따라서 FPGA-in-the-loop 시뮬레이션 중 발견되는 문제 영역의 보다 상세한 분석에 적합하다.

결론

엔지니어는 이 문서에서 설명한 4개의 모범 사례에 따라 기존의 수동 워크플로에 비해 더욱 빠르고 자신 있게 FPGA 프로토타입을 개발할 수 있다. 또한 엔지니어는 계속하여 개발 과정 전체에서 모델을 지속적으로 개선하고 FPGA 구현을 위한 코드를 신속하게 다시 생성할 수 있다. 이 기능은 수동 작성 HDL에 의존하는 기존 워크플로에 비해 훨씬 짧은 설계 반복을 가능하게 한다. ES

기술자료 키트 다운로드:

www.mathworks.co.kr/programs/techkits/techkit_asic_response.html

| MATLAB에서 자동 HDL 생성해 열 이미징 FPGA 개발 가속 매스웍스는 FLIR Systems가 MATLAB과 HDL Coder를 사용해 열 이미징 FPGA 개발 시, 콘셉트부터 프로토타입까지의 개발 시간을 60% 단축했다고 발표했다. FLIR은 알고리즘 설계, 시뮬레이션 및 평가에 MATLAB을 사용하고 FPGA에서 알고리즘을 신속하게 구현하는 데 HDL Coder를 사용했다. 이로써 개발 시간을 단축하고 단 몇 시간 만에 성능 개선을 완료했다. 또한 프로토타이핑 및 생산을 위해 코드를 재사용할 수 있었다. FLIR의 알고리즘 엔지니어는 하드웨어 엔지니어에게 사양을 적어 전달하는 대신 MATLAB과 HDL Coder를 사용해 직접 FPGA 프로토타입을 만들어 제공한다. 이러한 새로운 열 이미징 알고리즘 개발 워크플로우는 오류가 발생하기 쉬운 알고리즘을 HDL로 수동 변환하는 단계를 생략해 개발자가 설계 반복을 더 많이 시도할 수 있는 시간을 제공한다. 따라서 FLIR 알고리즘 엔지니어는 설계를 많이 시도해 최종 프로토타입에 대한 확신을 얻을 수 있으며 코드를 생산 단계에서 재사용할 수 있다. |

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>