12개 이상의 레일을 사용하는 복잡한 회로 보드에서 모든 전력관리 요구사항들을 충족시킬 수 있는 확장 가능한 인-시스템 갱신 가능 스타 토폴로지 전력관리 아키텍처에 대해 설명한다. 온-칩 FPGA의 전력관리 알고리즘을 손상시키지 않으면서 DC-DC 컨버터 출력 전압을 (온-칩 정밀도 비교기를 사용하여) 정확하게 모니터링하는데 Lattice Platform Manager와 Power Manager 디바이스를 사용함으로써 보드 기능 신뢰성을 강화할 수 있다.

보드 상의 파워서플라이의 수는 사용된 멀티-전원 VLSI의 수, 이들 간의 통신 속도, 그리고 사용된 메모리 기술 등과 같이 보드 상에서 특정한 전원 설정을 요구하는 기타 디바이스들에 의해 결정된다. 이것은 각각의 VLSI I(ASIC/SoC) 디바이스가 정상적으로 동작하기 위해서 다양한 전원(예컨대 코어 전원, I/O 전원, PLL 전원, SERDES 채널 전원, 메모리 인터페이스 전원)을 요구하기 때문이다. 따라서 회로 보드에 15개에서 25개까지의 레일이 있는 것은 그리 이상한 것도 아니다. 다양한 파워서플라이를 사용하는 보드는 일반적으로 전력 시퀀싱, 전원 고장에 대한 모니터링, 트리밍, 마지닝 등과 같은 전력관리 기능을 구현해야만 한다. 일부 보드들은 전압 스케일링, 전원 고장에 대한 비휘발성 로그 기록(non-volatile logging), 백그라운드 시퀀스 갱신 등과 같은 강화된 전력관리 기능을 요구할 수도 있다.

회로 보드 전력관리 요구사항

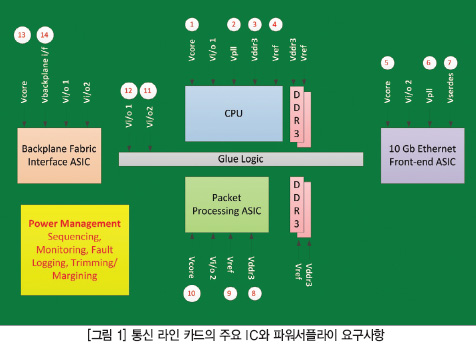

그림 1에 나타낸 라인 카드의 경우, 4개의 메인 IC와 일부 글루 로직(glue logic)이 있다. 이들 각각의 IC는 다양한 파워서플라이를 요구하며 시퀀싱 요구사항들을 가지고 있다. 이 보드는 모니터링, 시퀀싱, 트리밍, 마지닝되어야 하는 14개의 전원 레일을 가지고 있다. 뿐만 아니라, 보드 설계 역시 예상치 못한 파워서플라이 고장을 비휘발성 메모리에 기록할 것을 요구하고 있다.

보드의 전력관리 알고리즘을 초기에 설계할 때, 디바이스별 시퀀싱만을 고려한다. 이것은 보드 설계자들이 다양한 레일들 사이에서 전력 시퀀싱의 상호 의존성에 대해 파악할 수 없기 때문이다. 일반적으로 디버그 기간 동안 전력 시퀀싱을 완결하기 위해 프로그램 가능한 시퀀싱 솔루션은 원래의 시퀀싱 알고리즘에 대한 다음과 같은 변경 사항들을 수용할 수 있어야 한다.

- 각각의 레일 또는 그룹 레일을 온 상태로 전환할 때의 시간 지연

- 시퀀스 재배열 - 예를 들어 원래의 설계가 시퀀스 1, 2, 4, 5, 3을 가지고 있었다면 새로운 시퀀스는 시퀀스 2, 3, 5, 1, 4를 가질 수 있다.

- 파워다운 시퀀싱 - 반대의 순서로 전원을 오프 상태로 전환(이것은 IC에 대한 손상을 최소화하는데 필요하다)

- (다양한 레일을 필요로 하는) IC들에 대해 부분적으로 전력이 공급되는 조건들의 최소화 - 이것은 해당 디바이스에 대한 잘못된 전력에 의해 결정된다. 예를 들어 전원 3에 고장이 발생했다면, 전원 4를 즉시 오프 상태로 전환한 다음 전원 1과 전원 2를 오프 상태로 전환한다. 만약 전원 1에 고장이 발생했다면, 전원 2, 3, 4를 해당 시퀀스에 따라 오프 상태로 전환한다.

- 다양한 디바이스가 스타트 동작을 하도록 이들에 대한 파워 굿(Power Good) 표시 생성. 예를 들어 CPU는 코어 전원이 양호할 때만이 아니라 DDR 메모리 전원, PLL 및 I/O 전원이 양호할 때에도 파워 굿 신호를 필요로 한다.

- 시퀀싱을 완료하기 위해서 디지털 신호를 모니터링 할 수 있어야 한다. 예를 들어 DDR 파워서플라이의 파워업 단계를 진행하기 전에 패킷 처리 ASIC의 PLL 록(PPL lock)을 대기해야 한다.

- 디지털 제어 신호(또는 디지털 제어 신호의 논리적 조합)에 의해 전력 셧다운 개시 : 예를 들어 프런트 패널 셧다운 신호

모든 전원이 온 상태로 전환된 후 보드는 정상적으로 기능하기 시작하며, 전력관리 영역은 고장에 대비해 전원을 모니터링하기 시작해야 한다. 특정 전원에 고장이 발생한 경우에 - 어떤 전원이냐에 따라서- CPU를 중단시키거나 플래시 변형(Flash corruption)을 방지하기 위해서 리셋시켜야 한다. 전력관리 알고리즘의 모니터링 영역은 다음과 같은 특성을 제공해야 한다.

- 슈퍼바이저(supervisor)의 잘못된 관리 고장 표시를 최소화하고 누락된 전력 고장을 최소화하기 위해 1% 또는 그 이상의 정확도를 통해 특정 보드 실장 전원의 고장 식별. 이 고장 표시를 사용해 CPU에 대해 중단 리셋을 생성할 수 있다.

- 전력관리 회로와 보드 실장 파워서플라이 사이의 접지 전압 차이로 인한 에러를 최소화하기 위해서 차동 신호를 사용해 보다 낮은 전원 전압(1.5 V 이하) 감지

- 전원 고장으로 인해 발생한 잘못된 데이터 또는 명령의 지속 시간을 최소화하기 위해서 100 μs 이내에 고장 보고

- 관리 신호(supervisory signal)들을 고장과 상호 연결. 예를 들어 전원 1, 2, 3, 4 중에 하나에 고장이 발생하면 리셋 신호를 활성화시킨다. 하지만 전원 12에 고장이 발생하면, 잘못된 데이터 전송을 방지하기 위해서 CPU만을 중단시킨다.

고장 로그 기록 기능은 전체 보다 셧다운에 대한 주요 사유를 기록해야 한다. 회로 보드에서 초기 고장은 일반적으로 2차 동작을 유발한다. 예를 들어 전원 1에 고장이 발생하면, 보드 셧다운 기능이 파워다운 시퀀스에 의해 프로그램된 대로 나머지 전원들을 차단하기 시작한다. 고장 로그 기록 회로가 파워서플라이 1의 고장에 대해 신속하게 반응한다면, 획득된 이미지를 통해 전원 1에 고장이 발생하였고, 나머지 전원은 양호하다는 것을 확인할 수 있을 것이다. 하지만 고장 로그 기록 회로의 응답 시간이 느리다면, 전원 2, 3, 4 역시 고장이 발생한 것으로 기록될 것이다. 이와 같은 고장 이미지를 사용할 수는 없다. 고장 로그 기록 회로는 다음과 같은 특성을 제공해야 한다.

- 획득된 고장 이미지의 신뢰성을 증대시키기 위해서 모든 파워서플라이 고장의 위치를 정확하게 확인(< 1% error)

- 획득된 이미지에 오류를 발생시키는 원래 고장의 부차적인 영향을 최소화하기 위해서 고장 로그 프로세스를 100 μs 이내에 개시

전력관리 구현 예제

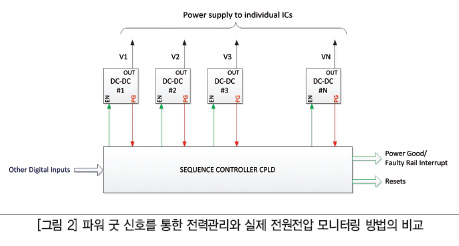

복잡한 전력관리 기능을 구현하기 위한 한 가지 일반적인 접근방법(그림 2)은 전원을 모니터링하기 위해 파워 굿 신호를 사용하고 시퀀싱 알고리즘(DC-DC 컨버터 이네이블 신호 제어)을 구현하기 위해 CPLD를 사용하는 것이다. CPLD는 파워-굿(Power-Good)/고장 레일 인터럽트(Faulty Rail Interrupt), 리셋 신호 등과 같은 관리 신호도 생성한다.

장점 :

- 모든 시퀀싱 요구사항들을 충족한다.

- 많은 수의 전원을 통해 확장 가능하다.

- 파워업 또는 파워다운 시퀀싱 알고리즘의 크기와 복잡도에 대한 제한이 없다.

- 시퀀싱 알고리즘은 파워서플라이 시퀀싱 간의 감독 신호(파워 굿/고장 전압 표시)들을 인터리빙 할 수 있다.

- 다양한 디지털 입력 수를 통해 시퀀싱 및 모니터링 알고리즘을 제어할 수 있다.

- 보드 동작을 중단시키지 않고 현장에서 시스템의 시퀀싱 알고리즘을 갱신할 수 있다.

단점 :

- 능동 “파워 굿” 신호가, 전원이 IC에 대해 알맞은 범위 내에 있다는 것을 의미하지는 않는다. 대부분의 DC-DC 컨버터의 파워 굿 신호는 8%에서 20%까지의 모니터링 에러 특성을 가지고 있다. 하지만 대부분 IC의 전원전압 허용 공차는 3~5% 사이다. 예를 들어 1.2 V 레일(코어 전원)의 실제 전압은 정격 값(1.08 V) 이하인 10%이지만, DC-DC 컨버터 파워 굿 신호는 전원이 양호하다고 표시해 CPLD가 리셋 신호를 활성화시키지 않을 수 있다. 결과적으로 CPU가 플래시 메모리(플래시 변형) 영역이 정지되거나 겹쳐 쓰기 된다. “리셋” 또는 “저전압 인터럽트(low voltage interrupt)” 등과 같은 관리 신호를 생성하는데 있어서 전원 레일 고장 표시로서 DC-DC 컨버터의 파워 굿 신호를 사용해서는 안 된다.

- 심지어 해당 파워서플라이 전압이 동작 허용 공차 내에 있지 않은 경우에도 종종 일부 IC가 활성화된다. 결과적으로 시퀀싱 알고리즘이 IC를 활성화하기 전에 추가적인 시간을 대기하게 되며 보드는 신뢰성 있게 스타트-업 하지 않는다.

- 소프트웨어 디버그 시간 증가 - CPU와 메모리 파워서플라이의 파워 굿 신호의 정확도가 낮아 플래시 변형이 발생할 수 있다. 잘못된 전원으로 인한 소프트웨어 버그와 예상치 못한 프로그램 동작을 구분하는 것은 매우 어렵다. 하드웨어의 잘못된 전원을 결정할 수 있는 방법이 없기 때문에 소프트웨어 엔지니어는 플래시 변형에 대해 고장 보드를 원인으로 판단하기 전에 소프트웨어 버그를 원인으로 판단해 시간을 허비하게 된다. 이것은 제품 출시 지연의 원인이 될 수 있다.

플랫폼 관리자를 통한 분산 감지 및 중앙 집중 제어 기능의 구현

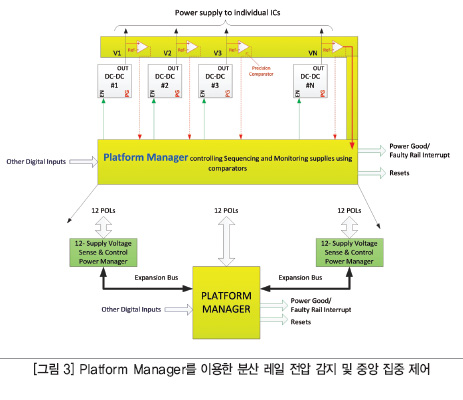

그림 3은 원격 감지 및 중앙 집중 제어 구현을 나타낸 것이다. 이 아키텍처는 그림 2에 제시한 회로 배치와 유사하다. 비교기(comparator)와 ADC를 통합함으로써 이 배치는 최소한의 부품만을 요구한다. 이 솔루션은 Lattice Platform Manager와 2개의 Lattice Power Manager IC를 사용해 최대 36개 레일의 전력관리 기능을 구현할 수 있다.

Lattice Platform Manager 디바이스는 12개의 전원전압 모니터링, 48개의 매크로셀 CPLD, 640개의 LUT FPGA를 통합하고 있다. Power Manager 디바이스는 최대 12개의 POL(Point of Load) 파워서플라이를 감지 및 제어하는 데 사용할 수 있다. 전체 전력관리 알고리즘은 Platform Manager의 FPGA 영역 내에 구현된다. Platform Manager 역시 전원의 트리밍과 마지닝을 지원한다.

장점 :

- 중앙 전력관리 기능을 FPGA에 구현했기 때문에 최대 36개의 레일에 대해 완벽하고 유연한 시퀀싱을 지원한다. 각 전력 고장 조건에 대한 타이밍 조정 또는 시퀀싱 응답에 제한이 없다.

- 전압 모니터링 정확도가 0.7%이기 때문에 신뢰성 손상 없이 유연한 관리 신호를 생성한다. 뿐만 아니라, Platform Manager 및 Power Manager 디바이스 모두 차동 전압 감지 기능을 지원하기 때문에, 회로 보드의 특정 영역 사이의 접지 전압 차이에 의해 정확도가 저하되지 않는다.

- 모든 전원 고장 상태가 FPGA에 전송되기 때문에 알고리즘이 모든 고장에 대해 100 μs 이내에 응답하며 관리 신호를 즉시 생성한다. 이러한 속도는 높은 모니터링 정확도와 결합해 플래시 변형 가능성을 최소화시킨다.

- 특정 파워서플라이 고장 또는 다른 보드 내의 고장을 비휘발성 메모리에 100 μs 이내에 기록할 수 있다. 이를 통해 고장 획득 이미지가 일차적인 고장을 포함하도록 보장할 수 있다.

- HDL 코드를 사용하거나 LogiBuilder라고 하는 간단한 알고리즘 개발 툴을 이용해 전력관리 알고리즘을 구현할 수 있다. 프로그램을 완벽하게 시뮬레이션하고 알고리즘 동작을 정밀하게 조정할 수 있다 : 이를 통해 에러로 인한 보드 리스핀(re-spin) 가능성을 최소화할 수 있다.

- 보드 동작을 중단하지 않고 전력관리 알고리즘을 시스템 내에서 갱신할 수 있다. 디바이스는 또한 “골든 이미지(golden image)”를 저장하기 때문에, 인-시스템 갱신이 중단되거나 보드 전력이 순환하는 경우에 이 골든 이미지를 사용해 보드를 백업할 수 있다.

- Platform Manager와 Power Manager 사이의 통신은 간단하며 래티스가 레퍼런스 설계를 제공하고 있다. 사용자는 이 레퍼런스 설계를 실제 보드 전력관리 알고리즘에 간단하게 추가할 수 있다. 제공된 레퍼런스 설계는 메인 전력관리 알고리즘의 인터리빙 없이 모든 디바이스 간의 통신을 자동으로 관리한다.

요약

CPLD는 12개 이상의 레일을 사용하는 회로 보드에서 시퀀싱, 리셋 생성 등과 같은 전력관리 기능을 구현해야만 한다. 이들 설계들은 레일들을 모니터링하기 위해서 보드에 실장된 DC-DC 컨버터에 의해 생성된 파워 굿 신호에 의해 결정된다. 하지만 이들 파워 굿 신호의 열악한 모니터링 정확도 규격으로 인해 회로 보도의 기능 신뢰성이 크게 떨어진다. 이들 파워 굿 신호를 DC-DC 컨버터의 실제 출력 전압을 모니터링하는 정밀 비교기의 출력으로 대체하여 보드의 신뢰성을 증대시킬 수 있다.

이 글에서는 12개 이상의 레일을 사용하는 복잡한 회로 보드에서 모든 전력관리 요구사항들을 충족시킬 수 있는 확장 가능한 인-시스템 갱신 가능 스타 토폴로지 전력관리 아키텍처에 대해 설명했다. 온-칩 FPGA의 전력관리 알고리즘을 손상시키지 않으면서 DC-DC 컨버터 출력 전압을 (온-칩 정밀도 비교기를 사용하여) 정확하게 모니터링하는데 Lattice Platform Manager와 Power Manager 디바이스들을 사용함으로써 보드 기능 신뢰성을 강화할 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>