이 글은 시프트 단계 동안 조합 로직 토글을 게이트하며 설계의 피크 및 평균 동적 전력을 절감하는 플롭 설계를 제시하고 있다. 여기에 제시한 회로는 LOS(Launch On Shift)에서 SE(Scan Enable)을 활용해, 타이밍 문제로 인해 LOS 패턴을 수행할 수 없는 기존 회로의 단점을 해결한다.

글|아몰 아가왈 (Amol Agarwal), 가우라브 고얄 (Gaurav Goyal)

실파 굽타 (Shilpa Gupta) ,샌딥 자인 (Sandeep Jain)

프리스케일반도체

모든 SoC는 제조 상 결함을 찾아내기 위해 설계에 스캔 체인을 사용한다. 테스트용으로 설계된 스캔 체인은 칩의 순차적 소자(sequential elements)를 연속적인 순서로 연결한다. SoC에 점점 더 많은 기능이 통합됨에 따라, SoC 내의 총 플롭(순차적 소자)과 조합 로직 수도 증가하고 있다. 스캔 시프트 단계 동안에는 모든 플롭과 함께 조합 로직이 완전한 SI(shift-in) 및 SO(shift-out) 단계 동안 토글 되고, 피크 전력이 허용 한계를 초과하면 시프트 데이터가 손상될 수 있으며 의사 실패(pseudo fail)로 인해 칩 수율이 영향을 받게 되므로 피크 전력이 중요한 문제다. 이 글은 시프트 단계 동안 조합 로직 토글을 게이트하며 설계의 피크 및 평균 동적 전력을 절감하는 플롭 설계를 제시한다.

문제 설명

테스트용으로 설계에 사용되는 스캔 체인은 설계의 모든 순차적 소자를 복수의 체인으로 연결한다. 일반적인 플립 플롭에는 함수 출력(Q)과 스캔 출력(S0)이 있으며 서로 내부적으로 단락되어 있다. 플롭 설계자는 시프트 내의 홀드 타이밍을 손쉽게 마감할 수 있도록 전용 스캔 출력을 제공하며, SoC의 시프트 모드에서 플롭의 스캔 출력이 스캔 체인 내 다음 플롭의 스캔 입력에 직접 연결되고, 조합 로직이 존재하지 않으므로 이는 홀드 타이밍 크리티컬이 된다. 따라서 설계자는 이 문제를 사전에 방지하기 위해 단순히 함수 출력(Q)의 지연된 버전인 전용 스캔 출력을 제공한다.

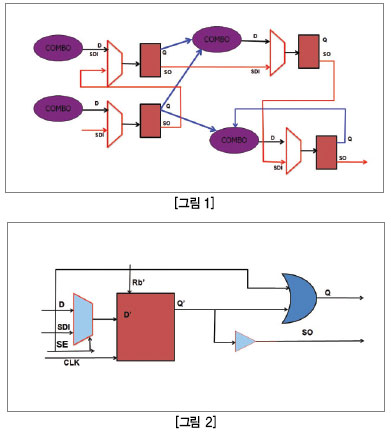

그 결과 SI 및 SO 단계 동안 스캔 입력 SI에 따라 함수 출력 Q와 함께 스캔 출력 SO가 계속 토글한다. 함수 출력 Q가 토글하므로 전체 함수 조합 로직 또한 전체 SI 및 SO 단계 동안 지속적으로 토글한다. 위 개념이 그림 1에 설명돼 있다.

문제 해결의 동기

시프트 동안 전력을 제한하는 것은 매우 중요하다. 설계, 인스턴스 수, 테스트 시간에 영향을 주지 않으면서 전력을 제한하는 것이 과제이다. 현재 시프트 주파수를 낮추거나 복수의 시프트 도메인을 생성하고 연속적으로 실행하거나, 시프트 패터 생성 도중 토글을 제한하는 등과 같은 몇 가지 수단으로 이를 달성할 수 있다. 하지만 위 솔루션은 모두 테스트 시간에 영향을 미치며, 그에 따른 테스트 비용도 추가된다.

따라서 조합 로직의 불필요한 토글을 중단시킴으로써 시프트 도중 피크 소비 전력을 현저히 낮출 수 있다.

이를 달성하는 방법 중 하나는 시프트 도중 함수 출력을 게이트하고 캡처 사이클에서 다시 언게이트하는 것이다. 이전에 이에 대한 연구가 일부 수행되었으며 SE(scan enable)로 함수 출력을 게이트하는 이전의 기술(US 7,650,548 B2)도 존재한다. 아이디어는 간단한 것으로, SE가 시프트 도중 1이 되고 캡처 사이클에서 언게이트됨으로써 일부 오래되거나 일정한 값이 아니라 스캔 입력의 최근 값에서 캡처가 일어남에 따라 함수 출력이 시프트 도중 일정하게 유지된다.

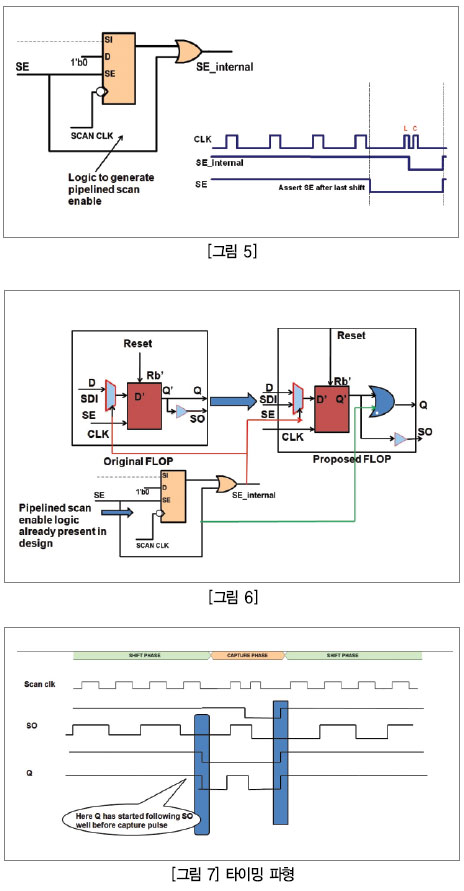

이 회로는 LOC 패턴에서는 잘 작동하지만 타이밍에 대한 커다란 제약으로 인해 LOS 패턴에서는 잘 작동하지 않는다(그림 2).

LOS 및 LOC

LOS(Launch on shift) 및 LOC(launch on capture)는 at-speed 테스트의 두 가지 유형이다.

LOC에서는 시프트 단계가 종료된 후 SE가 하락하며 2개의 캡처 펄스가 생긴다. SE가 하락한 후에 캡처 펄스를 확장할 수 있으므로 LOC에서 SE 타이밍은 문제가 되지 않는다(그림 3).

LOS의 경우, SE가 시작 및 캡처 펄스 사이에서 하락한다(그림 4). 여기서는 시프트 단계 도중 시작이 일어난다. LOS에서는 SE가 외부 테스터의 시간 T(함수 캡처 기간) 이내에 모든 플롯에 도달해야 하므로 SE 타이밍이 중요하다. 더구나 일부 내부 클록이 캡처 클록으로 사용되는 경우, 테스터 차원에서 내부 클록의 레퍼런스가 없으므로, 이 문제가 더욱 심각해진다. SE 타이밍 문제를 해결하기 위해 파이프라인 방식의 SE 구현(그림 5)을 선택했다.

LOS에서 외부 SE는 마지막 시프트가 발생할 캡처 클록을 고려하여 동기화된다. 그림 5의 타이밍 파형에서는 SE_internal이 SE를 포함한 각 순차적 소자에 전달되는 신호이다. 시프트 단계가 종료된 후 외부 SE는 하락하지만 내부 SE는 계속 1로 유지되므로 모든 플롭이 시프트 단계로 유지된다. 첫 번째 캡처 펄스가 도착하면 내부 SE가 0이 되며, 이제 한 번의 캡처 사이클 내에서 SE가 내부 파이프라인 SE 발생 로직의 모든 플롭에 도달하도록 보장하기만 하면 된다. 이제 파이프라인 SE를 통해 SE 타이밍의 단점이 해소되었으며 필요한 패턴 수가 적다는 점과 조합 ATPG 및 높은 적용 범위를 고려할 때 LOC에 비해 LOS가 선호된다.

하지만, 이전 기술 로직의 문제는 LOC에서 잘 작동하지만 LOS에서는 아니라는 점이다. 이는 함수 출력 이후의 LOC가 언게이트 상태이며, 시작 및 캡처 펄스를 확장할 수 있으므로 함수 출력 Q에서 스캔 출력 Q의 최근 값을 얻는 데 충분한 시간이 있지만 LOS의 경우 마지막 시프트가 일어난 후에만 SE가 하락될 수 있으므로 함수 출력이 언게이트되고 결국 유효한 캡처를 수행하기에는 시간이 부족하다. 따라서 현재 아키텍처에서는 LOS와 게이팅 조합 로직을 함께 사용할 수 없다.

해결 아이디어

SE 이외에 함수 출력을 게이트할 수 있는 다른 신호가 필요함이 분명해졌다. 우리의 아이디어는 파이프라인이 아닌 SE 신호를 함수 출력을 게이트하는 제어 신호로 사용하고, 파이프라인 SE를 일반 플롭의 경우처럼 함수 및 스캔 입력의 다중화(muxing)에 사용하는 것이다.

파이프라인이 아닌 SE는 캡처 단계가 시작되기 전, 즉 시프트 단계의 종료 시점 이전에 하락하게 된다. 따라서 LOS 패턴의 캡처 단계에서 마지막 시프트 사이클이 시작되기 전에 함수 출력이 스캔 출력과 동일하게 된다. 이에 따라, 이전 기술에서 동일한 SE 신호를 사용했을 때 발생했던 타이밍 문제가 이 사례에서 발생하지 않으며 플롭은 설계 내의 LOS 패턴을 지원하게 된다. 이 내용을 그림 7의 타이밍 파형에서 확인할 수 있다.

SoC 차원에서 원본 파이프라인 SE는 SE 타이밍이 각 플롭에서 클록 신호를 만족하는 방식으로 설계에 포함된 스캔 가능한 모든 플롭에 분배되어야 하는 전역 신호이다. 여기에는 설계 측면에서 일부 노력이 필요하다. 위에서 소개한 새로운 파이프라인이 아닌 전역 신호 또한 SoC 전반에서 각 순차적 소자에 분배되어야 하지만, 그림 7의 파형에서 볼 수 있듯이 매우 여유 있는 신호이므로 이 신호에 대한 설계 오버헤드는 극히 적으며 그리 많은 설계 노력 없이도 손쉽게 수용할 수 있다.

그림 7의 파형으로 볼 때 이제 함수 출력의 게이트 및 언게이트 작업이 SE 타이밍에 따라 좌우되지 않으며 파이프라인이 아닌 SE 신호를 사용해 독립적으로 제어할 수 있으므로 제시된 회로가 LOS 및 LOC 패턴 유형을 모두 지원함이 분명해졌다.

결론

시프트 스캔 모드에서 피크 소비 전력은 중요한 문제이다. 시프트 전력의 주요 구성요소 중 하나는 조합 로직의 불필요한 토글이다. 그간 시프트 모드에서 함수 출력을 게이트함으로써 이 문제를 해결하려는 시도가 있었다. 이전의 기존 회로는 타이밍 문제로 인해 LOS 패턴을 수행할 수 없다는 단점이 있다. 여기에 제시된 회로는 파이프라인이 아닌 SE를 활용해 이 문제를 해결하며, 그렇지 않으면, LOS에서 시프트 모드 동안 정적 상태였다. 이제 at-speed 캡처의 LOS 및 LOC 모드 모두에 제시된 플롭 설계를 활용할 수 있으며, 동시에 조합 로직의 불필요한 토글을 없앰으로써 시프트 모드 소비 전력도 절감할 수 있다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>