낮은 EMI 전원장치를 어떻게 조밀한 보드에 탑재하나

2019-11-05 글 / 박티 와그마레(Bhakti Waghmare), 디아무드 캐리(Diarmuid Carey), 아나로그디바이스(Analog Devices, Inc.)

전원장치는 EMI를 발생시키며 EMI는 반드시 해결해야 하지만, 어디에서 이러한 잡음이 발생하고, 이를 완화시키는 일반적인 전략은 무엇인가? 이 글에서는 EMI 저감 전략을 다루면서, EMI를 줄이고 효율을 유지하면서 제한된 솔루션 공간에 전원장치를 탑재하는 솔루션을 제시할 것이다.

제한된 협소한 보드 공간, 타이트한 설계 사이클, CISPR 32 및 CISPR 25와 같은 엄격한 전자기 간섭(EMI) 규격은 높은 효율과 우수한 열 성능 특성을 갖춘 전원장치의 제작을 어렵게 만드는 제한들이다. 이러한 문제는 종종 전원장치 설계가 설계 과정의 뒤로 밀리는 설계 사이클로 인해 더 복잡해진다.

.jpg)

설계 과정 끝으로 갈수록 복잡한 전원장치를 더 좁은 공간에 밀어 넣어야 때문에 설계 작업이 더 까다로워진다. 마감 시간 안에 설계를 마치기 위해 성능은 타협되고, 서둘러 테스트와 검증에 들어간다. 단순성과 성능, 솔루션 크기는 전통적으로 상충 관계에 있다. 하나 또는 두 가지 원하는 특징을 우선적으로 선택하면 세 번째 특징은 포기해야 한다. 특히 설계 마감일이 다가오면 이러한 현상이 두드러진다. 희생은 정상적으로 받아들여지지만, 그렇게 되어서는 안 된다.

이 글은 복잡한 전자 시스템에서 전원장치에 의해 제기되는 중요한 문제를 살펴보는 것으로부터 시작한다. 흔히 간단히 잡음으로 불리는 EMI 문제이다. 전원장치는 EMI를 발생시키며 EMI는 반드시 해결해야 하지만, 어디에서 이러한 잡음이 발생하고, 이를 완화시키는 일반적인 전략은 무엇인가? 이 글에서는 EMI 저감 전략을 다루면서, EMI를 줄이고 효율을 유지하면서 제한된 솔루션 공간에 전원장치를 탑재하는 솔루션을 제시할 것이다.

EMI란 무엇인가?

전자기 간섭은 시스템의 성능을 방해하는 전자기 신호이다. 이러한 교란은 전자기 유도, 정전기 결합 또는 전도를 통해 회로에 영향을 미친다. EMI는 자동차, 의료, 시험 및 계측 장비 제조업체의 중요한 설계 과제이다. 위에서 언급한 많은 제한은 물론 증가하는 전력 밀도, 높은 스위칭 주파수, 더 높은 전류를 포함한 전원장치에 대한 증가하는 성능 요구는 EMI의 영향을 확장하는 데 기여할 뿐이다. 따라서 이를 줄이는 솔루션이 필요하다. 많은 산업에서 EMI 표준을 준수해야 하며, 설계 사이클 초기에 이를 고려하지 않을 경우 제품 출시에 상당한 영향을 미칠 수 있다.

EMI 결합 유형

EMI는 간섭의 소스가 수신기(전자 시스템에서 일부 구성요소)와 결합할 때 전자 시스템에 발생하는 문제이다. EMI는 결합 매질에 따라 전도 또는 방사 EMI로 분류할 수 있다.

전도 EMI(저주파수, 450kHz ~ 30MHz)

전도 EMI는 기생 임피던스와 전원 및 접지 연결을 통한 전도를 통해 부품과 결합한다. 잡음은 전도에 의해 다른 디바이스나 회로에 전달된다. 더 나아가 전도 EMI는 공통 모드 또는 차동 모드 잡음으로 분류할 수 있다.

공통 모드 잡음은 기생 커패시턴스와 높은 dV/dt(C × dV/dt)를 통해 전도된다. 이 잡음은 기생 커패시턴스를 통해 모든 신호(양 또는 음)에서 GND로 흐르는 경로를 따른다(그림 1 참조).

.jpg)

차동 모드 잡음은 기생 인덕턴스(자기 결합)와 높은 di/dt(L × di/dt)를 통해 전도된다.

방사 EMI(고주파수, 30MHz ~ 1GHz)

방사 EMI는 자기 에너지를 통해 무선으로 시험 대상 디바이스에 전달되는 잡음이다. 스위칭 전원장치에서 잡음은 높은 di/dt가 기생 인덕턴스와 결합한 결과이다. 이러한 방사 잡음은 가까운 디바이스에 영향을 미칠 수 있다.

EMI 제어 기법

전원장치에서 EMI 관련 문제를 해결하는 일반적인 방법은 무엇인가? 첫째, EMI 문제를 명확히 한다. 이는 분명해 보이지만, 이에 대한 지식을 얻기 위해서는 EMI 챔버(모든 곳에서 사용 가능하지는 않음)에 접근하여 얼마나 많은 전자기 에너지가 전원장치에 의해 생성되는지 정량화하고, 수치가 시스템에서 요구하는 표준 안에 충분히 들어가는지 확인해야 하므로 많은 시간이 걸릴 수 있다.

테스트 후 전원장치에서 EMI 문제가 존재한다고 가정하면, 다음을 포함하여 다수의 전통적인 교정 전략을 통해 EMI 저감 과정이 수행된다.

- 최소 보드 공간에서 높은 효율

- 우수한 열 성능

- 레이아웃 최적화: 신중한 전원장치 레이아웃은 전원장치를 위한 올바른 부품 선택만큼 중요하다. 성공적인 레이아웃은 전원장치 설계자의 경험 수준에 크게 의존한다. 레이아웃 최적화는 본질적으로 반복적이며, 숙련된 전원장치 설계자는 반복 횟수를 최소화하는 데 도움을 줄 수 있다. 따라서 시간 지연과 추가적인 설계 비용을 피할 수 있다. 문제는 그와 같은 경험은 종종 사내에서 얻을 수 없다는 점이다.

- 스너버: 일부 설계자는 미리 계획을 세우고 간단한 스너버 회로(스위치 노드에서 GND까지 단순한 RC 필터)를 위한 풋프린트를 제공한다. 이 방법은 EMI 원인이 되는 스위치 노드 링잉을 억제할 수 있지만, 손실을 증가시키고 효율에 부정적인 영향을 미친다.

- 에지 속도 감소: 게이트 턴온의 슬루율을 감소시키면 스위치 노드 링잉을 줄일 수 있다. 그러나 유감스럽게도 이 방법 역시 스너버와 마찬가지로 전체 시스템 효율에 부정적인 영향을 미친다.

- 확산 스펙트럼 주파수 변조(SSFM): 이 기능은 많은 ADI Power by Linear™ 스위칭 레귤레이터에서 옵션으로 제공되며, 엄격한 EMI 테스트 표준을 통과할 수 있게 도와준다. SSFM에서 스위칭 주파수 구동에 사용되는 클록은 알려진 범위(예를 들어 프로그래밍된 fSW에서 ±10%)에서 변조된다. 이는 피크 잡음 에너지를 더 넓은 주파수 범위에 걸쳐 분산시키는 데 도움이 된다.

- 필터 및 차폐: 필터와 차폐는 항상 비용과 공간을 증가시키며, 생산을 복잡하게 만든다.

- 위의 모든 대응책은 잡음을 감소시킬 수 있지만, 모두 단점을 갖는다. 전원장치 설계에서 잡음을 최소화하는 것이 가장 깨끗한 경로를 제공하지만, 이는 달성하기가 어렵다. ADI 사일런트 스위처(Silent Switcher®) 및 사일런트 스위처 2 레귤레이터는 레귤레이터에서 낮은 잡음을 달성하므로 추가적인 필터링이나 차폐 또는 많은 레이아웃 반복이 필요하지 않다. 비용이 많이 드는 대응책을 피하면 제품 출시 기간을 단축하고 상당한 비용을 절감할 수 있다.

전류 루프 최소화

EMI를 줄이려면 전원장치 회로에서 핫루프(높은 di/dt 루프)를 결정하고, 그 영향을 감소시켜야 한다. 핫루프는 그림 2에서 볼 수 있다. 표준 벅 컨버터의 1 사이클에서 ac는 청색 루프를 따라 흐르고, 이때 M1은 닫히고 M2는 열린다. M1이 열리고 M2가 닫히는 오프(off) 사이클 동안 전류는 녹색 루프를 따라 흐른다. 완전히 직관적으로 알기는 어렵지만, 가장 높은 EMI를 생성하는 루프는 청색 루프도 녹색 루프도 아니다. 오직 보라색 루프만 완전히 스위칭 된 ac를 전도한다. 즉, 영에서 IPEAK로 스위칭 되었다가 다시 영이 된다. 이 루프는 가장 높은 ac와 EMI 에너지를 갖고 있기 때문에 핫루프 라고 한다.

스위처 핫루프의 높은 di/dt와 기생 인덕턴스는 전자기 잡음과 스위치 링잉을 발생시킨다. EMI를 줄이고 기능을 향상시키려면 가능한 한 많이 보라색 루프의 방사 영향을 감소시켜야 한다. 핫루프의 방사 EMI는 면적과 함께 증가한다. 따라서 핫루프의 PC 영역을 0으로 줄이고 임피던스가 0인 아이디얼 커패시터를 사용하면 -이것이 가능하다면- 문제를 해결할 수 있을 것이다.

.jpg)

저잡음 달성하는 사일런트 스위처 레귤레이터

자기 상쇄

핫루프 영역을 0으로 줄이는 것은 사실상 불가능하지만, 핫루프를 극성이 반대인 2개의 루프로 분리할 수 있다. 이렇게 하면 효과적으로 자기장을 국지적으로 묶어 둠으로써 IC로부터 어느 거리에서나 자기장이 서로 상호 간에 효과적으로 상쇄하게 된다. 이것이 사일런트 스위처 레귤레이터가 바탕을 둔 개념이다.

.jpg)

플립 칩으로 와이어본드 대체

EMI를 향상시키는 또 다른 방법은 핫루프의 와이어를 짧게 하는 것이다. 다이를 패키지 핀에 연결하는 전통적인 와이어본드 방법을 제거하는 것이다. 패키지에서 실리콘을 뒤집어서(Flip) 구리 필러를 추가한다. 이렇게 하면 내부 FET에서 패키지 핀과 입력 커패시터까지 거리가 짧아져 핫루프의 영역이 더욱 최소화된다.

.jpg)

사일런트 스위처 vs. 사일런트 스위처 2

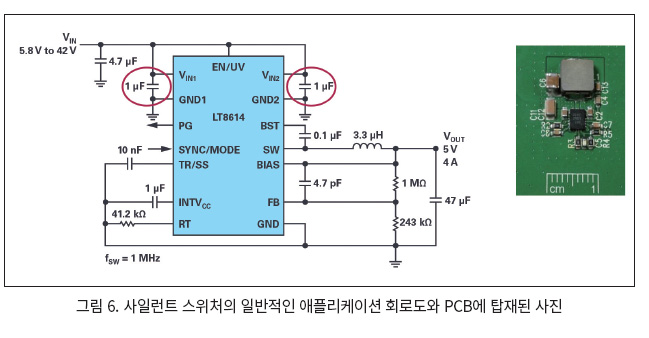

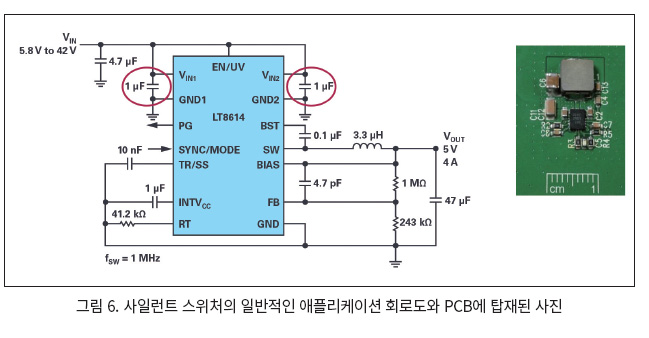

그림 6은 사일런트 스위처 레귤레이터를 사용하는 일반적인 애플리케이션을 보여준다. 2개의 입력 전압 핀에서 대칭적인 입력 커패시터로 식별할 수 있다. 이러한 구조에서는 레이아웃이 중요한데, 사일런트 스위처 기술은 입력 커패시터를 가능한 대칭적으로 배치해야 상호적인 자기장 상쇄 이점을 제공할 수 있기 때문이다. 그렇지 않을 경우 사일런트 스위처 기술의 이점은 사라진다. 물론 문제는 어떻게 설계와 생산 과정 전체에서 적절한 레이아웃을 보장하느냐이다. 답은 사일런트 스위처 2 레귤레이터이다.

사일런트 스위처 2

사일런트 스위처 2 레귤레이터는 한 단계 더 나아간 EMI 저감을 제공한다. 외부 커패시터(VIN 커패시터, INTVCC, 부스트 커패시터)를 LQFN 패키지에 통합함으로써 꼭 필요한 커패시터를 핀에 가능한 가깝게 배치할 수 있기 때문에 PCB 레이아웃에 대한 EMI 성능 민감도가 제거된다. 모든 핫루프와 접지 플레인이 내부에 있으므로 EMI를 최소화하고 전체 솔루션 풋프린트를 줄일 수 있다.

사일런트 스위처 2 기술은 또한 열 성능을 향상시킨다. LQFN 플립 칩 패키지의 대형, 다중 접지 노출형 패드는 패키지로부터 PCB로 용이하게 열을 발산시킨다. 또한 저항이 높은 본드 와이어가 제거돼 더 높은 변환 효율을 달성한다. EMI 성능 테스트에서 LT8640S는 여유 있게 CISPR 25 클래스 5 피크 제한을 통과한다

.jpg)

.jpg)

μModule 사일런트 스위처 레귤레이터

사일런트 스위처 포트폴리오를 개발하고 이를 이미 방대한 μModule® 포트폴리오와 결합하면서 얻은 지식과 경험을 통해 우리는 설계하기 쉽고 전원장치의 가장 중요한 지표들인 열, 신뢰성, 정확도, 효율, 뛰어난 EMI 성능을 만족하는 전력 제품을 제공할 수 있었다.

.jpg)

그림 9는 이 전원장치의 동작에 필요한 여러 가지 다른 수동 부품과 함께 자기장 상쇄를 가능하게 하는 2개의 입력 커패시터를 통합한 LTM8053을 보여준다. 이 모든 것이 6.25mm× 9mm×3.32mm BGA 패키지로 제공되므로 고객은 보드 설계의 다른 부분에 집중할 수 있다.

LDO 레귤레이터 필요를 없애주는 전원장치 케이스 스터디

일반적인 고속 ADC는 다수의 전압 레일을 필요로 하며, ADC의 최고 데이터 시트 성능을 달성하려면 이러한 레일 중 일부는 매우 잡음이 낮아야 한다. 높은 효율, 작은 보드 공간, 낮은 잡음의 균형을 달성하는 데 일반적으로 받아들여지는 솔루션은 스위칭 전원장치와 LDO 포스트 레귤레이터를 결합하는 것이다(그림 10).

.jpg)

스위칭 레귤레이터는 높은 효율로 비교적 높은 스텝다운 비를 달성할 수 있지만 상대적으로 잡음이 많다. 저잡음 LDO 포스트 레귤레이터는 상대적으로 비효율적이지만, 스위칭 레귤레이터에 의해 생성되는 전도된 잡음의 상당 부분을 제거할 수 있다. LDO 포스트 레귤레이터의 스텝다운 비를 최소화하면 효율에 도움이 된다. 이러한 결합은 깨끗한 전원을 생성하여 ADC가 최고 성능 수준에서 동작할 수 있게 한다. 문제는 다수의 레귤레이터로 레이아웃이 복잡해지고, LDO 포스트 레귤레이터는 높은 부하에서 열 문제를 가질 수 있다는 것이다.

그림 10에 보이는 설계에서는 명백히 일부 절충이 수반된다. 이 경우 낮은 잡음이 우선적이므로 효율과 보드 공간을 희생해야 한다. 하지만 이러한 절충은 피할 수 있다. 최신 세대 사일런트 스위처 μModule 디바이스는 저잡음 성능 스위칭 레귤레이터 설계와 μModule 패키징을 결합함으로써 쉬운 설계, 높은 효율, 초소형 크기, 낮은 잡음이라는 달성 불가능한 조합을 달성한다.

이들 레귤레이터는 보드 공간을 최소화할 뿐 아니라 확장도 가능하므로 1개의 μModule 레귤레이터에서 여러 개의 전압 레일을 구동할 수 있기 때문에 공간과 시간을 더욱 절약할 수 있다. 그림 11은 LTM8065 사일런트 스위처 μModule 레귤레이터를 사용하여 ADC에 전력을 공급하는 대안적인 전력 트리를 보여준다.

.jpg)

이들 설계는 서로에 대해 테스트되었다. 그림 10과 그림 11의 전원장치 설계를 사용하는 ADC 성능을 테스트하고 비교하여 ADI가 최근 발표한 글에 수록하였다.1 다음과 같은 세 가지 구성이 테스트되었다.

- 스위칭 레귤레이터와 LDO 레귤레이터를 사용하여 ADC에 전력을 공급하는 표준 구성

- 추가 필터 없이 LTM8065를 사용하여 ADC에 직접 전력을 공급하는 구성

- 출력을 더 깨끗하게 하기 위해 출력 LC 필터를 추가하고 LTM8065를 사용하는 구성

측정된 SFDR 및 SNRFS 결과는 LTM8065를 사용하여 77ADC에 직접 전력을 공급했을 때 ADC 성능 저하가 없다는 것을 보여주었다.

이러한 구현의 핵심적인 이점은 부품 수를 크게 줄이고 더 높은 효율, 더 쉬운 생산, 더 작은 보드 공간을 달성할 수 있다는 점이다.

요약

보다 엄격한 규격을 갖는 더 높은 시스템 수준의 설계로 전환됨에 따라, 특히 전원장치 설계 전문지식이 거의 없는 경우 가능하면 모듈식 전원장치 설계를 활용하는 것이 중요하다. 시스템 설계가 최신 EMI 규격을 통과해야 하는 많은 세분 시장에서 사일런트 스위처 기술은 소형 폼팩터에 통합돼 사용되며, μModule 레귤레이터의 사용 용이성은 제품 출시 기간을 획기적으로 향상시키고 보드 공간을 절감한다.

사일런트 스위처 μModule 레귤레이터의 이점

- PCB 레이아웃 설계 시간 절약(잡음 문제를 개선하기 위한 보드 재실행 불필요)

- 추가적인 EMI 필터 불필요(부품 비용 및 보드 공간 절약)

- 전원장치 잡음을 해결하기 위한 사내 전원장치 전문가 필요 감소

- 넓은 동작 주파수 범위에서 높은 효율

- 잡음에 민감한 디바이스에 전력을 공급할 경우 LDO 포스트 레귤레이터 불필요

- 설계 사이클 단축

- 최소 보드 공간에서 높은 효율

- 우수한 열 성능

참고문헌

1. Aldrick Limjoco, Patrick Pasaquian, and Jefferson Eco. “Silent Switcher μModule Regulators Quietly Power GSPS Sampling ADCs in Half the Space.” Analog Devices, Inc., October 2018.

글쓴이

박티 와그마레(Bhakti Waghmare)는 현재 미국 캘리포니아주 산타클라라에 있는 μModule 레귤레이터 Power by Linear 제품 그룹의 제품 마케팅 엔지니어이다. μModule 레귤레이터 전력 제품을 위한 마케팅을 지원하고 있다. 2018년에 아나로그디바이스에 입사했다. 미시간주 디트로이트의 웨인 주립대학에서 기계공학 학사 및 산업공학 석사학위를 받았다. bhakti.waghmare@analog.com으로 문의.

디아무드 캐리(Diarmuid Carey)는 아일랜드 리머릭에 있는 유럽 중앙집중 애플리케이션 센터의 애플리케이션 엔지니어이다. 2008년부터 애플리케이션 엔지니어로 근무했으며 2017년에 아나로그디바이스에 합류하여 광범위한 유럽 시장 고객을 위해 Power by Linear 포트폴리오를 위한 설계 지원을 제공하고 있다. 리머릭 대학에서 컴퓨터공학 학사학위를 받았다. diarmuid.carey@analog.com으로 문의.

제한된 협소한 보드 공간, 타이트한 설계 사이클, CISPR 32 및 CISPR 25와 같은 엄격한 전자기 간섭(EMI) 규격은 높은 효율과 우수한 열 성능 특성을 갖춘 전원장치의 제작을 어렵게 만드는 제한들이다. 이러한 문제는 종종 전원장치 설계가 설계 과정의 뒤로 밀리는 설계 사이클로 인해 더 복잡해진다.

.jpg)

설계 과정 끝으로 갈수록 복잡한 전원장치를 더 좁은 공간에 밀어 넣어야 때문에 설계 작업이 더 까다로워진다. 마감 시간 안에 설계를 마치기 위해 성능은 타협되고, 서둘러 테스트와 검증에 들어간다. 단순성과 성능, 솔루션 크기는 전통적으로 상충 관계에 있다. 하나 또는 두 가지 원하는 특징을 우선적으로 선택하면 세 번째 특징은 포기해야 한다. 특히 설계 마감일이 다가오면 이러한 현상이 두드러진다. 희생은 정상적으로 받아들여지지만, 그렇게 되어서는 안 된다.

이 글은 복잡한 전자 시스템에서 전원장치에 의해 제기되는 중요한 문제를 살펴보는 것으로부터 시작한다. 흔히 간단히 잡음으로 불리는 EMI 문제이다. 전원장치는 EMI를 발생시키며 EMI는 반드시 해결해야 하지만, 어디에서 이러한 잡음이 발생하고, 이를 완화시키는 일반적인 전략은 무엇인가? 이 글에서는 EMI 저감 전략을 다루면서, EMI를 줄이고 효율을 유지하면서 제한된 솔루션 공간에 전원장치를 탑재하는 솔루션을 제시할 것이다.

EMI란 무엇인가?

전자기 간섭은 시스템의 성능을 방해하는 전자기 신호이다. 이러한 교란은 전자기 유도, 정전기 결합 또는 전도를 통해 회로에 영향을 미친다. EMI는 자동차, 의료, 시험 및 계측 장비 제조업체의 중요한 설계 과제이다. 위에서 언급한 많은 제한은 물론 증가하는 전력 밀도, 높은 스위칭 주파수, 더 높은 전류를 포함한 전원장치에 대한 증가하는 성능 요구는 EMI의 영향을 확장하는 데 기여할 뿐이다. 따라서 이를 줄이는 솔루션이 필요하다. 많은 산업에서 EMI 표준을 준수해야 하며, 설계 사이클 초기에 이를 고려하지 않을 경우 제품 출시에 상당한 영향을 미칠 수 있다.

EMI 결합 유형

EMI는 간섭의 소스가 수신기(전자 시스템에서 일부 구성요소)와 결합할 때 전자 시스템에 발생하는 문제이다. EMI는 결합 매질에 따라 전도 또는 방사 EMI로 분류할 수 있다.

전도 EMI(저주파수, 450kHz ~ 30MHz)

전도 EMI는 기생 임피던스와 전원 및 접지 연결을 통한 전도를 통해 부품과 결합한다. 잡음은 전도에 의해 다른 디바이스나 회로에 전달된다. 더 나아가 전도 EMI는 공통 모드 또는 차동 모드 잡음으로 분류할 수 있다.

공통 모드 잡음은 기생 커패시턴스와 높은 dV/dt(C × dV/dt)를 통해 전도된다. 이 잡음은 기생 커패시턴스를 통해 모든 신호(양 또는 음)에서 GND로 흐르는 경로를 따른다(그림 1 참조).

.jpg)

차동 모드 잡음은 기생 인덕턴스(자기 결합)와 높은 di/dt(L × di/dt)를 통해 전도된다.

방사 EMI(고주파수, 30MHz ~ 1GHz)

방사 EMI는 자기 에너지를 통해 무선으로 시험 대상 디바이스에 전달되는 잡음이다. 스위칭 전원장치에서 잡음은 높은 di/dt가 기생 인덕턴스와 결합한 결과이다. 이러한 방사 잡음은 가까운 디바이스에 영향을 미칠 수 있다.

EMI 제어 기법

전원장치에서 EMI 관련 문제를 해결하는 일반적인 방법은 무엇인가? 첫째, EMI 문제를 명확히 한다. 이는 분명해 보이지만, 이에 대한 지식을 얻기 위해서는 EMI 챔버(모든 곳에서 사용 가능하지는 않음)에 접근하여 얼마나 많은 전자기 에너지가 전원장치에 의해 생성되는지 정량화하고, 수치가 시스템에서 요구하는 표준 안에 충분히 들어가는지 확인해야 하므로 많은 시간이 걸릴 수 있다.

테스트 후 전원장치에서 EMI 문제가 존재한다고 가정하면, 다음을 포함하여 다수의 전통적인 교정 전략을 통해 EMI 저감 과정이 수행된다.

- 최소 보드 공간에서 높은 효율

- 우수한 열 성능

- 레이아웃 최적화: 신중한 전원장치 레이아웃은 전원장치를 위한 올바른 부품 선택만큼 중요하다. 성공적인 레이아웃은 전원장치 설계자의 경험 수준에 크게 의존한다. 레이아웃 최적화는 본질적으로 반복적이며, 숙련된 전원장치 설계자는 반복 횟수를 최소화하는 데 도움을 줄 수 있다. 따라서 시간 지연과 추가적인 설계 비용을 피할 수 있다. 문제는 그와 같은 경험은 종종 사내에서 얻을 수 없다는 점이다.

- 스너버: 일부 설계자는 미리 계획을 세우고 간단한 스너버 회로(스위치 노드에서 GND까지 단순한 RC 필터)를 위한 풋프린트를 제공한다. 이 방법은 EMI 원인이 되는 스위치 노드 링잉을 억제할 수 있지만, 손실을 증가시키고 효율에 부정적인 영향을 미친다.

- 에지 속도 감소: 게이트 턴온의 슬루율을 감소시키면 스위치 노드 링잉을 줄일 수 있다. 그러나 유감스럽게도 이 방법 역시 스너버와 마찬가지로 전체 시스템 효율에 부정적인 영향을 미친다.

- 확산 스펙트럼 주파수 변조(SSFM): 이 기능은 많은 ADI Power by Linear™ 스위칭 레귤레이터에서 옵션으로 제공되며, 엄격한 EMI 테스트 표준을 통과할 수 있게 도와준다. SSFM에서 스위칭 주파수 구동에 사용되는 클록은 알려진 범위(예를 들어 프로그래밍된 fSW에서 ±10%)에서 변조된다. 이는 피크 잡음 에너지를 더 넓은 주파수 범위에 걸쳐 분산시키는 데 도움이 된다.

- 필터 및 차폐: 필터와 차폐는 항상 비용과 공간을 증가시키며, 생산을 복잡하게 만든다.

- 위의 모든 대응책은 잡음을 감소시킬 수 있지만, 모두 단점을 갖는다. 전원장치 설계에서 잡음을 최소화하는 것이 가장 깨끗한 경로를 제공하지만, 이는 달성하기가 어렵다. ADI 사일런트 스위처(Silent Switcher®) 및 사일런트 스위처 2 레귤레이터는 레귤레이터에서 낮은 잡음을 달성하므로 추가적인 필터링이나 차폐 또는 많은 레이아웃 반복이 필요하지 않다. 비용이 많이 드는 대응책을 피하면 제품 출시 기간을 단축하고 상당한 비용을 절감할 수 있다.

전류 루프 최소화

EMI를 줄이려면 전원장치 회로에서 핫루프(높은 di/dt 루프)를 결정하고, 그 영향을 감소시켜야 한다. 핫루프는 그림 2에서 볼 수 있다. 표준 벅 컨버터의 1 사이클에서 ac는 청색 루프를 따라 흐르고, 이때 M1은 닫히고 M2는 열린다. M1이 열리고 M2가 닫히는 오프(off) 사이클 동안 전류는 녹색 루프를 따라 흐른다. 완전히 직관적으로 알기는 어렵지만, 가장 높은 EMI를 생성하는 루프는 청색 루프도 녹색 루프도 아니다. 오직 보라색 루프만 완전히 스위칭 된 ac를 전도한다. 즉, 영에서 IPEAK로 스위칭 되었다가 다시 영이 된다. 이 루프는 가장 높은 ac와 EMI 에너지를 갖고 있기 때문에 핫루프 라고 한다.

스위처 핫루프의 높은 di/dt와 기생 인덕턴스는 전자기 잡음과 스위치 링잉을 발생시킨다. EMI를 줄이고 기능을 향상시키려면 가능한 한 많이 보라색 루프의 방사 영향을 감소시켜야 한다. 핫루프의 방사 EMI는 면적과 함께 증가한다. 따라서 핫루프의 PC 영역을 0으로 줄이고 임피던스가 0인 아이디얼 커패시터를 사용하면 -이것이 가능하다면- 문제를 해결할 수 있을 것이다.

.jpg)

저잡음 달성하는 사일런트 스위처 레귤레이터

자기 상쇄

핫루프 영역을 0으로 줄이는 것은 사실상 불가능하지만, 핫루프를 극성이 반대인 2개의 루프로 분리할 수 있다. 이렇게 하면 효과적으로 자기장을 국지적으로 묶어 둠으로써 IC로부터 어느 거리에서나 자기장이 서로 상호 간에 효과적으로 상쇄하게 된다. 이것이 사일런트 스위처 레귤레이터가 바탕을 둔 개념이다.

.jpg)

플립 칩으로 와이어본드 대체

EMI를 향상시키는 또 다른 방법은 핫루프의 와이어를 짧게 하는 것이다. 다이를 패키지 핀에 연결하는 전통적인 와이어본드 방법을 제거하는 것이다. 패키지에서 실리콘을 뒤집어서(Flip) 구리 필러를 추가한다. 이렇게 하면 내부 FET에서 패키지 핀과 입력 커패시터까지 거리가 짧아져 핫루프의 영역이 더욱 최소화된다.

.jpg)

사일런트 스위처 vs. 사일런트 스위처 2

그림 6은 사일런트 스위처 레귤레이터를 사용하는 일반적인 애플리케이션을 보여준다. 2개의 입력 전압 핀에서 대칭적인 입력 커패시터로 식별할 수 있다. 이러한 구조에서는 레이아웃이 중요한데, 사일런트 스위처 기술은 입력 커패시터를 가능한 대칭적으로 배치해야 상호적인 자기장 상쇄 이점을 제공할 수 있기 때문이다. 그렇지 않을 경우 사일런트 스위처 기술의 이점은 사라진다. 물론 문제는 어떻게 설계와 생산 과정 전체에서 적절한 레이아웃을 보장하느냐이다. 답은 사일런트 스위처 2 레귤레이터이다.

사일런트 스위처 2

사일런트 스위처 2 레귤레이터는 한 단계 더 나아간 EMI 저감을 제공한다. 외부 커패시터(VIN 커패시터, INTVCC, 부스트 커패시터)를 LQFN 패키지에 통합함으로써 꼭 필요한 커패시터를 핀에 가능한 가깝게 배치할 수 있기 때문에 PCB 레이아웃에 대한 EMI 성능 민감도가 제거된다. 모든 핫루프와 접지 플레인이 내부에 있으므로 EMI를 최소화하고 전체 솔루션 풋프린트를 줄일 수 있다.

사일런트 스위처 2 기술은 또한 열 성능을 향상시킨다. LQFN 플립 칩 패키지의 대형, 다중 접지 노출형 패드는 패키지로부터 PCB로 용이하게 열을 발산시킨다. 또한 저항이 높은 본드 와이어가 제거돼 더 높은 변환 효율을 달성한다. EMI 성능 테스트에서 LT8640S는 여유 있게 CISPR 25 클래스 5 피크 제한을 통과한다

.jpg)

.jpg)

μModule 사일런트 스위처 레귤레이터

사일런트 스위처 포트폴리오를 개발하고 이를 이미 방대한 μModule® 포트폴리오와 결합하면서 얻은 지식과 경험을 통해 우리는 설계하기 쉽고 전원장치의 가장 중요한 지표들인 열, 신뢰성, 정확도, 효율, 뛰어난 EMI 성능을 만족하는 전력 제품을 제공할 수 있었다.

.jpg)

그림 9는 이 전원장치의 동작에 필요한 여러 가지 다른 수동 부품과 함께 자기장 상쇄를 가능하게 하는 2개의 입력 커패시터를 통합한 LTM8053을 보여준다. 이 모든 것이 6.25mm× 9mm×3.32mm BGA 패키지로 제공되므로 고객은 보드 설계의 다른 부분에 집중할 수 있다.

LDO 레귤레이터 필요를 없애주는 전원장치 케이스 스터디

일반적인 고속 ADC는 다수의 전압 레일을 필요로 하며, ADC의 최고 데이터 시트 성능을 달성하려면 이러한 레일 중 일부는 매우 잡음이 낮아야 한다. 높은 효율, 작은 보드 공간, 낮은 잡음의 균형을 달성하는 데 일반적으로 받아들여지는 솔루션은 스위칭 전원장치와 LDO 포스트 레귤레이터를 결합하는 것이다(그림 10).

.jpg)

스위칭 레귤레이터는 높은 효율로 비교적 높은 스텝다운 비를 달성할 수 있지만 상대적으로 잡음이 많다. 저잡음 LDO 포스트 레귤레이터는 상대적으로 비효율적이지만, 스위칭 레귤레이터에 의해 생성되는 전도된 잡음의 상당 부분을 제거할 수 있다. LDO 포스트 레귤레이터의 스텝다운 비를 최소화하면 효율에 도움이 된다. 이러한 결합은 깨끗한 전원을 생성하여 ADC가 최고 성능 수준에서 동작할 수 있게 한다. 문제는 다수의 레귤레이터로 레이아웃이 복잡해지고, LDO 포스트 레귤레이터는 높은 부하에서 열 문제를 가질 수 있다는 것이다.

그림 10에 보이는 설계에서는 명백히 일부 절충이 수반된다. 이 경우 낮은 잡음이 우선적이므로 효율과 보드 공간을 희생해야 한다. 하지만 이러한 절충은 피할 수 있다. 최신 세대 사일런트 스위처 μModule 디바이스는 저잡음 성능 스위칭 레귤레이터 설계와 μModule 패키징을 결합함으로써 쉬운 설계, 높은 효율, 초소형 크기, 낮은 잡음이라는 달성 불가능한 조합을 달성한다.

이들 레귤레이터는 보드 공간을 최소화할 뿐 아니라 확장도 가능하므로 1개의 μModule 레귤레이터에서 여러 개의 전압 레일을 구동할 수 있기 때문에 공간과 시간을 더욱 절약할 수 있다. 그림 11은 LTM8065 사일런트 스위처 μModule 레귤레이터를 사용하여 ADC에 전력을 공급하는 대안적인 전력 트리를 보여준다.

.jpg)

이들 설계는 서로에 대해 테스트되었다. 그림 10과 그림 11의 전원장치 설계를 사용하는 ADC 성능을 테스트하고 비교하여 ADI가 최근 발표한 글에 수록하였다.1 다음과 같은 세 가지 구성이 테스트되었다.

- 스위칭 레귤레이터와 LDO 레귤레이터를 사용하여 ADC에 전력을 공급하는 표준 구성

- 추가 필터 없이 LTM8065를 사용하여 ADC에 직접 전력을 공급하는 구성

- 출력을 더 깨끗하게 하기 위해 출력 LC 필터를 추가하고 LTM8065를 사용하는 구성

측정된 SFDR 및 SNRFS 결과는 LTM8065를 사용하여 77ADC에 직접 전력을 공급했을 때 ADC 성능 저하가 없다는 것을 보여주었다.

이러한 구현의 핵심적인 이점은 부품 수를 크게 줄이고 더 높은 효율, 더 쉬운 생산, 더 작은 보드 공간을 달성할 수 있다는 점이다.

요약

보다 엄격한 규격을 갖는 더 높은 시스템 수준의 설계로 전환됨에 따라, 특히 전원장치 설계 전문지식이 거의 없는 경우 가능하면 모듈식 전원장치 설계를 활용하는 것이 중요하다. 시스템 설계가 최신 EMI 규격을 통과해야 하는 많은 세분 시장에서 사일런트 스위처 기술은 소형 폼팩터에 통합돼 사용되며, μModule 레귤레이터의 사용 용이성은 제품 출시 기간을 획기적으로 향상시키고 보드 공간을 절감한다.

사일런트 스위처 μModule 레귤레이터의 이점

- PCB 레이아웃 설계 시간 절약(잡음 문제를 개선하기 위한 보드 재실행 불필요)

- 추가적인 EMI 필터 불필요(부품 비용 및 보드 공간 절약)

- 전원장치 잡음을 해결하기 위한 사내 전원장치 전문가 필요 감소

- 넓은 동작 주파수 범위에서 높은 효율

- 잡음에 민감한 디바이스에 전력을 공급할 경우 LDO 포스트 레귤레이터 불필요

- 설계 사이클 단축

- 최소 보드 공간에서 높은 효율

- 우수한 열 성능

참고문헌

1. Aldrick Limjoco, Patrick Pasaquian, and Jefferson Eco. “Silent Switcher μModule Regulators Quietly Power GSPS Sampling ADCs in Half the Space.” Analog Devices, Inc., October 2018.

글쓴이

박티 와그마레(Bhakti Waghmare)는 현재 미국 캘리포니아주 산타클라라에 있는 μModule 레귤레이터 Power by Linear 제품 그룹의 제품 마케팅 엔지니어이다. μModule 레귤레이터 전력 제품을 위한 마케팅을 지원하고 있다. 2018년에 아나로그디바이스에 입사했다. 미시간주 디트로이트의 웨인 주립대학에서 기계공학 학사 및 산업공학 석사학위를 받았다. bhakti.waghmare@analog.com으로 문의.

디아무드 캐리(Diarmuid Carey)는 아일랜드 리머릭에 있는 유럽 중앙집중 애플리케이션 센터의 애플리케이션 엔지니어이다. 2008년부터 애플리케이션 엔지니어로 근무했으며 2017년에 아나로그디바이스에 합류하여 광범위한 유럽 시장 고객을 위해 Power by Linear 포트폴리오를 위한 설계 지원을 제공하고 있다. 리머릭 대학에서 컴퓨터공학 학사학위를 받았다. diarmuid.carey@analog.com으로 문의.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

본 기사의 전문은 PDF문서로 제공합니다.

(로그인필요)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

100자평 쓰기