[기술기고] 산업용 이더넷의 동기화 과제 해결하기

2019-12-04 글 / 마두 발라수브라마니안(Madhu Balasubramanian), 시스템 및 애플리케이션 엔지니어, 텍사스 인스트루먼트(TI)

이더넷은 전통적으로 통신 시스템에서 유선으로 로컬 영역 네트워크(LAN)를 연결했다. 최근에는 산업용과 자동화용 애플리케이션의 서브시스템을 연결하는 실질적인 표준이 됐다. 시간 동기화는 전체 시스템의 단일 마스터 클럭으로 추적 가능한 서브시스템에서 클럭을 생성하는 기능이다.

.jpg)

자동화공장 셋업의 효율성 최적화 및 개선, 데이터 수집 시스템의 전반적인 성능 향상 또는 다운로드 시간 감소를 위한 효율적인 장애 감지 및 수정을 원하는가? 앞에 제시된 조건의 전부 또는 일부를 원한다면, 네트워크 동기화(network synchronizer)로 클럭 동기화(clock synchronization)을 활성화하는 방법을 고려할 수 있다.

클럭 동기화란?

이더넷은 전통적으로 통신 시스템에서 유선으로 로컬 영역 네트워크(LAN)를 연결했다. 최근에는 산업용과 자동화용 애플리케이션의 서브시스템을 연결하는 실질적인 표준이 됐다. 레퍼런스 클럭(Reference clock)은 이더넷 링크 작동을 위해 필요하며, 대개 프리런닝 클럭 소스에서 생성된다. 시간 동기화는 전체 시스템의 단일 마스터 클럭으로 추적 가능한 서브시스템에서 클럭을 생성하는 기능이다.

클럭 동기화는 많은 엔드 애플리케이션에 유용하며, 예는 다음과 같다.

• 공장 자동화 과정에서 클럭 동기화로 프로그래밍 가능한 로직 컨트롤러 및 센스, 액추에이터, 트라이브, 원격 입출력 상에서 작업과 이벤트를 동기화할 수 있다.

• 의료영상 과정에서 클럭 동기화를 통해 여러 검출기로 추출된 데이터를 빠르게 수집할 수 있다.

• 소프트웨어 정의 무선(SDR) 과정에서 클럭동기화를 통해 고도로 정밀하게 객체를 감지할 수 있다.

• 통신 인프라에서 클럭동기화를 통해 빠른 데이터 레이트에서 시간에 민감한 정보(time-critical information)을 최소한의 인터페이스로 교환할 수 있다.

이더넷은 직렬 통신 표준으로, 비용 효율성과 최소 10Mbps ~ 최대 400 Gbps의 링크를 지원하는 기능 덕분에 인기가 높다. 이더넷 표준은 동기화를 지원하지 않기 때문에 이더넷 링크를 통한 동기화 활성화 방법이 여러가지 있다. 동기화에는 두가지 측면이 있다.

• 클럭 동기화는 미국 전기전자학회(Institute of Electrical and Electronics Engineers, IEEE)의 IEEE 1588 정밀 클럭 프로토콜(Precision Time Protocol) 또는 네트워크 타임 프로토콜(Network Time Protocol)를 통해 처리된다. 현대 시스템에서 클럭 동기화는 중앙 프로세스 장치에 설치된 소프트웨어 스택의 일부 또는 필드-프로그램밍 가능한 게이트 어레이의 일부로 처리된다.

• 주파수 동기화는 동기식 이더넷을 통해 처리되며, 이를 통해 병렬-직렬 송신회로 구간의 레퍼런스 클럭을 단일 마스터 클럭으로 추적할 수 있다. 클럭 지터 클리너(clock jitter cleaner)는 일반적으로 주파수 동기화를 위해 실행된다.

이더넷 링크는 전송 섹션에서 직렬 데이터 스트림에 클럭을 삽입한 후, 수신 섹션에서 데이터 스트림이 병렬화 되기 전에 삽입돼 클럭을 복구하는 방식으로 설정된다.

동기식 이더넷에서는 설계자가 서브시스템에 적합한 레퍼런스 클럭을 생성하는 클럭 장치를 선택하는 것이 중요하다. PHY에서 복구된 클럭에 의한 지터 퍼포먼스가 떨어지는 경우, 외부 VCXOs가 있는 PLL이 초과된 지터 처리 및 전송 이더넷 PHY와 기타 시스템의 클럭을 깨끗하게 복구할 수 있다. 아래 그림 1은 다른 노들 사이에서 기가비트 이더넷 링크가 있는 셋업을 보여준다.

.jpg)

이러한 셋업의 주요 과제는 다음과 같다.

• 이더넷 전송 PHY의 PNM을 충족시키는 외부 VCXO설치 인한 비용 증가

• 지터 클리닝을 위한 외부 아날로그 루프 필터 구성 요소 추가로 인한 보드 공간 증가

• 여러 외부 구성 요소 추가를 위한 고도의 설계로 인한 전반적인 설계 복잡성 및 설계 시간 증가

LMK05318 네트워크 싱크로나이저 클럭은 초고성능의 클럭 생성기이자 지터 클리너로써 위에 설명한 과제를 해결할 수 있으며, 통신 및 산업 애플리케이션의 엄청난 요구 사항을 뛰어넘는다. 이 디바이스는 전압제어발전기로서 TI의 독자적인 벌크탄성파(BAW) 공명기라는 특징이 있다. BMW 공명기는 네트워크 싱크로나이저 직접 회로에서 흔히 볼 수 있는 인덕터-커패시터 오실레이터(inductor-capacitor oscillator)를 대체하는 고품질 공명기다.

수정 진동자(quartz crystal)과 비슷한 박막 공명기로, 기계 에너지를 억제를 위해 금속 필름과 다른 레이어 사이에 끼어있다. 그 결과, 초저 지터 성능을 지닌 고품질 초저음 공명기가 탄생했다.

.jpg)

그림 2는 LNK05318의 기본 구조를 보여준다. LMK05318은 DPLL 또는 BAW VCO를 사용한 APLL에서 루프 대역폭을 설정하는 기능을 사용해 레퍼런스 클럭 지터를 삭제하고, 장치 주위의 저렴한 기성 부품에 이용해 전반적인 PCB 설계를 단순화한다.

LMK05318은 아래 두가지 구성에서 지터 클리너 역할을 할 수 있다.

• DPLL 루프대역폭이 10Hz보다 크면, APLL에 대한 레퍼런스로 크리스탈 오실레이터를 사용해 레퍼런스 인풋 클럭 지터를 제거할 수 있다. 이 구성의 장점은 레퍼런스 인풋 클럭에 존재하는 저주파 소음을 제거할 수 있다는 것이다. 또한, 낮은 오프셋 주파수에 대한 위상 잡음 (phase-noise) 요구사항이 있을 경우, DPLL을 사용한 지터 클리닝으로 인밴드 위상 잡음을 최대한 낮게 줄일 수 있다.

• DPLL 전원이 꺼진 상태에서 100Hz ~ 1kHz 범위의 루프 대역폭 제공하는 APLL 1을 사용해 레퍼런스 인풋 클럭의 고주파 잡음을 제거할 수 있다. 이 구성의 장점은 낮은 오프셋 주파수에 대한 명시적인 위상 잡음 요구사항이 없는 경우에도 외부 크리스탈 오실레이터없이 고주파 잡음을 제거할 수 있다는 것이다. APLL1 구성에는 작은 영역에 적합한 비용 효율적인 솔루션을 적용할 수 있다. 다른 경쟁 지터 클리너 제품과 달리, 크리스탈 기반 부품과 외부 루프 필터 부품이 필요하지 않아 신뢰도가 올라간다.

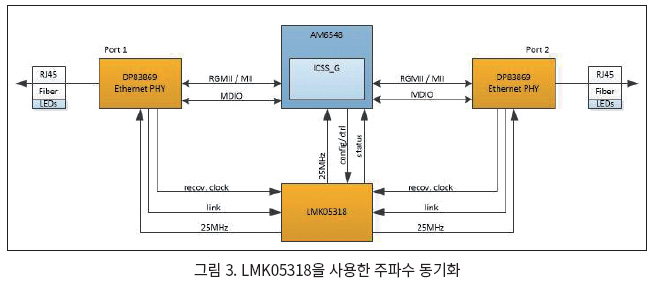

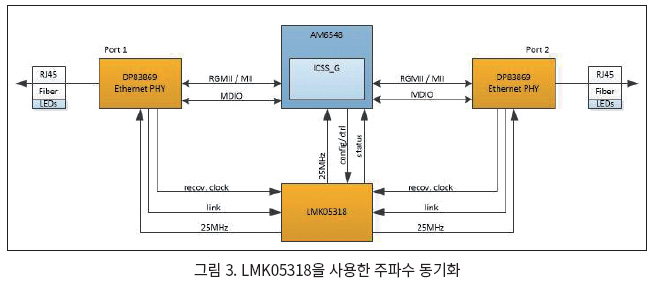

• 그림 3은 LMK05318 보다 간단한 클럭킹 체계를 보여준다. LMK05318은 다른 노드 사이의 기가비트 이더넷 링크 및 칩의 프로세스 장치와 같은 AM6548 시스템, 높은 면역성의 기가비트 이더넷 PHY를 사용해 이더넷 PHY 역할을 하는 DP83869HM을 제공한다.

LMK05318과 같은 TI의 초고성능 클럭 지터 클리너와 싱크로나이저는 실시간 이더넷에서 클럭 동기화를 위한 클럭 트리를 간소화하는 동시에 설계 사이클과 PCB 공간, 시스템 비용을 절감해 준다.

.jpg)

자동화공장 셋업의 효율성 최적화 및 개선, 데이터 수집 시스템의 전반적인 성능 향상 또는 다운로드 시간 감소를 위한 효율적인 장애 감지 및 수정을 원하는가? 앞에 제시된 조건의 전부 또는 일부를 원한다면, 네트워크 동기화(network synchronizer)로 클럭 동기화(clock synchronization)을 활성화하는 방법을 고려할 수 있다.

클럭 동기화란?

이더넷은 전통적으로 통신 시스템에서 유선으로 로컬 영역 네트워크(LAN)를 연결했다. 최근에는 산업용과 자동화용 애플리케이션의 서브시스템을 연결하는 실질적인 표준이 됐다. 레퍼런스 클럭(Reference clock)은 이더넷 링크 작동을 위해 필요하며, 대개 프리런닝 클럭 소스에서 생성된다. 시간 동기화는 전체 시스템의 단일 마스터 클럭으로 추적 가능한 서브시스템에서 클럭을 생성하는 기능이다.

클럭 동기화는 많은 엔드 애플리케이션에 유용하며, 예는 다음과 같다.

• 공장 자동화 과정에서 클럭 동기화로 프로그래밍 가능한 로직 컨트롤러 및 센스, 액추에이터, 트라이브, 원격 입출력 상에서 작업과 이벤트를 동기화할 수 있다.

• 의료영상 과정에서 클럭 동기화를 통해 여러 검출기로 추출된 데이터를 빠르게 수집할 수 있다.

• 소프트웨어 정의 무선(SDR) 과정에서 클럭동기화를 통해 고도로 정밀하게 객체를 감지할 수 있다.

• 통신 인프라에서 클럭동기화를 통해 빠른 데이터 레이트에서 시간에 민감한 정보(time-critical information)을 최소한의 인터페이스로 교환할 수 있다.

이더넷은 직렬 통신 표준으로, 비용 효율성과 최소 10Mbps ~ 최대 400 Gbps의 링크를 지원하는 기능 덕분에 인기가 높다. 이더넷 표준은 동기화를 지원하지 않기 때문에 이더넷 링크를 통한 동기화 활성화 방법이 여러가지 있다. 동기화에는 두가지 측면이 있다.

• 클럭 동기화는 미국 전기전자학회(Institute of Electrical and Electronics Engineers, IEEE)의 IEEE 1588 정밀 클럭 프로토콜(Precision Time Protocol) 또는 네트워크 타임 프로토콜(Network Time Protocol)를 통해 처리된다. 현대 시스템에서 클럭 동기화는 중앙 프로세스 장치에 설치된 소프트웨어 스택의 일부 또는 필드-프로그램밍 가능한 게이트 어레이의 일부로 처리된다.

• 주파수 동기화는 동기식 이더넷을 통해 처리되며, 이를 통해 병렬-직렬 송신회로 구간의 레퍼런스 클럭을 단일 마스터 클럭으로 추적할 수 있다. 클럭 지터 클리너(clock jitter cleaner)는 일반적으로 주파수 동기화를 위해 실행된다.

이더넷 링크는 전송 섹션에서 직렬 데이터 스트림에 클럭을 삽입한 후, 수신 섹션에서 데이터 스트림이 병렬화 되기 전에 삽입돼 클럭을 복구하는 방식으로 설정된다.

동기식 이더넷에서는 설계자가 서브시스템에 적합한 레퍼런스 클럭을 생성하는 클럭 장치를 선택하는 것이 중요하다. PHY에서 복구된 클럭에 의한 지터 퍼포먼스가 떨어지는 경우, 외부 VCXOs가 있는 PLL이 초과된 지터 처리 및 전송 이더넷 PHY와 기타 시스템의 클럭을 깨끗하게 복구할 수 있다. 아래 그림 1은 다른 노들 사이에서 기가비트 이더넷 링크가 있는 셋업을 보여준다.

.jpg)

이러한 셋업의 주요 과제는 다음과 같다.

• 이더넷 전송 PHY의 PNM을 충족시키는 외부 VCXO설치 인한 비용 증가

• 지터 클리닝을 위한 외부 아날로그 루프 필터 구성 요소 추가로 인한 보드 공간 증가

• 여러 외부 구성 요소 추가를 위한 고도의 설계로 인한 전반적인 설계 복잡성 및 설계 시간 증가

LMK05318 네트워크 싱크로나이저 클럭은 초고성능의 클럭 생성기이자 지터 클리너로써 위에 설명한 과제를 해결할 수 있으며, 통신 및 산업 애플리케이션의 엄청난 요구 사항을 뛰어넘는다. 이 디바이스는 전압제어발전기로서 TI의 독자적인 벌크탄성파(BAW) 공명기라는 특징이 있다. BMW 공명기는 네트워크 싱크로나이저 직접 회로에서 흔히 볼 수 있는 인덕터-커패시터 오실레이터(inductor-capacitor oscillator)를 대체하는 고품질 공명기다.

수정 진동자(quartz crystal)과 비슷한 박막 공명기로, 기계 에너지를 억제를 위해 금속 필름과 다른 레이어 사이에 끼어있다. 그 결과, 초저 지터 성능을 지닌 고품질 초저음 공명기가 탄생했다.

.jpg)

그림 2는 LNK05318의 기본 구조를 보여준다. LMK05318은 DPLL 또는 BAW VCO를 사용한 APLL에서 루프 대역폭을 설정하는 기능을 사용해 레퍼런스 클럭 지터를 삭제하고, 장치 주위의 저렴한 기성 부품에 이용해 전반적인 PCB 설계를 단순화한다.

LMK05318은 아래 두가지 구성에서 지터 클리너 역할을 할 수 있다.

• DPLL 루프대역폭이 10Hz보다 크면, APLL에 대한 레퍼런스로 크리스탈 오실레이터를 사용해 레퍼런스 인풋 클럭 지터를 제거할 수 있다. 이 구성의 장점은 레퍼런스 인풋 클럭에 존재하는 저주파 소음을 제거할 수 있다는 것이다. 또한, 낮은 오프셋 주파수에 대한 위상 잡음 (phase-noise) 요구사항이 있을 경우, DPLL을 사용한 지터 클리닝으로 인밴드 위상 잡음을 최대한 낮게 줄일 수 있다.

• DPLL 전원이 꺼진 상태에서 100Hz ~ 1kHz 범위의 루프 대역폭 제공하는 APLL 1을 사용해 레퍼런스 인풋 클럭의 고주파 잡음을 제거할 수 있다. 이 구성의 장점은 낮은 오프셋 주파수에 대한 명시적인 위상 잡음 요구사항이 없는 경우에도 외부 크리스탈 오실레이터없이 고주파 잡음을 제거할 수 있다는 것이다. APLL1 구성에는 작은 영역에 적합한 비용 효율적인 솔루션을 적용할 수 있다. 다른 경쟁 지터 클리너 제품과 달리, 크리스탈 기반 부품과 외부 루프 필터 부품이 필요하지 않아 신뢰도가 올라간다.

• 그림 3은 LMK05318 보다 간단한 클럭킹 체계를 보여준다. LMK05318은 다른 노드 사이의 기가비트 이더넷 링크 및 칩의 프로세스 장치와 같은 AM6548 시스템, 높은 면역성의 기가비트 이더넷 PHY를 사용해 이더넷 PHY 역할을 하는 DP83869HM을 제공한다.

LMK05318과 같은 TI의 초고성능 클럭 지터 클리너와 싱크로나이저는 실시간 이더넷에서 클럭 동기화를 위한 클럭 트리를 간소화하는 동시에 설계 사이클과 PCB 공간, 시스템 비용을 절감해 준다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

본 기사의 전문은 PDF문서로 제공합니다.

(로그인필요)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

다운로드한 PDF문서를 웹사이트, 카페, 블로그등을 통해 재배포하는 것을 금합니다. (비상업적 용도 포함)

100자평 쓰기