이 글에서는 전원 설계가 RF 증폭기 위상 잡음에 어떠한 영향을 미치는지 살펴본다. 수집된 데이터를 분석해 보면, 적절한 전원 모듈을 선택함으로써 위상 잡음을 10dB까지 향상할 수 있으며, 따라서 적절한 전원 모듈 선택이 RF 신호 체인 성능을 최적화하기 위해 중요하다는 것을 알 수 있다.

.jpg)

글 / 미첼 스턴버그(Mitchell Sternberg) 시스템 AE, 에르칸 아카르(Erkan Acar) RF 시스템 AE,

데이비드 응(David Ng) 전원 시스템 매니저, 시드니 웰즈(Sydney Wells) AE

아나로그디바이스(Analog Devices, Inc.)

오늘날 RF(radio frequency) 시스템은 갈수록 더 복잡해지고 있다. 이처럼 복잡성이 높아짐에 따라 엄격한 링크 및 잡음 예산을 비롯한 시스템의 모든 측면에 걸쳐서 최상의 성능을 달성하는 것이 요구된다. 이러한 요구를 충족하기 위해서는 전체 신호 체인을 적절히 설계하는 것이 중요하다.

이 신호 체인 상에서 흔히 간과되는 부분이 DC 전원이다. DC 전원은 시스템을 작동하는 데 있어서 중요한 역할을 하지만, 한편으로는 원치 않는 효과를 불러올 수 있다. RF 시스템에서 중요한 성능 중 하나가 위상 잡음인데, 어떤 전원 솔루션을 선택하는가에 따라 해당 지표가 나빠질 수 있다. 이 글에서는 전원 설계가 RF 증폭기 위상 잡음에 어떠한 영향을 미는지 살펴본다. 수집된 데이터를 분석해 보면, 적절한 전원 모듈을 선택함으로써 위상 잡음을 10dB까지 향상할 수 있으며, 따라서 적절한 전원 모듈 선택이 RF 신호 체인 성능을 최적화하기 위해 중요하다는 것을 알 수 있다.

위상 잡음이란?

위상 잡음(phase noise)이란 신호가 수신단에 도달할 때 예상치 않게 앞서거나 뒤쳐짐으로 인해 신호에 존재하는 잡음을 말한다. 진폭 잡음(amplitude noise)이 신호의 공칭 진폭으로부터 벗어나는 편이나 편차인 것과 마찬가지로, 위상 잡음은 신호의 공칭 위상으로부터 벗어나는 편이나 편차이다. 이상적인 오실레이터는 공식 1로 표현되는 것과 같은 사인파를 출력한다:

이 사인파는 완벽한 주기성을 가지며, Videal(t)의 푸리에 변환은 출력 파형의 주파수에서 델타 함수로 나타난다. 오실레이터 출력의 보다 현실적인 표현식은 위상(및 진폭)에 있어서 임의적인 변동성을 포함한다(공식 2):

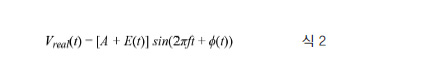

이 파형은 일종의 확률 프로세스(stochastic process) φ(t)를 포함하는데, 이것이 신호의 위상을 약간 이동시킨다. 위상에서 이러한 편이로 인해 그림 1과 같은 비이상적 클럭 출력의 푸리에 변환이 일어난다.

약간의 위상 편이로 인해, 이제 이 신호에는 1개 이상의 주파수 성분이 존재한다. 그러므로 신호는 중심 주파수를 중심으로 확산된다.

위상 잡음의 요인과 여파

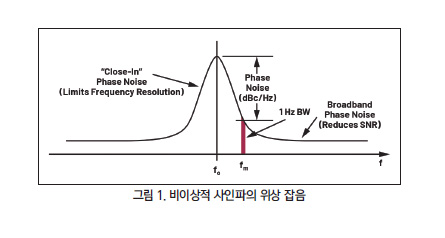

중요하지만 흔히 간과되는 위상 잡음의 요인이 신호 체인의 DC 전원 솔루션이다. 신호 체인에 전원을 공급하는 전원 레일에서 발생하는 어떠한 잡음이나 리플은 내부적으로 결합될 수 있다. 이는 위상 잡음의 증가로 이어질 수 있으며, 그러면 송신되는 대역폭에서 중요한 주파수 성분들을 가리거나 또는 반송파로부터 스퍼 오프셋을 유발할 수 있다. 이러한 스퍼는 반송파에 가까이 있어서 처리하기가 특히 어려울 수 있고, 엄격한 전이 대역 요구 때문에 필터링하기가 까다로울 수 있다.

많은 다양한 요인들이 위상 잡음의 원인이 될 수 있다. 그 중에서도 화이트 플로어 잡음(white floor noise), 샷 잡음(shot noise), 1/f 혹은 플리커 잡음(flicker noise)이 세 가지 주된 요인으로 알려져 있다. 화이트 플로어 잡음은 전류가 통과할 때 자유 전자의 임의적인 열적 이동으로 인한 것이다. 샷 잡음도 이와 비슷한데, 전류 흐름의 임의적인 특성으로 인한 것이다.

이들과 달리, 플리커 잡음은 주파수에 따라 달라진다. 반도체 격자 구조의 결함으로 인해 발생하는 플리커 잡음 역시 특성적으로임의적이다. 플리커 잡음은 주파수에 따라서 감소한다. 그러므로 낮은 1/f 코너 주파수가 매우 바람직하다. 통상적인 위상 잡음 곡선은 기울기가 1/fx인 구간들에 의해 근사화되는데, 여기서 x = 0은 화이트 플로어 잡음 구간이고(기울기 = 0dB/decade), x = 1은 플리커 위상 잡음 구간에 해당한다(기울기 = -20dB/decade). x = 2, 3, 4인 구간들은 반송파 주파수에 좀더 가깝다.

전원 솔루션

RF 신호 체인 상에서 증폭기로 전원을 적절히 바이어싱하고 공급하는 것은 그리 쉽지 않은데, 특히 드레인 전압이 출력 포트로도 사용될 경우 그렇다. 시중에는 다양한 유형의 전원 솔루션과 토폴로지가 나와 있다. 어떤 전원 솔루션을 사용할 것인가는 애플리케이션과 시스템 요구에 따라서 달라질 것이다.

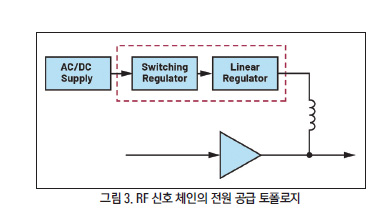

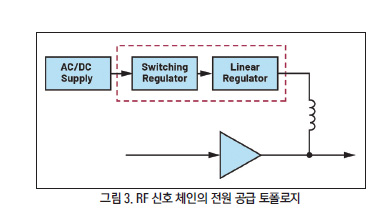

이 글에서 설명하는 실험에서는, 그림 3에서 보는 것과 같이 LDO(low dropout) 선형 레귤레이터와 스텝다운(Buck) 스위칭 레귤레이터를 사용해서 데이터를 확보했다. Buck 스위칭 레귤레이터는, 전압 강하가 크고 높은 효율로 낮은 온도에서 동작하는 경우에 통상적으로 사용되는 솔루션이다.

스위칭 전원장치는 예컨대 12V 같이 보다 높은 전압을 3.3V와 1.8V 같은 통상적인 칩 레벨 전압으로 스텝다운할 수 있다. 하지만 이 장치는 출력 전압에 심한 스위칭 잡음이나 리플을 발생할 수 있으며, 이는 상당한 성능 저하로 이어질 수 있다. LDO 레귤레이터는 이러한 전압들을 스텝다운할 수 있으면서 더 적은 잡음을 발생한다. 하지만 전력 소산이 주로 발열로 나타난다. LDO 레귤레이터를 사용하는 것은 입력과 출력 전압 사이에 차이가 작을 때 좋은 선택이다. 하지만 접합부-대-주변 열 저항(θJA)이 30℃/W 이상일 때는 FPGA와 ASIC의 높은 전류 소모가 LDO 레귤레이터의 성능을 빠르게 저하시킬 수 있다.

테스트 셋업

이번 실험에는 아나로그디바이스(Analog Devices)의 3가지 전원 제품인 LTM8063, LTM4626, LT3045이 사용됐다. 표 1은 이들 전원 솔루션의 데이터 시트 명세 내역을 요약해서 정리한 것이다.

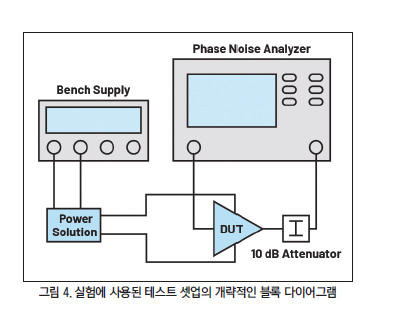

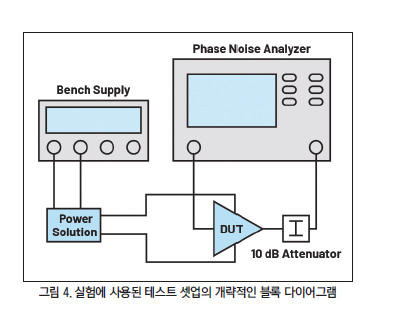

입력 신호는 100MHz, 200MHz, 500MHz, 그리고 1GHz부터 10GHz까지의 주파수 범위를 스윕했다. 위상 잡음은 10Hz ~ 30MHz의 주파수 오프셋으로 분석했다. 그림 4는 테스트 셋업을 보여준다. 입력 RF 신호는 로데슈바르츠(Rohde & Schwarz) FSWP50 위상 잡음 분석기를 사용해서 내부적으로 발생시켰다. 이 오실레이터는 성능이 매우 우수한 데다, 전원장치로 인해 발생하는 부가적인 위상 잡음이나 변조 스퍼를 ADI확실하게 보여줄 수 있다는 점에서 이번 실험에 사용됐다.

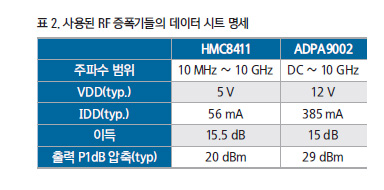

RF 신호 체인의 블록을 보여주기 위해 2개의 ADI 증폭기 제품을 사용했다.

결과

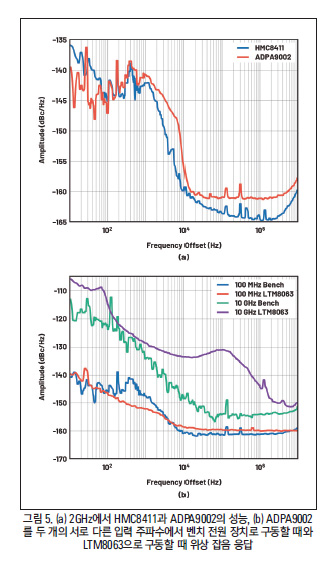

그림 5는 PA를 LTM8063을 사용해서 구동할 때와 벤치 전원 장치로 구동할 때 위상 잡음 응답을 비교해서 보여준다. 이 PA는 1/f 주파수를 지나서 성능이 약간 떨어지는 것으로 관찰된다. 이 PA는 훨씬 더 많은 전류를 소모하고, 이로써 위상 잡음이 대략 2dB ~ 4dB 증가하는 것으로 나타난다.

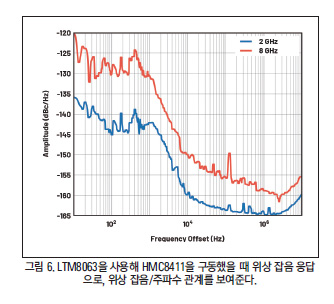

그림 6은 2GHz와 8GHz의 입력 주파수일 때 HMC8411의 위상 잡음 응답을 보여준다. 이 응답은 공식 3으로 표현된 것과 같은 일반적인 위상 잡음/주파수 관계를 그대로 따르고 있다.

이 관계식을 보면, 입력 주파수가 두 배가 될 때마다 위상 잡음이 약 6dB 증가한다는 것을 알 수 있다. 그러므로 주파수가 4배일 때 10Hz ~ 100Hz 주파수 오프셋으로부터 위상 잡음이 약 12dB 증가하는 것을 볼 수 있다.

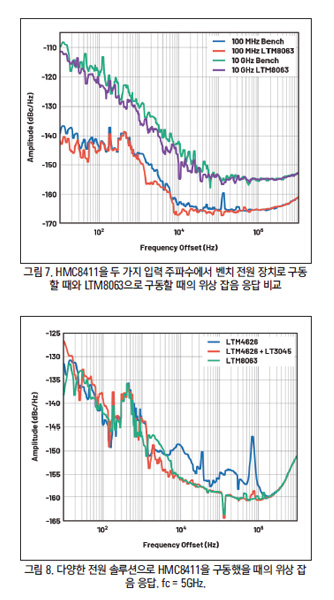

그림 7에서는 HMC8411을 100MHz와 10GHz에서 LTM8063으로 구동할 때와 벤치 전원 장치를 사용해서 구동할 때의 위상 잡음 응답을 보여준다. 여기서는 벤치 전원 장치의 위상 잡음 응답을 특정 전원 솔루션의 성능을 판단하기 위한 기준으로 사용했다. 실험에서 LTM8063은 광범위한 잡음 플로어에서 약 2dB 증가했을 뿐, 벤치 전원 장치와 비교할 때 다양한 주파수에 걸쳐 극히 우수한 성능을 나타낸다는 것을 알 수 있다.주전원장치로는 LTM4626 같은 고전류 모듈을 사용하는 것이 일반적이다. 각 회로 블록의 요구 사항에 따라 전원 분배 네트워크를 스텝다운할 수 있기 때문이다.

그림 8에서는, LTM8063이 LTM4626과 LT3045 초저잡음 LDO 레귤레이터를 캐스케이드 방식으로 결합해서 사용한 것과 비슷한 위상 잡음 성능을 나타낸다는 것을 알 수 있다. 만약 LTM8063이 제공하는 전압과 전류 출력이 설계 요구를 충족하기만 한다면, 이 전원 솔루션을 사용함으로써 상당한 비용과 보드 공간을 절약할 수 있다.

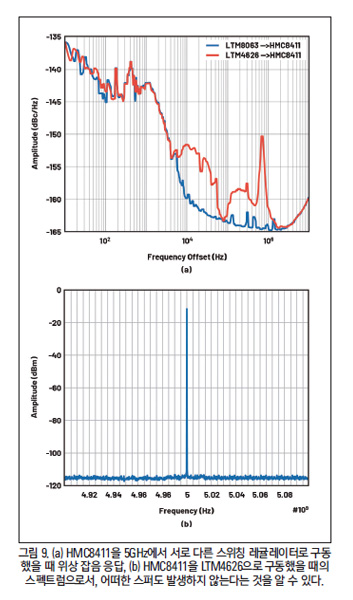

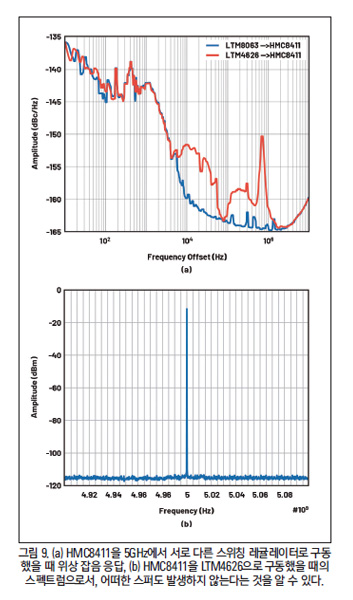

그림 9a에서는, 스위칭 전원 공급 장치들이 다양한 주파수 대역에서 확연히 다른 동작을 보여준다는 것을 알 수 있다. LTM8063과 LTM4626은 5kHz 이하에서는 전원 LNA 위상 잡음에 대해 비슷하게 미미한 영향을 미치지만, 그 이상에서는 크게 다른 양상을 나타낸다.

LTM4626은 하이엔드 디지털 제ADI품에 사용하도록 최적화되었다. 이들 디바이스는 통상적으로 높은 효율과 빠른 과도 응답을 요구하므로, 이들 디바이스에 사용되는 전원 장치는 매우 낮은 패시브 임피던스, 빠른 스위칭 에지 레이트, 그리고 높은 제어 루프 이득 및 대역폭 같은 특성을 가질 수 있다. 이러한 특성은 출력 전압에서 수 밀리볼트(mV)의 섭동(perturbation)을 발생할 수 있다.

이러한 섭동이 디지털 시스템에서는 그리 대수롭지는 않다 하더라도, 신호 체인 제품의 성능을 떨어뜨릴 수 있다. 그런데 그림 9b에서는 LTM4626을 사용했을 때의 출력 스펙트럼이 102.7dB의 SFDR로 그리 주목할 만한 스퍼를 발생하지 않는다는 것을 알 수 있다. 하지만, LTM8063은 EMI나 출력 모두에 있어서 저잡음을 위해 설계됨으로써 신호 체인 애플리케이션에서 성능을 극대화한다. 이 제품은 저주파수 안정성이 매우 우수하고, 출력 섭동이 낮을 뿐 아니라, 스위칭 기본 주파수 및 해당 고조파에서 훨씬 더 낮은 잡음을 발생한다.

맺음말

신호 체인 분석 작업을 수행할 때는 모든 잡음 요인들을 고려해야 한다. 흔히 간과되는 요인 중의 하나가 DC 전원 솔루션인데, 신호 체인에 전원을 공급하는 전원 레일에서 발생하는 어떠한 잡음이나 리플은 내부적으로 결합해서 신호 체인 성능을 심각하게 저하할 수 있다.

이 글에서는 적절한 전원 모듈을 선택하는 것이 매우 중요하며, 10kHz 오프셋에서 위상 잡음을 많게는 10dB까지 향상할 수 있다는 것을 확인했다. 이 애플리케이션의 경우, LTM8063이 가장 우수한 결과를 나타냈다. LTM4626과 LT3045를 캐스케이드 방식으로 결합한 것이 이와 비슷한 수준의 위상 잡음 성능을 보여줬지만, RF 신호 체인을 최적화하기 위해서는 정확한 전원 솔루션을 선택하는 것이 중요하다는 것을 재확인할 수 있었다.

참고문헌

Acar, Erkan. “Why a Fully Integrated Translation Loop Device Achieves the Best Phase Noise Performance.” Analog Devices, Inc., April 2021.

Bergeron, Jarrah. “Analyzing and Managing the Impact of Supply Noise and Clock Jitter on High Speed DAC Phase Noise.” Analog Dialogue, Vol. 51, No. 1, March 2017.

Delos, Peter, and Jarrett Liner. “Improved DAC Phase Noise Measurements Enable Ultralow Phase Noise DDS Applications.” Analog Dialogue, Vol. 51, No. 3, August 2017.

Kester, Walt. “MT-008 Tutorial: Converting Oscillator Phase Noise to Time Jitter.” Analog Devices, Inc., 2009.

Liu, Leo. “Comprehensively Understand and Analyze Switching Regulator Noise.” Analog Devices, Inc., January 2019.

저자 소개

미첼 스턴버그(Mitchell Sternberg)는 아나로그디바이스(Analog Devices) 계측기 팀의 시스템 애플리케이션 엔지니어(AE)이다. 신호 체인 설계 및 분석, 신호 및

전원 무결성, 무선 통신 시스템과 관련해서 풍부한 경험을 쌓고 있다. 이전에는 이더넷 적합성 테스트와 관련해서 테스트 엔지니어 및 하드웨어 개발자로서

다양한 직책을 역임했다. 뉴햄프셔 대학(뉴햄프셔주 더럼)에서 전기공학 학사학위를 취득했다.

에르칸 아카르(Erkan Acar)는 듀크 대학(노스캐롤라이나주 더럼)에서 박사학위 및 석사학위를 취득했다. 저가형 RF 테스트, 자동화 테스트 장비(ATE), 고속

인터페이스의 신호 및 전원 무결성과 관련한 다수의 연구개발 프로젝트를 이끌었다. 다수의 특허를 보유하고, 다수의 논문을 발표했다. 현재는 베이스밴드

부터 110GHz 이상에 이르는 RF 및 밀리미터파 신호 체인을 맡고 있다.

데이비드 응(David Ng)은 아나로그디바이스(캘리포니아)의 전원 시스템 매니저이다. 산업용, 항공우주, 의료 애플리케이션용 고성능 ADC, DAC, 트랜시버, 증폭기,

기타 신호 체인 디바이스 구동에 필요한 전원 솔루션 개발을 책임지고 있다. LTM8000 ?Module? 제품 라인을 탄생시키고 수익성 좋은 사업부로 성공적으로

성장시켰다.

시드니 웰즈(Sydney Wells)는 현재 ADI의 필드 개발 순환 프로그램에 참여하여 FAE로서의 역할을 수련 중이다. 2020년에 코네티컷 대학에서 전기공학

학사학위를 취득했다. 이전에는 전력 변환기 평가, 제조 자동화, 공급자 개발 엔지니어링과 관련한 업무를 담당했다. 현재는 전원과 계측기를 맡고 있다.

<저작권자©스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)