하이-사이드 N채널 MOSFET 스위치를 사용하는 핫스왑 소자는 기동 시나 전류 제한 동작 중에 발진이 발생할 수 있다. 이는 새로운 문제가 아니지만, 데이터시트에는 이에 대한 해결 방법이 상세히 설명되지 않은 경우가 많다. 근본적인 원리를 이해하지 않은 채 간단한 해결책으로 소형 게이트 저항을 추가하는 것은 오히려 발진이 발생하기 쉬운 레이아웃이 될 수 있다. 이 글은 기생 발진(parasitic oscillation)의 이론을 설명하고, 솔루션을 올바르게 구현하기 위한 가이드를 제공하는 것을 목표로 한다.

글: 아론 샤피로(Aaron Shapiro) 제품 애플리케이션 엔지니어

머리말

하이-사이드 N채널 MOSFET(NFET)을 사용하는 핫스왑, 서지 스토퍼, eFuse, 아이디얼 다이오드 컨트롤러는 기동 시와 전압/전류 제어 동작 중에 발진이 발생할 수 있다. 데이터시트에서는 일반적으로 이 문제를 짧게 언급하고 있으며, 그에 대한 해결 방법으로 소형 게이트 저항을 추가할 것을 권장한다.

그러나 발진의 근본 원인에 대한 명확한 이해가 없으면 레이아웃에서 게이트 저항의 위치를 부적절하게 배치하게 되고, 그 결과 회로가 발진에 취약해질 수 있다. 이 글은 기생 발진의 이론을 설명함으로써 보드 재설계를 예방하는 데 목적이 있다.

처음에는 게이트 저항을 추가하는 것이 불필요해 보일 수 있는데, 이는 NFET의 게이트를 마주보고 있는 저항이 이론적으로 무한대이기 때문이다. 사용자는 이 부품을 생략해도 문제가 없을 것이라 생각하고, 게이트 저항이 필요한지 의문을 가질 수 있다. 그러나 10Ω 게이트 저항은 게이트 노드에서 발생하는 링잉을 억제하기 위한 예방 수단이다. 게이트 노드는 그 자체로 탱크 회로(tank circuit)의 요소를 갖고 있으며, 그 시작점은 게이트 트레이스이다. 긴 PCB 트레이스는 기생 인덕턴스와 인접한 접지면에 대한 분포 정전용량을 유발해, 고주파 성분이 접지로 흐르는 경로를 형성한다. 높은 안전 동작 영역(SOA)에 최적화된 파워 FET는 나노패럿(nf) 단위의 게이트 정전용량을 가지며, 더 큰 전류 처리를 위해 여러 개의 FET를 병렬로 연결하면 이 효과는 더욱 커진다. FET의 VGS를 클램프하기 위해 사용되는 제너 다이오드(Zener diode) 역시 기생 정전용량을 추가하지만, 전체적으로는 파워 FET의 입력 정전용량(CISS)이 지배적이다.

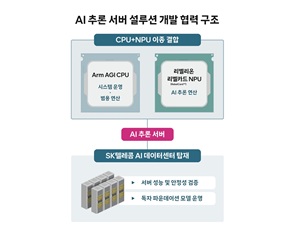

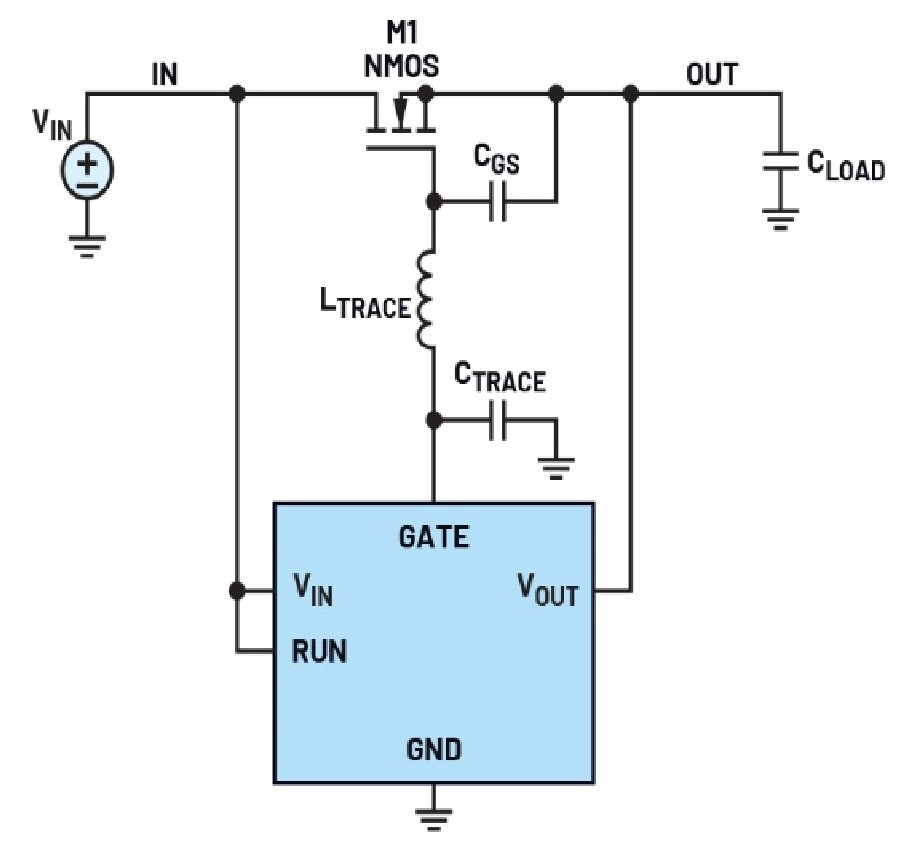

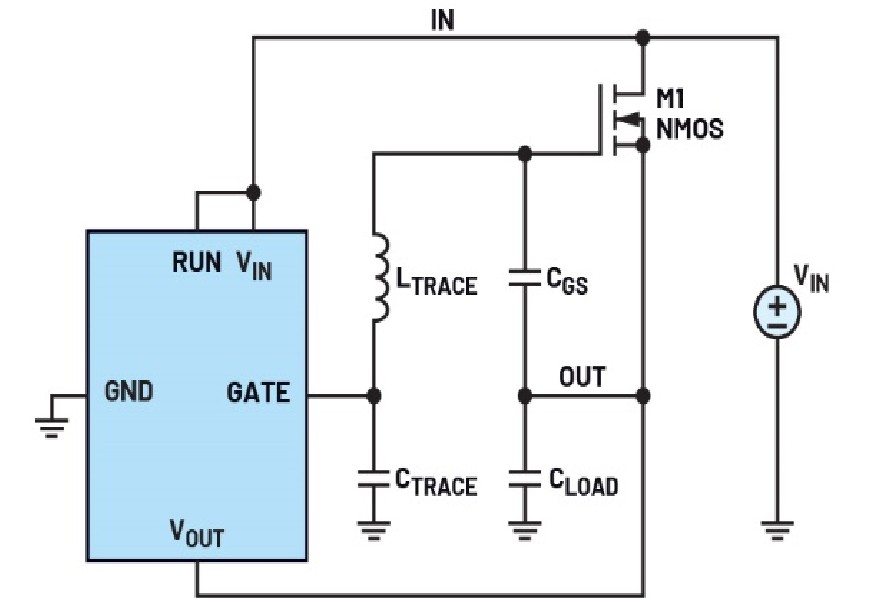

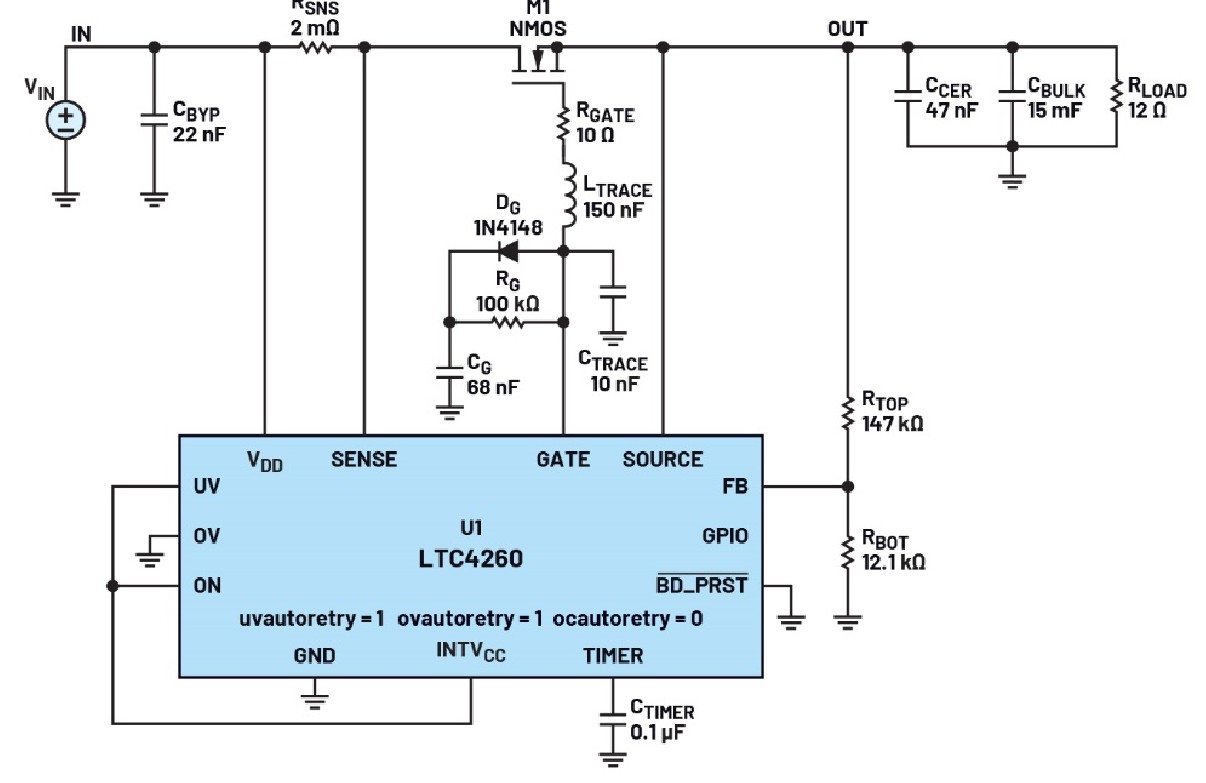

그림 1은 기생 성분을 포함하고 있는 일반적인 PowerPath™ 컨트롤러를 보여준다.

그림 1. 일반적인 PowerPath 컨트롤러

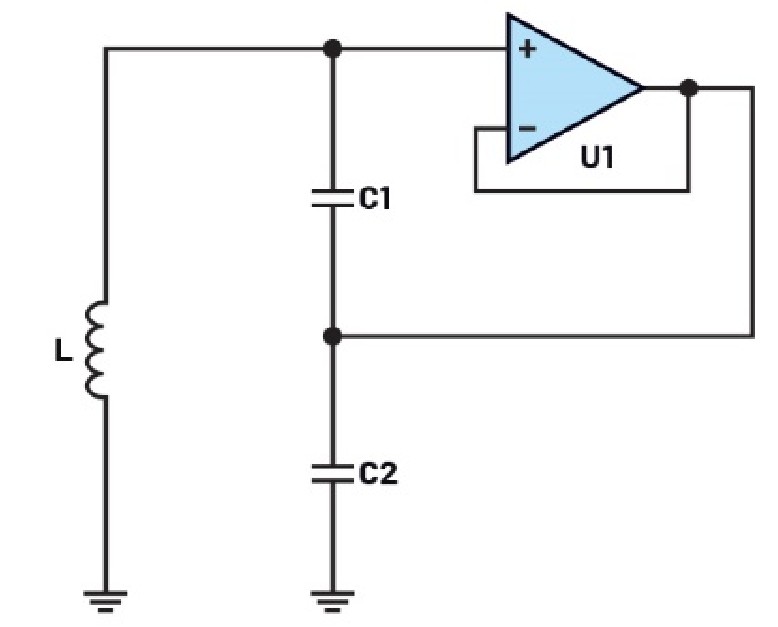

이 회로를 회전해 보면(그림 2), 콜피츠 발진기(Colpitts oscillator)와 유사한 구조임을 확인할 수 있다(그림 3). 이는 이득이 추가된 탱크 회로로, 지속적인 발진을 만들어낼 수 있는 형태다. 이러한 구성은 N채널 FET를 사용하는 PowerPath 컨트롤러에서 쉽게 확인할 수 있다.

그림 2. 회전시킨 PowerPath 컨트롤러

그림 3. 콜피츠 발진기

콜피츠 발진기는 커패시터 분배기를 통해 양(+)의 피드백을 제공하는 버퍼를 사용한다. PowerPath 컨트롤러에서는 이 역할을 FET가 수행한다. FET는 공통 드레인/소스 팔로워 구성이므로, 드레인 전류가 높을수록 성능이 향상되는 AC 버퍼처럼 작동한다. 커패시터 분배기 상단의 신호가 분배기의 중간 지점에 주입되어 분배기 상단의 신호 상승을 유발하고, 이 과정이 반복된다.

발진은 FET가 완전히 턴온되지 않은 상태에서 발생할 수 있으며, 몇 가지 예를 들면 다음과 같다:

1. 초기 기동 과정에서 게이트 전압이 상승하고 출력 커패시터가 충전될 때.

2. 전류가 조절되고 있을 때(컨트롤러가 능동 전류 제한 기능을 사용하는 경우).

3. 전압이 조절되고 있을 때(서지 스토퍼에서 관찰되는 경우).

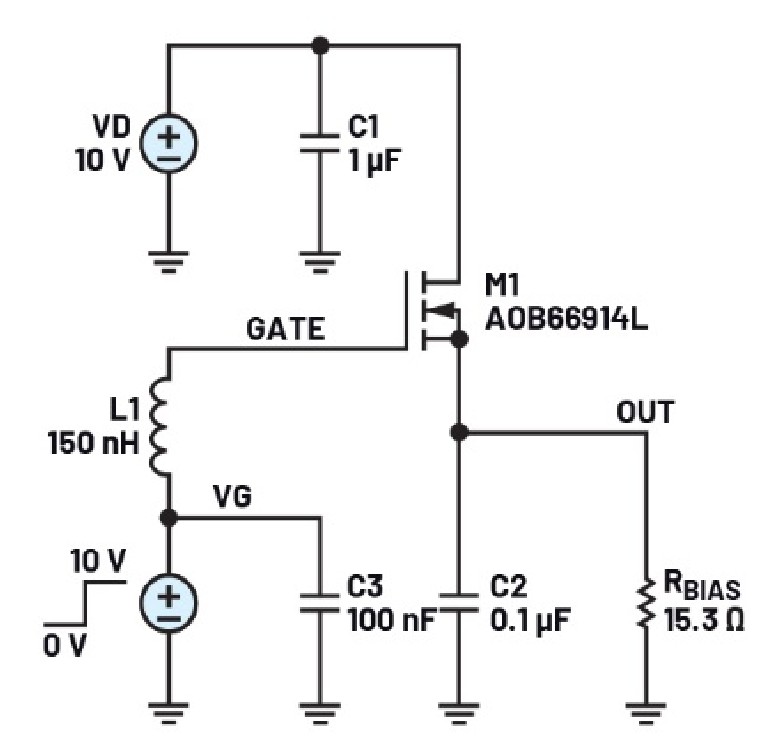

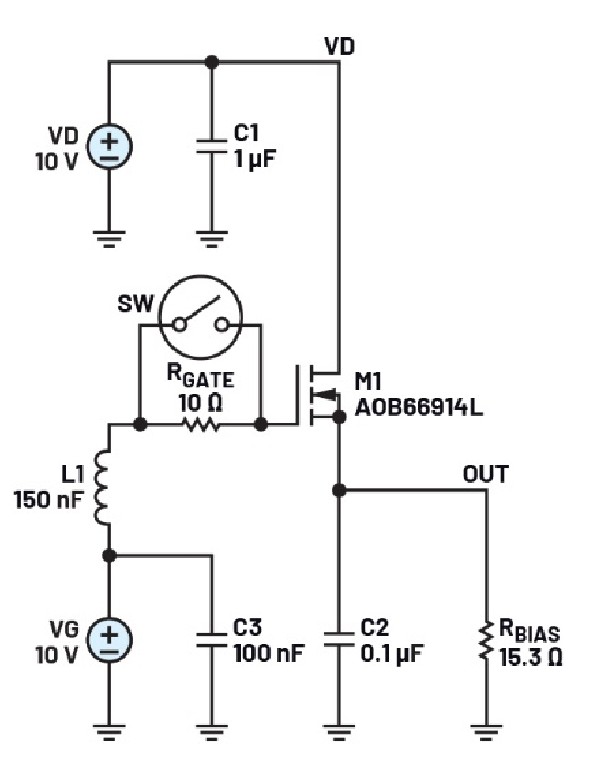

스위치 FET가 콜피츠 발진기 토폴로지에 놓여 있다는 개념을 검증하기 위해, 기본 회로를 게이트 드라이버 IC 없이 구성했다(그림 5). 그림 4에 개별 부품으로 표시되지는 않았지만, 이 회로에서 FET의 CGS는 C2와 함께 커패시터 분배기를 형성한다.

그림 4. 콜피츠 발진기로 구성한 NFET 테스트 회로

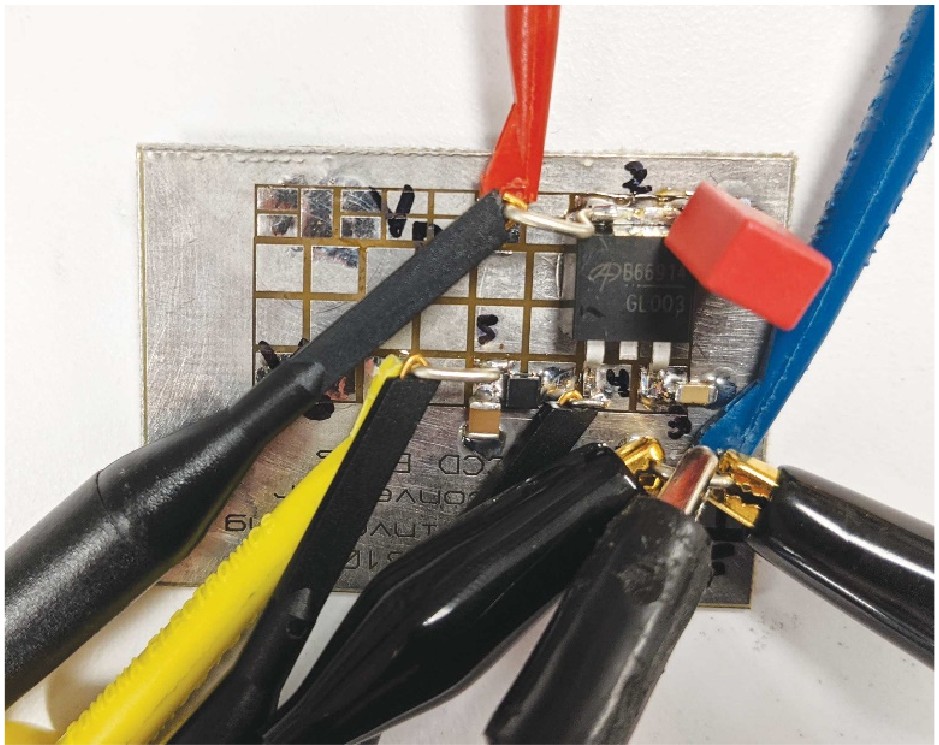

그림 5. 회로 프로토타입

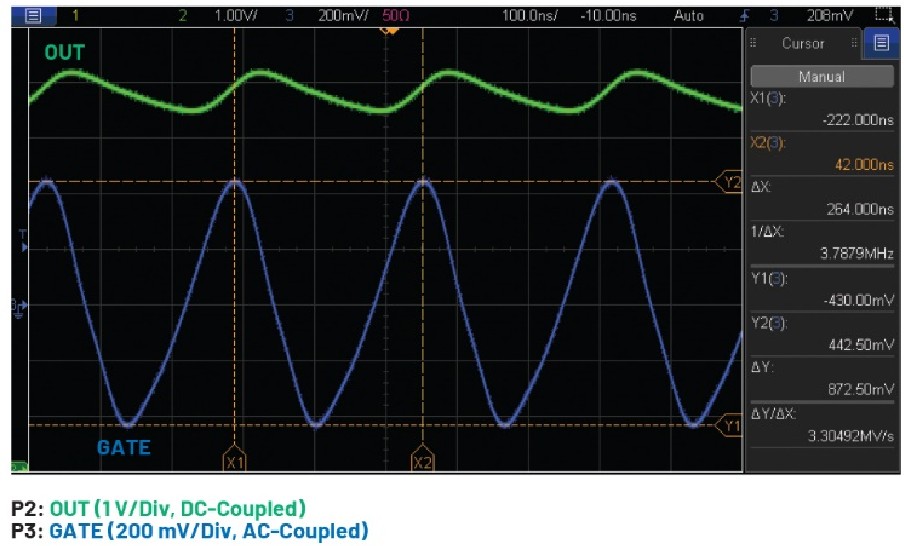

그림 6. DC를 인가했을 때 발진이 발생하는 모습을 보여주는 오실로스코프 파형

그림 6에서는 발진이 관찰되며, 이는 하이-사이드 NFET 스위치가 콜피츠 토폴로지에 놓여 있음을 뒷받침한다.

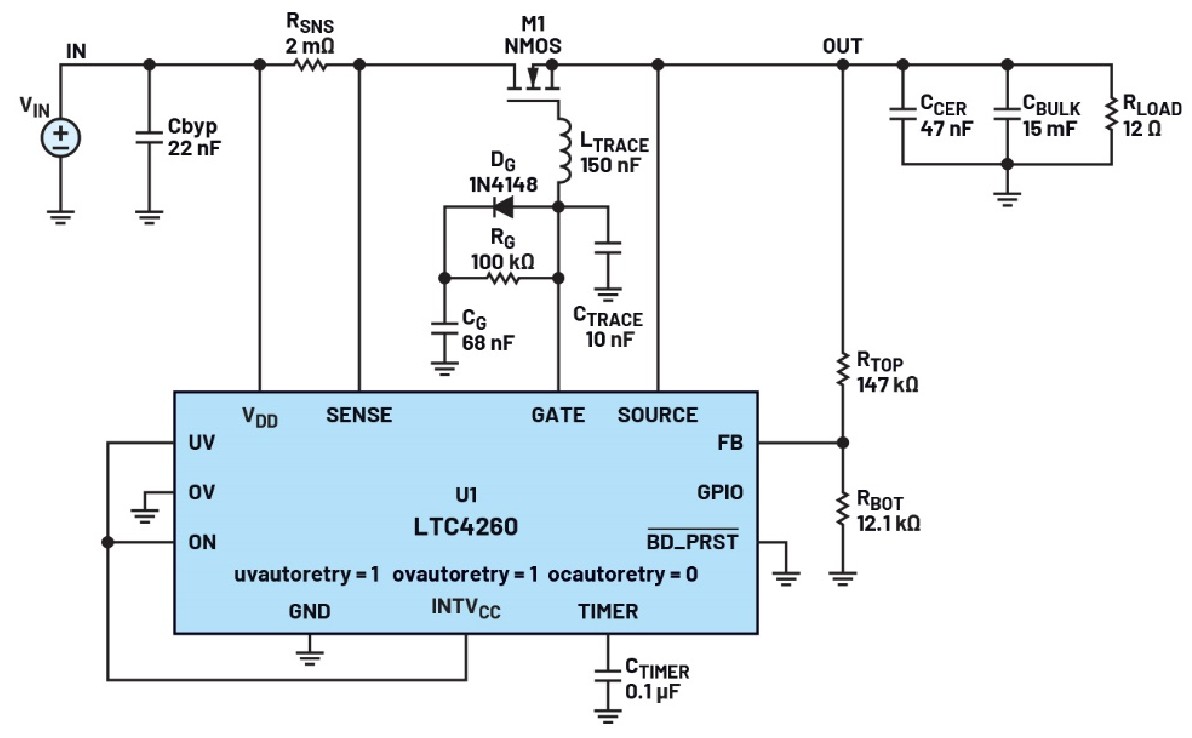

이제 핫스왑 컨트롤러로 넘어가 발진을 유도하도록 수정할 수 있는지 살펴본다. 데모 보드를 사용해 커패시티브 부하로 기동을 수행한다. 기동 과정에서 게이트 전압은 설정된 dV/dt로 상승하며, 출력 전압도 이를 따라 상승한다. 공식 IINRUSH = CLOAD × dV/dt에서 알 수 있듯이, 출력 커패시터로 유입되는 돌입 전류는 dV/dt에 의해 제어된다. FET의 트랜스컨덕턴스(gm)를 증가시키기 위해 돌입 전류를 비교적 큰 3A로 설정했다. 테스트 설정은 다음과 같다(그림 7):

-UV 및 OV 기능은 비활성화했다.

-CTRACE는 트레이스 정전용량을 나타내며, 10 nF 세라믹 커패시터를 추가로 사용했다.

-LTRACE는 트레이스 인덕턴스를 나타내며, LT4260의 GATE 핀과 NFET의 게이트 사이에 150 nH 인덕터를 추가했다.

-2 mΩ 감지 저항을 사용해 폴드백 전류 제한을 10A로 설정했다.

-68 nF 게이트 커패시터를 사용해 기동 시간을 수십 밀리초(ms)로 늘렸으며, 이 구간에서 FET는 발진에 취약해진다.? 15 mF의 출력 커패시턴스는 기동 시 수 암페어의 돌입 전류를 유발해 FET의 gm을 증가시킨다.

-12 Ω 부하는 FET의 gm을 높이기 위한 추가 전류를 제공한다.

그림 7. 단순화한 테스트 회로

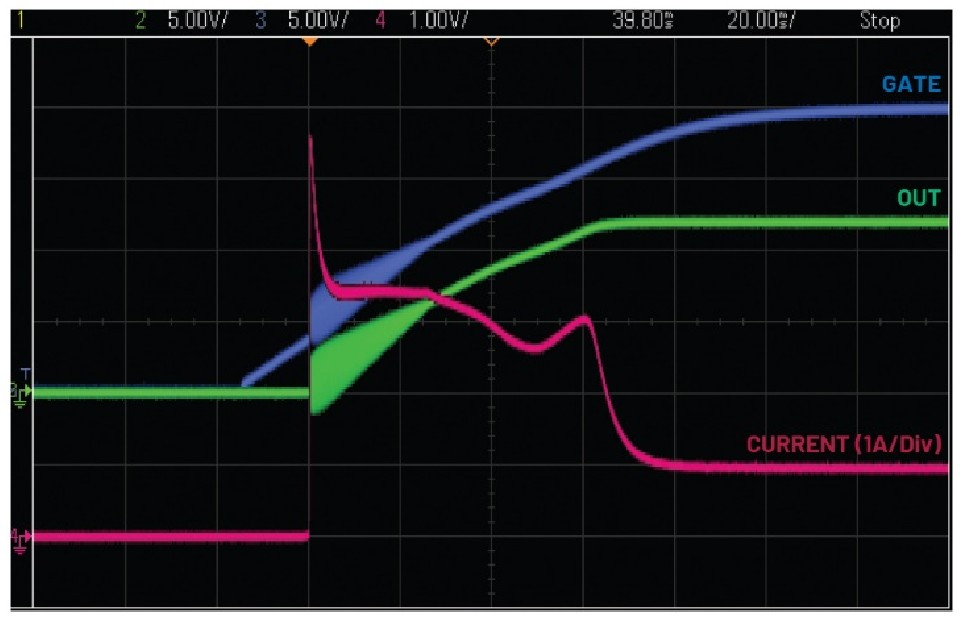

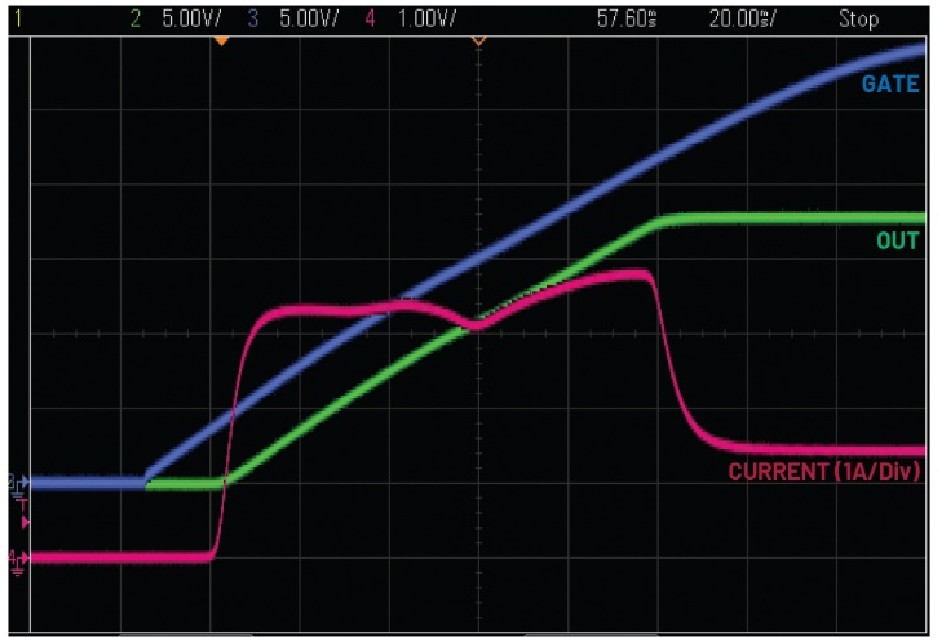

그림 8. 기동 중 점점 감쇠하는 발진을 보여주는 오실로스코프 파형

그림 8의 파형을 보면, 게이트 전압이 FET의 문턱 전압에 도달하는 순간 GATE와 OUT 파형에서 링잉이 발생한다. 이 링잉은 GATE 파형에 갑작스러운 스텝 변화가 생기면서 돌입 전류가 오버슈트되기 때문에 나타난다. 이후 링잉은 점차 감쇠한다.

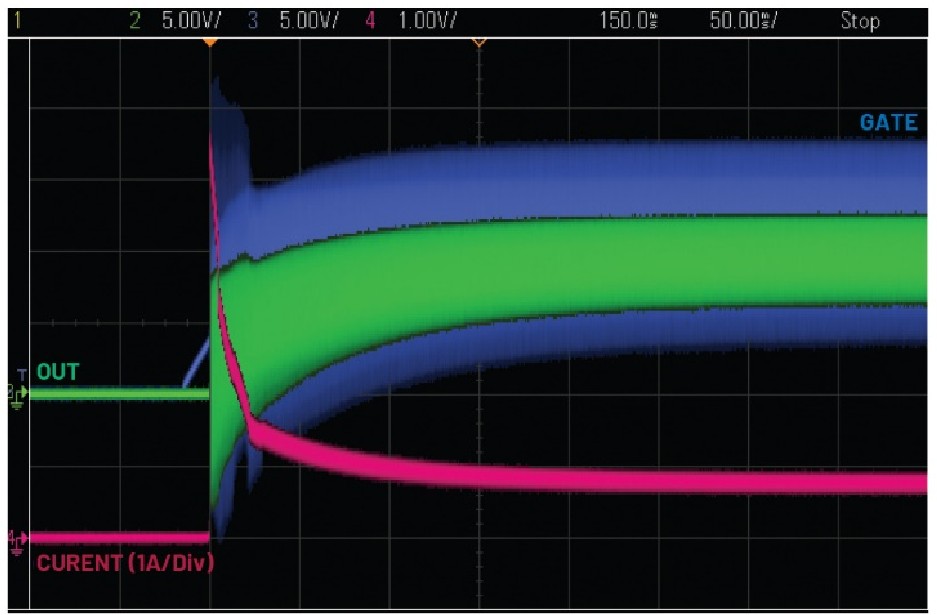

이 과도 링잉을 지속적인 발진으로 발전시키려면 FET의 이득을 더 키워야 한다. VIN을 12V에서 18V로 높이면 부하 전류와 gm이 모두 증가한다. 그 결과, 양의 피드백이 충분히 증폭되어, 그림 9의 오실로스코프 파형에서 보듯이 발진이 유지된다.

그림 9. VIN 증가로 인해 지속적인 발진이 발생하는 모습을 보여주는 오실로스코프 파형

그림 10. 게이트 저항을 추가한 데모 보드 테스트 회로

이제 문제가 재현되었으므로, 잘 알려진 해결책을 적용해 보자. 10Ω 게이트 저항을 인덕터와 직렬로 추가했다(그림 10). 이 저항을 추가하면 발진이 효과적으로 억제되며, 그림 11에서 보듯이 기동 과정이 깔끔하게 이루어진다.

그림 11. 게이트 저항을 추가한 후 발진 없이 기동되는 모습을 보여주는 오실로스코프 파형

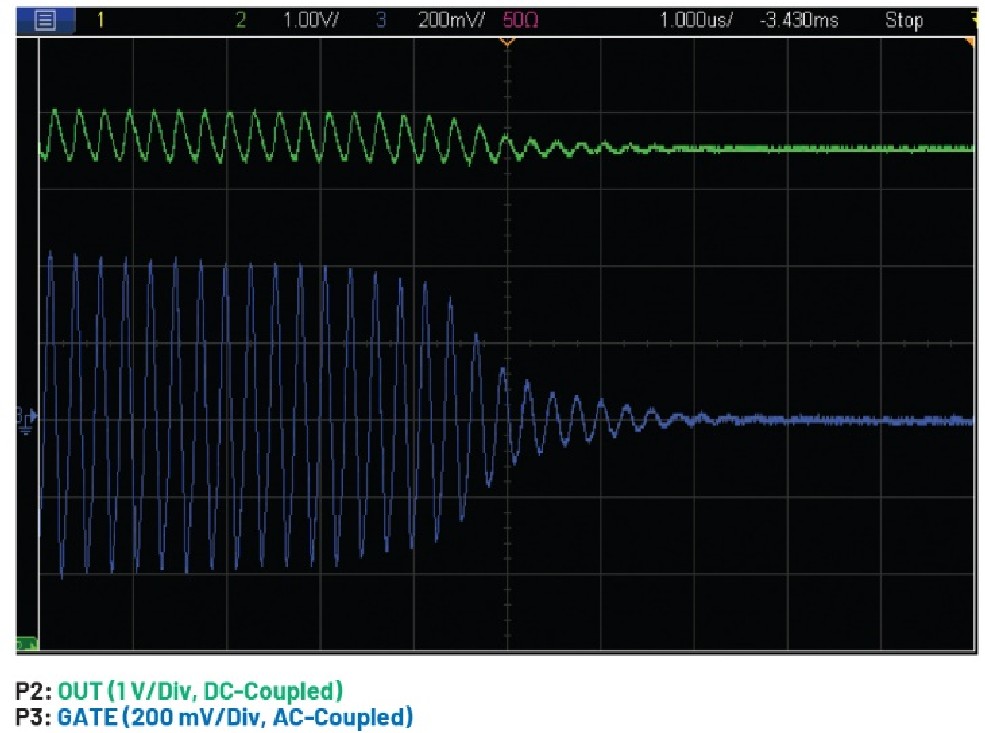

기본 NFET 콜피츠 발진기로 다시 돌아가 보면, 스위칭 가능한 게이트 저항을 추가함으로써 RGATE의 감쇠 효과를 확인할 수 있다(그림 12). 0Ω에서 10Ω으로 전환하면, 그림 13에서 보듯이 발진이 효과적으로 감쇠한다.

그림 12. 스위칭 가능한 RGATE를 추가한 기본 NFET 콜피츠 발진기

그림 13. RGATE 값을 단계적으로 변경함에 따라 발진이 사라지는 모습을 보여주는 오실로스코프 파형

결론

이 글에서는 FET 기생 발진의 이론을 다루고, 벤치 실험을 통해 콜피츠 모델을 검증했으며, 데모 보드 상에 동일한 문제를 재현하여 널리 알려진 해결책으로 이를 해소하는 과정들을 살펴봤다. 10Ω 게이트 저항을 FET의 게이트 핀에 최대한 가깝게 배치하면, PCB 트레이스의 기생 인덕턴스를 FET의 입력 정전용량으로부터 분리할 수 있다. 이를 통해 게이트 링잉이나 발진이 발생할 가능성을 제거할 수 있으며, 1개의 표면실장 저항만으로도 사용자가 몇 시간씩 들여야 하는 트러블슈팅과 보드 재제작 이슈를 피할 수 있다.

저자 소개

아론 샤피로(Aaron Shapiro)는 2019년에 아나로그디바이스(Analog Devices)에 입사해 핫스왑 제품을 담당해 왔다. 그는 캘리포니아 주립대학교 새크라멘토에서 아날로그 전자공학을 전공하며 전기전자공학 학사 학위(B.S.E.E.)를 받았다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>