전형적인 SMPS가 효율 요건을 충족시킬 수 있긴 하지만 낮은 대기 전류 요건을 준수하지는 못한다. 그러므로 하이브리드 전원 공급이 이러한 난제에 대한 해답이 될 수 있다.

자동차 시스템의 영구 전원 파워 서플라이에서 공통적인 난제는 자동차 제조사의 요건과 부합하도록 대기 상태에서 충분히 낮은 입력 전류 요구량을 유지 하면서도 높은 효율과 낮은 입력 전압 컴플라이언스를 유지하며 비용 및 공간요건을 충족시키는 것이다.

이러한 요건을 준수하기 위해 대부분의 자동차 시스템은 선형 레귤레이터와 연결된 낮은 대기 전류 배터리를 이용한다. 이러한 선형 레귤레이터는 각종 필요사항에 부합함에도 부하 전류가 증가하며 부하 공급 전압이 감소하는 특유의 전력 비효율이 채택에 걸림돌이 된다.

출력 전력이 높아지면 그에 비례하여 전력 손실도 증가하므로 시스템 온도가 상승한다. 전력 손실이 증가하면 열계수가 온도 상승으로 이어지는 만곡점에 도달하므로 접합 온도가 절대 최대치와 만나게 된다(그림 1). 이 단계를 넘어서면 신뢰성에 영향을 미칠 수 있으므로 SMPS(Switched Mode Power Supply)가 반드시 필요하게 된다. 전형적인 SMPS가 효율 요건을 충족시킬 수 있긴 하지만 낮은 대기 전류 요건을 준수하지는 못한다. 그러므로 하이브리드 전원 공급이 이러한 난제에 대한 해답이 될 수 있다.

하이브리드 파워 서플라이는 집적 SMPS와 낮은 대기 전류 선형 레귤레이터를 병렬로 결합시켜 개별 접근법의 장점을 취하는 한편, 대부분의 단점을 완화시킨다. 작동 원리는 간단명료하다. 통상 시스템 웨이크 상태에서 고 부하 전류를 지원해야 할 경우, SMPS가 활성화되고 낮은 대기 전류는 해제된다(SMPS 모드).

일반적으로 시스템 슬립 상태에서 낮은 대기 전류가 지원되어야 할 경우, SMPS는 해제되고 낮은 대기 전류 선형 레귤레이터가 활성화된다(LDO 또는 LDO 모드). 이 동작은 부하 전류 레벨을 모니터하는 집적 회로(IC) 내에서 자동으로 실행된다(그림 2).

이 아키텍처의 이점은 높은 출력 전력의 경우 고효율 SMPS가 작동하고 낮은 출력 전력의 경우에 낮은 대기 전류 선형 레귤레이터가 작동한다는 것이다. SMPS모드에서는 통상 90% 이상의 효율을 달성할 수 있으며, 낮은 대기 전류 선형 레귤레이터 모드에서는 최대 39 μA의 대기전류를 달성할 수 있다.

SMPS 모드에서 낮은 대기 전류 LDO모드로 전환하거나 그 반대의 경우 출력 전력에 작은 문제가 생기기도 하지만 출력 커패시턴스에 의해 이 전압의 크기가 억제될 수 있으므로 출력 전압이 허용치 내에서 유지된다(그림 3).

최신 자동차 시스템의 낮은 입력 전압 컴플라이언스를 위해서는 콜드 크랭크(cold-cranking) 또는 점차 보편화되고 있는 스톱-스타트(stop-start) 요건을 충족시키는 것이 중요한 관건이다.

이는 최대 듀티 사이클 제한이 낮은 입력 전압 구동을 제약할 수 있는 SMPS모드에서 특히 중요한 문제다.

일종의 절충안들이 가능한데, 하이사이드 PMOS 스위치를 갖춘 SMPS의 경우 100% 듀티 사이클이 실현될 수 있다. 낮은 입력 전압 구동의 유일한 장애물은 하이 사이드 스위치에 걸친 전압강하 및 IC의 내부 레일 전압 요건이다.

그러나 PMOS 스위치 SMPS는 여러가지 추가 작업을 필요로 한다. RDS(on)가 동일하더라도 NMOS 스위치에 비해 PMOS 스위치의 단위 면적당 사이즈가 더 크고 다이 면적도 넓으므로 가격이 높아지거나 다이 면적이 같아도 RDS(on)가 커지면 하이 사이드 스위치에 걸친 전압 강하 현상 역시 커진다.

NMOS 스위치 SMPS에서 NMOS 스위치 게이트 전압을 소스 전압 이상으로 유지하려면 부트스트랩(최소 3개 이상의 구성요소를 외부적으로 추가하는 것)이 필요하다. 부트스트랩은 커패시터 충전에 의존하여 게이트에 에너지를 전달하는데 해당 부트스트랩 커패시터는 일정한 충전을 위한 최소 시간을 필요로 하므로 최대 듀티 사이클이 제한된다.

이 상황을 개선하기 위해 SMPS의 아키텍처를 조정할 수 있다(특히 고주파 SMPS의 경우). 예를 들어, 스위칭 주파수를 낮은 입력 전압 조건에서 폴드백(fold back)하여 펄스-스킵(pulseskipping)없이 최대 듀티 사이클을 늘릴 수 있다. 또한 일부 자동차 시스템은 입력 전압을 모니터하고 입력 전압이 특정 임계치 이하로 떨어지는(부하 차단이 실행되는) 시점을 탐지하여 부하전류를 줄이기도 한다. 물론 부하 전류가 낮아지면 SMPS 하이 사이드 스위치에 걸친 전압 강하도 낮아진다.

온세미(ONSemiconductor)의 NCV891330은 (500 kHz) 주파수 폴드백을 활용, 최대 듀티 사이클을 확장시킴으로써 낮은 입력 전압 컴플라이언스 를 달성하는 NMOS 하이 사이드 스위치 SMPS를 집적시킨 하이브리드 파워서플라이의 좋은 예이다. IC 입력 핀에서 5.0 V 출력과 0.5 A 부하로 입력 전압 5.34 V를 달성할 수 있다.

하이브리드 파워 서플라이나 선형 레귤레이터를 사용하지 않고 낮은 대기 전류를 달성하는 방법은 이력(hysteretic)모드나 버스트 모드 컨버터와 같이 오프 타임이 가변적인 변조 방식을 갖춘 SMPS를 사용하는 것이다. 경부하 조건에서의 이러한 컨버터는 주로 스위치 오프 타임 연장 이전의 스위치 펄스 ‘버스트’를 활용한다. 이 과정에서 부하는 온전히 방전 출력 커패시터에 의해서만 공급된다. 이 연장된 오프 타임 중에는 게이트 구동 회로와 같은 회로가 해제되며 대기 전류가 최소화될 수 있다.

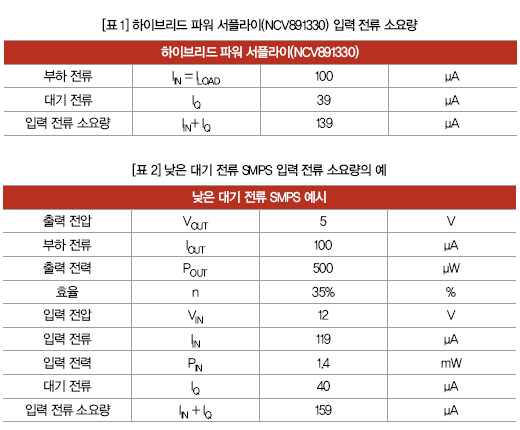

이처럼 낮은 대기 전류 SMPS는 대기전류가 하이브리드 파워 서플라이와 대등하거나 그보다 낮아질 수 있다. 그러나 경부하/대기 전류 여부는 전반적인 입력 전류 요구량이 낮을수록 버스트 모드의 전반적인 효율, 부하 전류, 그리고 대기 전류에 좌우된다. 예를 들어, 12 V 입력, 12 V 출력, 부하 100 μA, 대기 전류 39 μA의 하이브리드 파워 서플라이를 위해서는 선형 139 μA 입력 전류가 요구된다(표 1 참조). 그러나 같은 12 V 입력, 15 V 출력, 부하 100 μA, 대기 전류 40 μA 조건에서 35% 이하로 부하 효율이 낮은 대기 전류 SMPS의 입력 전류 소요량은 하이브리드 파워 서플라이보다 14% 높은 159 μA이다(표 2 참조).

한편, 이력 변조 방식을 사용하면 사이클당 가변 기간에 해당하는 가변 오프 타임(다시 말해 가변 주파수) 현상이 발생한다. 이 주파수는 인덕터 값의 함수인 부하 전류와 듀티 사이클이 되므로 더 이상 직접 제어 가능한 양만큼 되지는 않게 된다. 미지수 기본 주파수는 예측 불가능한 전자기 스펙트럼 반응을 생성하는데, 기본 주파수가 알려지지 않으면 방출을 억제하기가 힘들다.

히스테리시스 및 버스트 모드 토폴로지의 영향은 주파수가 가변적이며 전통적인 펄스 폭 변조(PWM) 기법을 활용하는 SMPS보다 높은 출력으로 출력 리플 전압을 가지고 있다. PWM 제어를 활용하는 하이브리드 파워 서플라이는 출력 전압 리플을 낮추는 장점을 제공한다.

결론적으로 하이브리드 파워 서플라이는 전원을 공급하면서도 낮은 대기 전류를 제공하는 한편, 과부하에서의 높은 효율과 낮은 출력 전압 리플, 예측 가능한 전자기 방출 및 우수한 입력 전압 컴플라이언스를 유지한다. 낮은 대기 전력 선형 레귤레이터는 여전히 경부하에 적합하지만 열역학적으로 혹독한 환경에서 과부하 용도에는 적합하지 않다. 낮은 대기 전력 SMPS는 때로 입력 전류 소요량을 낮춰주지만 대기 전력과 경부하 효율을 임계 분석해야 한다.

온세미의 NCV891330은 하이브리드 SMPS/LDO 파워 서플라이다. 이 소자는 3 A를 수용할 수 있는 2 MHz급 비동기 PWM 컨버터와 50 mA를 수용할 수 있는 최대 대기 전류 39 μA의 선형 레귤레이터를 집적한 것이다. 이에 따라 출력 전압 옵션이 생산 단계에서 정해지고 내부적으로 보상되며 Reset 및 Enable 핀이 함께 제공된다. SOIC-8 EPAD 패키지로 제공되는 NCV891330은 다양한 기능과 패키지 옵션을 갖춘 하이브리드 파워 서플라이 IC 제품군의 일부다.

참/고/문/헌

1. NCV891330 datasheet

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>