'이노베이터3D IC(Innovator3D IC)' 출시, ASIC 및 칩렛의 계획 및 이기종 통합

지멘스 디지털 인더스트리 소프트웨어, 지멘스 EDA 사업부는 세계에서 가장 진보된 최신 반도체 패키징 2.5D 및 3D 기술과 기판을 사용하여 ASIC 및 칩렛의 계획 및 이기종 통합을 위한 빠르고 예측 가능한 경로를 제공하는 소프트웨어인 이노베이터3D IC (Innovator3D IC™)를 발표했다.

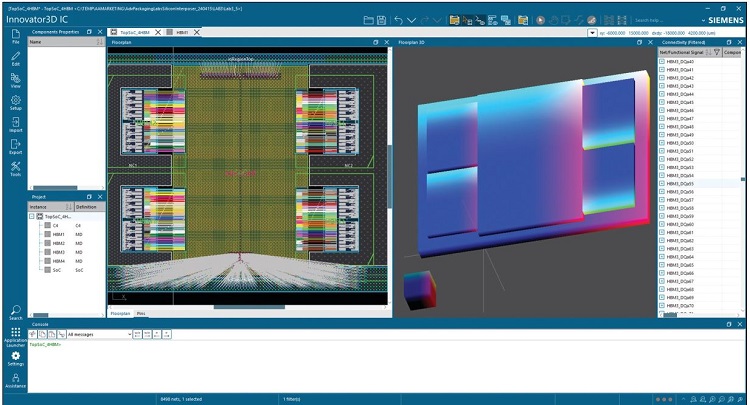

지멘스의 Innovator3D IC는 설계 계획, 프로토타이핑 및 예측 분석을 위한 통합 데이터 모델을 갖춘 전체 반도체 패키지 어셈블리의 디지털 트윈을 구축하기 위한 통합 콕핏(consolidated cockpit)을 제공한다. 이 콕핏은 물리적 설계, 다중 물리 분석, 기구 설계, 테스트, 사인오프, 제조 출시까지 모든 과정을 지원한다.

지멘스의 Innovator3D IC는 전력과 신호, 열, 기계적 응력 분석 도구를 통합함으로써 세부 설계 구현 전에 문제를 식별, 방지, 해결하는 동시에 신속한 '가정(what-if)' 탐색을 가능하게 한다. 이러한 전환적 접근 방식은 비용과 시간이 많이 소요되는 다운스트림 재작업이나 최적이 아닌 결과를 방지할 수 있다.

지멘스 디지털 인더스트리 소프트웨어의 AJ 인코르바이아(AJ Incorvaia)전자 보드 시스템(Electronic Board Systems) 부문 수석 부사장은 "지멘스는 이미 지멘스 엑셀러레이터의 일부로 가장 포괄적인 반도체 패키징 관련 기술 포트폴리오를 보유하고 있었다"라고 말하며, "이러한 기술을 Innovator3D IC와 결합함으로써 고객은 무어(Moore) 이상을 실현할 수 있다"라고 말했다.

Innovator3D IC는 지멘스의 Aprisa™ 소프트웨어 디지털 IC 배치 및 경로 기술, Xpedition™Package Designer 소프트웨어, Calibre® 3DThermal 소프트웨어, 기구 설계용 NX™ 소프트웨어, Tessent™ 테스트 소프트웨어, 인터칩렛 DRC, LVS 및 테이프아웃 사인오프용 Calibre® 3DSTACK 소프트웨어를 사용하여 ASIC, 칩렛 및 인터포저(Interposer) 구현을 지원한다.

Innovator3D IC는 계층적 디바이스 계획 방식을 사용하여 수백만 개의 핀이 포함된 고급 2.5D/3D 통합 설계의 엄청난 복잡성을 처리한다. 설계는 정교함과 구현 방법을 제어하는 속성을 가진 기하학적으로 분할된 영역으로 표현된다. 이를 통해 중요한 업데이트를 신속하게 구현하는 동시에 특정 영역에 분석 기법을 일치시켜 실행 시간이 지나치게 길어지는 것을 방지할 수 있다. 계층적 인터페이스 배선 경로 계획은 칩렛 인터페이스와 핀 할당을 더욱 최적화한다.

Innovator3D IC는 산업용 소프트웨어인 지멘스 엑셀러레이터 포트폴리오와 통합되어 있지만 개방형 아키텍처를 통해 타사 포인트 솔루션과의 통합도 지원한다. Innovator3D IC의 핵심 요소는 3Dblox, LEF/DEF, Oasis 및 인터페이스 IP 프로토콜(예: UCIe 및 BoW)과 같은 산업 표준 형식을 지원한다. ‘Open Compute Projects Chiplet Design Exchange’ 워킹 그룹(OCP CDX)에 적극적으로 참여하여 새로운 상용 칩렛 에코시스템에서 제공할 표준화된 칩렛 모델을 직접 사용할 수 있다.

Innovator3D IC는 2.5D 및 3D 통합에 국한되지 않고 인터포저(유기, 실리콘 또는 유리), ABF 빌드업, RDL 기반의 칩 퍼스트 또는 라스트 등 모든 선도적이고 새로운 반도체 통합 방법론과 플랫폼을 계획하고 프로토타입을 제작할 수 있으며, ‘Deca Technologies’ 회사의 적응형 패터닝 프로세스(adaptive patterning process)에 대한 지원도 포함한다. 또한 패널 레벨 패키징(PLP), 임베디드 또는 레이즈드 실리콘 브리지, 시스템 인 패키지(SiP) 및 모듈에 대한 인증도 받았다.

<저작권자©스마트앤컴퍼니. 무단전재-재배포금지>