정밀 계측을 위해서는 왜곡과 잡음이 극히 낮은 고성능 신호 발생기가 필요하다. 이 용도를 위한 레퍼런스 디자인으로서 ADMX1002는 고성능 정밀 디지털-아날로그 컨버터(DAC)를 채택해서 이전에 볼 수 없던 정확도와 분해능을 달성한다. 또한 참신한 디지털 전치왜곡(DPD) 알고리즘을 적용해서 테스트 신호 충실도를 추가적으로 향상시킴으로써 저렴하면서 크기가 작은 폼팩터로 왜곡이 극히 낮은 신호를 발생한다.

.jpg)

정밀 아날로그-디지털 컨버터(ADC)와 고충실도(Hi-Fi) 오디오 디바이스(코덱, MEMS 마이크로폰 등)가 진화함에 따라 자동화 테스트 장비(ATE)에서 고성능 오디오 및 신호 발생에 대한 요구가 높아지고 있다. 이들 디바이스의 DC와 AC 특성을 분석, 검증, 테스트하기 위해서는 여러 고성능 장비들이 필요하므로 개발 비용과 생산 테스트 비용을 증가시킬 뿐만 아니라, 때로는 테스트 커버리지가 제한적일 수 있다.

이에 대한 대안으로서 테스트 엔지니어들은 가능하다면 자체 솔루션을 개발하고자 한다. 하지만 그러려면 시간과 자원이 든다. 레퍼런스 디자인으로서 ADMX1002 초저 왜곡 신호 발생기 모듈은 바로 이러한 개발 작업을 돕기 위한 것이다.

.jpg)

ADMX1002는 하드웨어와 임베디드 소프트웨어 개발 과제를 모두 해결한다. 간단한 시리얼 인터페이스를 통해 설계 복잡성을 완화하고, 여러 사인파 및 임의 파형 발생을 자동화한 다. 뿐만 아니라 고유한 디지털 전치왜곡 알고리즘을 적용해서 신호 체인에서 DAC와 증폭기 성능을 추가로 향상시킨다.

고성능 혼성신호 테스트 요구

최신 ADC와 그 밖에 다른 혼성신호 디바이스는 높은 수준의 DC 및 AC 특성을 테스트하기 위해서 소스 장비를 필요로 한다. 어떤 경우이든 테스트하고자 하는 대상 디바이스(DUT) 보다 소스의 성능이 높아야 한다.

DC 테스트는 코드 소실이 발생하지 않는지 확인하기 위한 것으로서, 미분 선형성(DNL), 적분 선형성(INL), 오프셋과 이득 오차 등을 테스트한다. INL과 DNL 성능을 테스트하기 위해서는 램프파 같은 저잡음 고분해능 DC 결합 단일 샷 선형 신호가 필요하다. ADC에서 활용할 수 있는 모든 코드들을 활용하기 위해서는 높은 분해능이 필요하다.

AC 테스트는 총 고조파 왜곡(THD), 신호대 잡음 및 왜곡 (SINAD), 스퓨리어스 없는 동적 대역(SFDR) 등의 사양을 테스 트한다. 이들 테스트는 종종 최고 품질의 톤(사인파)을 사용해서 수행된다. 다시 말해 목표 사양 이상으로 어떠한 고조파 성분도 포함하지 않아야 한다는 뜻이다.

그러기 위해서 테스트 엔지니어는 시스템이 복잡해지고 비용이 증가하는 것을 감수 하고서라도 맞춤형 필터를 도입해서 테스트 신호로부터 원치 않는 왜곡 성분을 제거하고자 할 수 있다. 하지만 소스로부터의 광대역 잡음이 원하는 신호 부근에서 필터링을 어렵게 할수 있다. 소스로부터 나오는 이 잡음은 테스트 대상 ADC의 잡음 플로어보다 낮아야 한다. 그래야 원하는 측정 목표에 방해가 되지 않는다.

.jpg)

표 1은 고성능 ADC의 데이터 시트에 표기된 사양을 요약 해서 나타낸 것이다(AD4020/AD4021/AD4022, ADAQ23878, AD7134). 이 표에 따르면 우리가 목표로 하는 THD가 -123dBc보다 우수해야 한다는 것을 알 수 있다.

낮은 왜곡을 달성하기 위한 설계 고려사항:분해능과 선형성

왜곡은 특정 지점에서 신호 진폭의 오차로 정의할 수 있다.

이러한 오차가 발생하면 이상적 신호 형태로부터 벗어나게 된다. 디지털적으로 합성된 신호로는 해당 신호의 모든 샘플을 정확하게 표현하기 위해서 선형성을 최하위 비트(LSB) 수준 으로 보장하는 진정한 고정밀 DAC가 필요하다. INL과 DNL은 컨버터가 이상적인 전달 함수로부터 벗어나는 것을 나타내는 지표이므로, 이러한 선형성 오차는 고충실도 신호를 재현하는 데에 있어서 직접적으로 영향을 미친다.

주기적 신호의 왜곡은 흔히 THD로 표현되므로, 적절한 정밀 DAC를 선택하기 위해서는 분해능과 INL이 THD에 미치는 영향을 수치화해야 한다. 낮은 THD를 달성하기 위해서는 낮은 잡음 플로어가 필요하다. 즉, 높은 신호대 잡음비(SNR)가 필요하다. 기본 적으로 컨버터의 SNR은 양자화 잡음에 따라서 제한된다. 통상적 으로 SNR과 분해능은 다음과 같은 관계식으로 표현할 수 있다.

.jpg)

이 공식에서 N은 컨버터에서 이용할 수 있는 비트 수이고, fs는 샘플링 레이트이며, BW는 측정 대역폭이다 2 . 표 1을 통해 SNR이 최소한 100.5dB보다 우수해야 하고 이보다 3배 더우수하면 이상적이라는 것을 알 수 있다. 이는 약 110dB에 해당한다. 1차 나이퀴스트 영역까지의 대역폭을 고려했을 때 110dB에 필요한 분해능은 18비트이다.

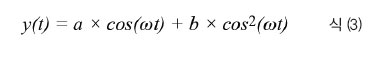

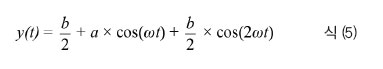

그 다음에는 INL과 THD 사이의 관계를 구한다. 이를 위해서 2차 INL이 약한 DAC라고 가정해보자. 이 전달 함수는 다음과 같은 다항식으로 표현할 수 있다.

.jpg)

이 공식에서 y는 DAC 출력(V)이고, x는 입력 코드이다. 첫째 항의 계수 a는 입력 코드와 출력 전압에 대한 이상적 계수 이다. 둘째 항은 INL을 나타내는 것으로서, 이의 계수 b는 a보다 훨씬 작다. 이 DAC로 코사인 신호 x(t) = cos(ωt)를 발생시 키면 다음과 같은 출력을 얻는다.

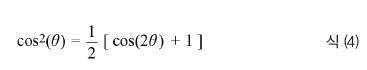

삼각함수 항등식 때문에

DAC 출력에서 신호는 다음과 같이 표현할 수 있다:

이번에는 둘째 항이 2차 고조파 왜곡(HD2)을 나타낸다. 이관계식을 보면 왜곡이 낮은 신호를 발생하기 위해서는 INL이 근본적인 제한 요소라는 것을 알 수 있다. 이 분석은 더 높은 차수 INL 항에도 그대로 적용된다. 이것들은 더 높은 차수의 고조파 왜곡 성분을 발생한다. 예를 들어서 진폭의 3차 비선형성 항 c를 추가하면 다음과 같은 신호를 얻는다.

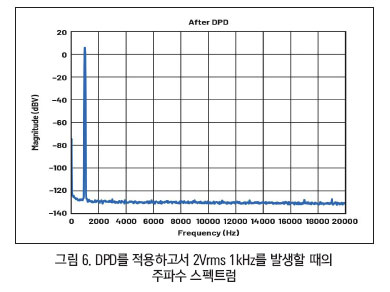

위의 SNR 계산에 따라서 18비트 DAC를 사용하고 3차 INL 이 2 LSB라면 3차 고조파에 의해서 발생하는 왜곡은 다음과 같다.

이것은 설계 목표인 -123dBc에 못 미친다. 2비트를 추가하면 이 왜곡이 12dB 낮아져서 -126dBc가 된다. 그러므로 목표로 하는 왜곡 수준을 달성하려면 분해능이 최소한 20비트인 DAC가 필요하다.

신호 발생 경로 설계

왜곡과 잡음 목표를 충족하는 소스를 설계하는 것은 핵심 부품인 DAC와 이의 전압 레퍼런스 회로에서부터 시작된다.

이 용도로는 AD5791 20비트 정밀 DAC를 사용할 수 있다. 이 DAC는 높은 분해능과 1LSB보다 우수한 선형성을 제공함으로써 10V 출력 범위를 사용했을 때 10μV 미만의 오차로 신호 레벨을 극히 정확하게 재현하도록 한다.

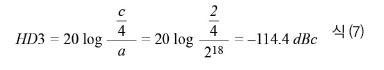

그림 2는 출력 신호 경로 다이어그램을 보여준다. 2개의 AD5791이 반대 극성으로 동작해서 완전 차동 경로를 구현함

으로써 SNR을 추가적으로 높이고 희망 신호를 접지 유도 누화로부터 차단시킨다. 저잡음 전압 레퍼런스로서 LTC6655가 AD8676 정밀 연산 증폭기와 결합해서 각각 AD5791의 고선 형성 바이폴라 동작을 위해서 필요한 양(+) 및 음(-)의 레퍼 런스 레벨을 제공한다.

AD5791은 고정밀 아키텍처이므로 한 가지 과제는 신호를 발생할 때 코드 전이 사이에 글리치 에너지가 발생한다는 것이다 4 . 글리치는 발생하려는 신호의 시간 도메인 특성을 왜곡하고, DUT에 바람직하지 않은 에너지 양이 전달되 도록 한다. 주기적 신호의 경우, 이들 글리치가 주파수 도메 인에 기본 톤과 고조파적으로 상관적인 스퓨리어스 성분을 발생한다.

이에 대한 한 가지 해결책은 글리치 에너지를 필터링하는 것이다. 하지만 이렇게 하면 소스의 신호 대역폭과 안정화 시간을 나쁘게 한다. 더 좋은 방법은, ADG1236과 AD8676 연산 증폭기 같은 전하 주입이 낮은 아날로그 스위 치를 사용해서 샘플-앤-홀드 회로에 기반 한 글리치 억제 회로를 구현하는 것이다 5 .

.jpg)

그림 3은 글리치 억제 회로를 적용하기 전(위)과 후(아래) 의 10kHz 사각파를 보여준다. 하단 트레이스는 AD5791 출력 으로 존재하는 코드 전이 글리치를 보여준다. DAC와 글리치 억제 회로 업데이트 레이트는 1MHz이다. 스위치로부터의 잔류 전하 주입은 발생한 신호에 대해 고조파적으로 상관적이지 않고, 그러므로 출력에서 복원 필터를 사용해서 손쉽게 필터링할 수 있다.

글리치 억제 회로로부터 나온 결과 신호를 출력에 전달하기 앞서 ADA4945-1 완전 차동 증폭기(FDA)에 기반한 다중스 테이지 6차 저역통과 필터를 사용해서 필터링을 한다. 이 고차수 복원 필터가 필요한 것은, 글리치 억제 회로로부터 잔류 에 너지와 1차 나이퀴스트 영역 너머의 이미지들을 제거하기 위한 것이다. 이 성분들이 DUT의 입력 스펙트럼에 다시 에일리 어싱할 수 있다 6 .

ADA4945-1은 차동 출력을 구현해서 최신 ADC의 입력 요구를 충족한다. 또한 각각의 ADA4945-1은 오직 1.8nV/ √Hz 잡음만을 발생하고, 0.5μV/℃의 보장된 오프셋 드리프트로 높은 정밀도를 달성한다.

디지털 전치왜곡

디지털 전치왜곡(DPD)은 신호 경로 상에 부품들이 발생하는 비선형성을 최소화하기 위한 기법이다. DPD를 적용하기 위해서는 교정하고자 하는 오차를 알아야 한다. 그래야 이 오차를 신호에서 뺄 수 있다. 따라서 신호 경로의 측정이 먼저 이루어져야 한다.

신호 경로 오차 측정과 관련한 과제는, 이 측정 경로가 소스 경로보다 왜곡이 낮아야 한다는 것이다. 그렇지 않으면 측정 경로에서 소스로 오차가 추가될 것이기 때문이다. 하지만 우수한 ADC와 증폭기를 사용한다 하더라도 이렇게 하기가 쉽지는 않다. LTC2378-20은 고유 선형성이 업계에서 가장 우수한 20비트 ADC로서, ±2ppm INL을 보장한다. 이는 AD5791 INL의 두 배이다. 그러므로 단지 전달 함수의 다중 지점들을 디지털화하는 것만으로는 소스 경로의 전달 함수 오차를 측정할 수 없다. 더 나은 접근법이 필요하다.

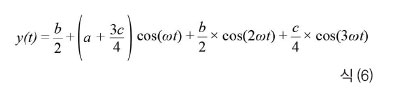

특허 받은 DPD 알고리즘을 통해, ADMX1002는 소스 오차를 교정하기 위해 사용되는 측정 경로의 선형성을 향상한다.

목표는 사인파 왜곡을 낮추는 것이므로 소스가 측정 간격에 단일 주파수 톤을 발생한다. 이 신호에 따라서 ADC 앞의 DPD 검출 경로가 이 경로의 전반적인 선형성을 향상한다.

이 파형의 여러 디지털화 부분들을 사용해서 디지털 도메 인에서 신호를 복원하고 이것을 수학적 모델과 비교한다. 이동작으로부터 교정 파라미터를 구한 다음, 이를 발생하고자 하는 사인파에 적용한다. 이 프로세스를 위해서는 임의적 오차를 제거하기 위해서 여러 번의 반복 작업이 필요하다. 알고 리즘이 교정을 위한 최적의 파라미터들을 구했으면 실행을 멈추고 최종적으로 사용된 파라미터들을 저장한다. 그림 4는 이알고리즘의 플로우 차트를 나타낸다.

.jpg)

이 교정은 발생하고자 하는 신호에 따라서 다르므로, 진폭과 주파수가 다른 신호들마다 이 분석을 실시해야 한다. ATE 시스템에서 다른 파형을 셋업하는 데 걸리는 시간을 줄이기 위해, 이렇게 처리된 파형 데이터를 온보드 플래시 메모리에 저장했다가 나중에 불러낼 수 있다. ADMX1002는 최대 15개의 파형을 저장할 수 있다. 여기에는 듀얼 톤이나 임의적 패턴도 포함된다.

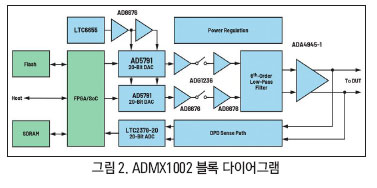

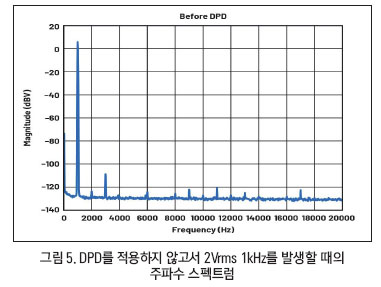

그림 5의 스펙트럼은 이 신호 체인에 DPD를 적용하지 않았을 때 왜곡과 잡음 성능을 보여준다. 그림 6은 이 신호 체 인에 DPD 알고리즘을 적용했을 때로서, 총 THD가 -130dBc 를 넘는다. 이는 DPD를 적용하지 않고서 달성된 -115dBc보다 15dB 향상된 것이다.

DPD 알고리즘 외에도, 진폭 교정 알고리즘은 DPD 검출 경로를 사용해서 복구 필터가 소스 경로에 가중하는 감쇠를 보상한다.

전체 시스템의 프로세싱, 인터페이스, 제어는 SoC가 맡는 다. 이 SoC는 Arm ® 코어 프로세서에 FPGA 패브릭을 포함하 며, 다음과 같은 작업들을 수행한다:

- 파형 합성 - 전치왜곡 알고리즘 실행 - 비휘발성 패턴 메모리 관리 - 글리치 억제 회로의 정밀 타이밍 제어 - 디지털-아날로그 컨버터(DAC)로 데이터 스트리밍 - 아날로그 프런트엔드(AFE) 스위치의 제어 - 전원 레일 제어 및 시퀀싱 - 호스트 인터페이스: SPI, 상태, 병렬 제어

추가적인 DDR3 SDRAM이 데이터 컨버터에 대한 직접 데이터 스트리밍 같은 SoC의 프로세싱 작업을 지원한다.

시스템 전원 공급

이 작업을 다 마쳤으면 하드웨어 설계 엔지니어에게 그 다음으로 어려운 과제가 전체 시스템에 대한 고성능 전원 레일을 구축하는 것이다. 디지털 부품들은 부하 지점(point-ofload, POL)에서 여러 개의 저전압 레일을 필요로 하고, 아날로그 및 혼성신호 디바이스들은 디지털 부품들의 전원 전이로부터 적절히 차단해야 하고 잡음이 낮은 전원 레일을 사용해야 한다. 이 작업을 간소화하기 위해서 ADMX1002는 LDO 레귤 레이터와 전원 감시기(power supervisor)로 이루어진 포괄적인 전원 서브시스템을 포함한다.

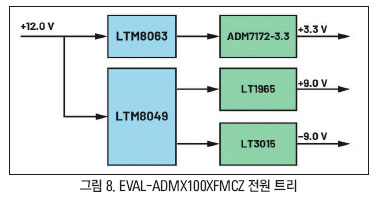

LDO 레귤레이터들이 전단의 스위치 모드 전원장치(SMPS) 로부터 원치 않는 리플을 제거하고 민감한 아날로그 회로로 스퓨리어가 유입되지 않도록 한다. 이러한 스퓨리어스는 출력 스펙트럼에 영향을 미칠 수 있다. 또한 이 SoC의 핵심 전원 레일들은 LTC2962에 의해 감시되는데, LTC2962가 전원 양호 신호를 발생하면 호스트 시스템이 이것을 폴링해서 진단을 한다. 전체적으로 ADMX1002는 호스트로부터 단지 3개의 벌크 전원 레일만을 필요로 한다(+3.3V, +9.0V, -9.0V). 그림 7은 개략적인 전원 트리를 보여준다.

.jpg)

컴퓨터 기반 테스트 시스템에서 일반적으로 사용되는 +12V 전원 레일 같은 양의 레일로부터 저잡음 ?9.0V 레일을 발생하는 것은 외부 자기 소자나 복잡한 레이아웃을 사용할 필요 없이 LTM8049를 사용해서 간단하게 할 수 있다. 마찬 가지로, +12V를 +3.3V로 스텝다운하는 것도 LTM8063을 사용해서 할 수 있다. ADM7172-3.3, LT1965, LT3015 같은 추가적인 LDO 레귤레이터들은 빽빽하게 탑재된 ADMX1002로 리플 전류가 흐르지 않도록 함으로써 깨끗한 출력 스펙트럼을 유지한다.

그림 8의 블록 다이어그램은 이 구성을 보여준 다. 이 구성은 EVAL-ADMX1002FMCZ 평가 보드에서 사용 하고 있는 것이다.

맺음말

이 글에서는 신중하게 설계된 신호 경로와 신호 프로세싱 기법을 사용해서 ADC와 오디오 테스트 요구를 충족하는 것을 설명했다. 이 목표를 달성하기 위해서는 고분해능 DAC를 사용하고, 출력에 글리치가 유입되지 않도록 하고, 왜곡이 낮은 증폭기를 사용해서 복원 필터를 구현해야 한다. 혼성신호 알고리즘을 사용해서 최적화된 디지털 피드백 경로를 구현함으 로써 신호를 정확하게 복원하도록 한다. 또한 전치왜곡 알고 리즘을 적용해서 고조파 왜곡 정보를 도출하고 소스 경로 왜곡을 보상한다.

참고문헌

1. Patrick Butler. “An Almost Pure DDS Sine Wave Tone Generator.” Analog Devices, Inc., December 2019.

2. Walt Kester. “MT-001 Tutorial: Taking the Mystery Out of the Infamous Formula, “SNR = 6.02 N + 1.76 dB,” and Why You Should Care.” Analog Devices, Inc., 2009.

3. Behzad Razavi. RF Microelectronics, Second Edition.

September 2011.

4. Miguel Usach and Martina Mincica. “AN-1444 Application Note: Second-Order Effects to Consider for Continuous Precision DAC Updates.” Analog Devices, Inc., January 2017.

5. “MT-090 Tutorial: Sample-and-Hold Amplifiers.”

Analog Devices, Inc., 2009.

6. “Why Does a DDS Need a Reconstruction Filter?”

Analog Devices, Inc.Brandon, David and Ken Gentile.

“AN-837: DDS-Based Clock Jitter Performance vs.

DAC Reconstruction Filter Performance.” Analog Devices, Inc., December 2006.

Kester, Walt. “MT-003 Tutorial: Understand SINAD, ENOB, SNR, THD, THD + N, and SFDR so You Don’t Get Lost in the Noise Floor.” Analog Devices, Inc., 2009.

Kester, Walt. “MT-017 Tutorial: Oversampling Interpolating DACs.” Analog Devices, Inc., 2009.

저자 소개

구스타보 카스트로(Gustavo Castro)는 아나로그디바이스 (매사추세츠주 윌밍턴)의 계측기 사업부 시스템 아키텍트이 다. 2011년에 아나로그디바이스에 입사했으며, 그 전에는 내쇼날 인스트루먼트(National Instruments)에서 10년 간재직하면서 자동화 테스트 장비용 고성능 디지털 멀티미터와 정밀 소스 측정 유닛 설계를 담당했다. 정밀 측정 및 전자 계측용 아날로그, 혼성신호, 알고리즘 설계와 관련한 다수의 특허에 참여했다. 몬테레이 공과대학에서 전자 시스템 학사 학위와 노스이스턴 대학에서 마이크로시스템 및 소재공학 석사학위를 취득했다.

[문의: gustavo.castro@analog.com]

<저작권자©스마트앤컴퍼니. 무단전재-재배포금지>