글 | Michel Azarian, Linear Technology

본고에서는 RF 리시버의 한 부분으로써, 325 MHz IF 샘플링 시스템을 구축하고 30 MHz 이상 대역폭, 64 dB의 뛰어난 SNR, 80 dB의 SFDR을 달성하는 레퍼런스 클록 분배 디자인에 대해 알아본다.

서론

클록 지터는 레퍼런스 클록 버퍼링 및 분배 시에 RF 리시버로 유발되어, 달성 가능한 시스템 성능을 제한할 수 있다. 또한 프론트엔드 필터 요구량을 완화하고자 하는 의도에서 비교적 높은 IF(intermediate frequency)를 이용할 시에 낮은 지터의 요구가 더욱 더 높아진다. 본고는 325 MHz IF 샘플링 시스템에 대한 설명과 사인파 레퍼런스 신호를 고속 ADC를 구동하기에 적합한 한 쌍의 차동 LVPECL 클록으로 변환하고, 변환 후에 유발되는 지터를 최소화하는 클록 버퍼 및 분배기를 소개한다.

시스템

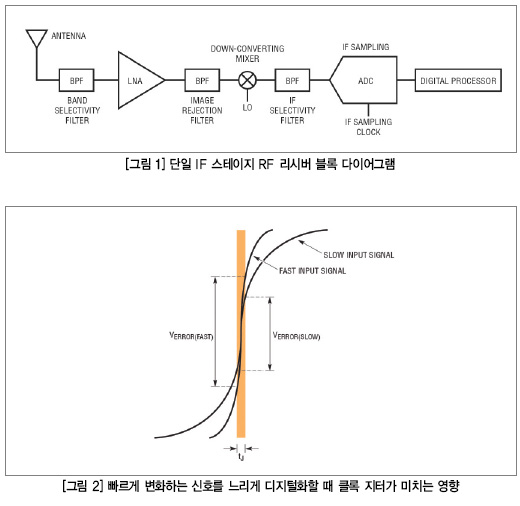

IF 샘플링(다시 말해서 언더샘플링) 시스템은 ADC가 RF 리시버에서 최종으로 변환 스테이지를 수행하는 것으로써, IF가 높을수록 RF 프론트엔드의 이미지 제거 필터 요구량을 완화할 수 있다. 따라서 필터 비용과 크기, 삽입 손실을 낮출 수 있으며, 이는 다시 증폭 필요성을 줄일 수 있도록 해 비용과 전력 소모를 더 낮출 수 있다. 그림 1은 IF 샘플링을 채택한 RF 리시버 체인의 예를 보여주고 있다.

리시버를 비교적 높은 IF를 이용하도록 설계할 때의 단점은, 고주파 아날로그 입력 신호를 샘플링할 때 ADC 성능이 저하되어 시스템 성능이 악화될 수 있다는 것이다. 예를 들면 입력 주파수가 높아질수록 ADC의 SFDR(spurious free dynamic range)이 나빠진다. 또한 더욱 중요한 점은 더 빠른 입력일수록 ADC의 애퍼처 지터와 클록 지터가 결합하여 달성 가능한 SNR(signal-to-noise ratio)에 영향을 미치게 된다. 동일한 ADC와 클록을 이용하면 기울기가 더 높은 2개의 변화하는 신호를 샘플링하면서 클록 지터로 전압 오차 크기를 비교해 클록 지터가 미치는 영향을 알 수 있다. 그림 2에서 보듯이 이 클록은 2개 신호를 샘플링할 때 동일한 시간 지터이다(tJ, s-RMS 단위). 빠르게 변화하는 신호일수록 클록 지터로 인해 유발되는 불확실성의 정도가 높아진다는 것을 알 수 있으며, 이에 클록 지터가 아날로그 입력에 고주파 성분이 포함될 때 SNR을 제한하는 가장 지배적인 오차 요인이 아니더라도 주요한 오차 요인이라는 것을 알 수 있다. 그러므로 그림 1은 IF 샘플링 클록으로 표기하고 있는 것으로 ADC 클록의 지터를 되도록이면 낮추도록 해야 한다. ADC 클록 입력에서 AM-대-PM 잡음 변환을 방지하기 위해서는 클록이 이상적인 사각파로써 슬루율이 높아야 한다. 또한 신호를 취하고 입력 신호의 제로 크로싱(또는 여타 레퍼런스) 시에 판단해서 스퀘어링할 때 ADC의 클록 입력이 리미터 역할을 한다. 들어오는 신호가 저주파나 진폭 사인파 같이 슬루율이 느릴 때 AM-대-PM 잡음 변환이 발생한다. 예를 들어 저항 열 잡음이나 전원장치로부터의 결합 잡음 등과 같이 어떠한 형태의 AM 잡음이 있으면, 들어오는 신호의 제로 크로싱이 이후 에지들에서 불일치하게 됨으로써, 리미터 출력에서 지터를 발생시킨다. 그럼으로써 AM 잡음이 PM 잡음으로 변환된다. 반면에 LVPECL 신호가 빠른 상승 및 하강 시간으로 인해 통상적으로 들어오는 신호가 빠르게 제로 크로싱을 통과하면 클록으로 첨가된 AM 잡음이 PM 잡음으로 변환될 가능성이 아예 없거나 매우 적어진다.

뿐만 아니라 대다수 최신 ADC는 최대의 성능을 달성하기 위해서 클록 입력을 차동으로 구동해야 한다. 클록 신호는 PCB 상에서 통상적으로 상당한 거리에 걸쳐서 배선된다. 클록 소스와 대상이 대개 서로 가깝게 있지 않기 때문이다. 클록 신호를 차동으로 구동하면 클록 신호가 결합에 내구성을 갖도록 할 수 있고 single-ended 클록 배선에 비해 전반적으로 더 견고한 설계를 달성할 수 있다.

그림 1에서 보는 LO 신호는 통상적으로 PLL(phase-locked loop) 시스템을 이용해서 발생시킨다. PLL은 LO를 동기화하기 위해서 레퍼런스 클록을 필요로 한다. 전통적으로 10 MHz가 주된 레퍼런스 주파수로 이용되어 왔다. 하지만 최근에는 훨씬 더 높은 주파수의 레퍼런스 클록들이 갈수록 더 널리 이용되고 있다. 실제로 첨단 RF 디자인에서는 100 MHz 이상의 주파수가 드물지 않게 이용되고 있다.

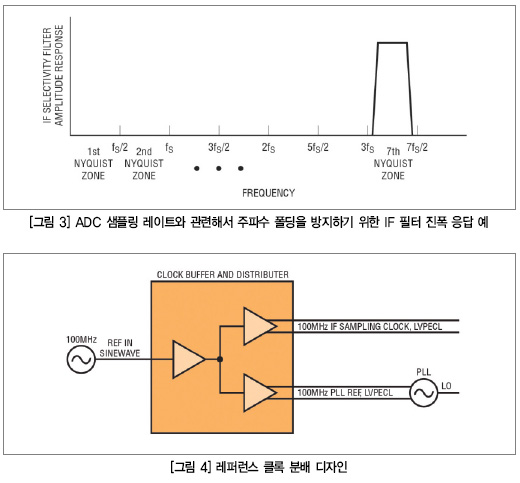

레퍼런스 클록은 보통 OCXO나 TCXO 소자를 이용해서 발생시킨다. 이들 소자는 일반적으로 지터(위상 잡음)가 매우 낮다. PLL 레퍼런스 클록의 주파수를 수신 RF 채널 대역폭(2개 이상 인접 채널을 동시에 디지털화하는 리시버에서는 다중 채널의 대역폭)의 2배보다 상당히 높도록 선택하면 적절한 주파수 플래닝에 의거해 동일한 레퍼런스 신호를 이용해서 IF 샘플링 ADC를 클로킹할 수 있다. 이상적으로는 주파수 폴딩을 방지하기 위해 IF 선택도 필터의 통과대역 및 상당 부분의 전이 구역(transition zone)이 ADC의 단일 나이퀴스트 구역 안에 들어가도록 해야 한다. 이 점은 그림 3에서 보여주고 있는 IF 필터 진폭 응답을 보면 확실해진다. 여기서는 IF를 ADC의 7차 나이퀴스트 구역과 일치하도록 선택하고 있다. 그림 3에서 fS는 ADC의 샘플링 레이트이다. 이 경우 그림 1의 LO를 믹서의 하향 변환 신호 출력 중심이 그림 3에서 보여주고 있는 IF 선택도 필터의 가운데에 오도록 선택할 수 있다.

그림 4는 레퍼런스 주파수가 100 MHz라고 했을 때 위에서 설명하고 있는 클록 분배 디자인을 요약하여 보여주고 있다. 그림 4의 클록 버퍼 및 분배기는 OCXO 또는 TCXO 디바이스로부터 single-ended 사인파를 받아서 ADC 및 PLL로 루팅하기에 적합한 2개의 차동 LVPECL 신호를 제공해 매우 중요한 역할을 하고 있다. 이렇게 하면서 분배되는 클록으로 최소한의 지터만이 추가하도록 해야 한다. 리니어 테크놀로지의 LTC6957-1은 첨가 지터가 낮은 듀얼 LVPECL 출력 클록 버퍼로서, 바로 이 같은 애플리케이션에 이용하기에 적합하며, 위에서 논의하는 모든 요구사항을 충족한다. 또한 LTC6957의 다른 제품 버전을 이용하면 다른 출력 형식들을 달성할 수 있다. LTC6957-2는 LVDS 출력이고, LTC6957-3과 LTC6957-4는 CMOS 출력을 제공한다.

회로 구현

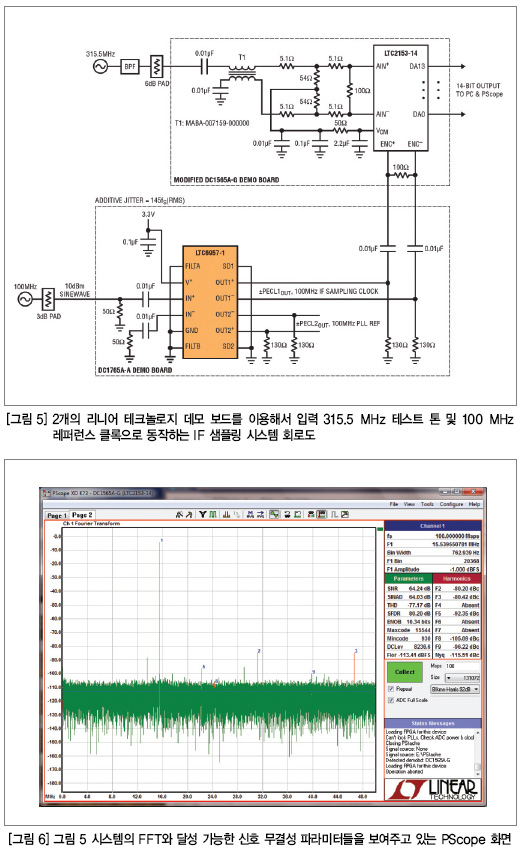

위에서 살펴보았듯이 지터는 IF를 높이고자 할 때 주된 제한 요소이다. 일반적인 ADC에 클록 분배기로서 LTC6957-1을 이용하면 어떠한 성능을 달성할 수 있는지 2개의 리니어 테크놀로지 데모 회로를 그림 5에서와 같이 수정해 연결했다.

LTC2153-14는 310 Msps 14비트 ADC로서 높은 아날로그 입력 주파수를 이용하기에 적합하도록 설계해 이 애플리케이션의 IF 샘플링 ADC로 이용하기에 알맞다. 이 데모 회로인 DC1565A-G를 그림 5와 같이 수정했다.

DC1765A-A 데모 회로는 LTC69571을 기반으로 이를 이용하면 100 MHz OCXO의 사인파 출력을 버퍼링할 수 있다. DC1765A-A 차동 LVPECL 출력 쌍 중의 하나는 DC1565A-G의 차동 인코드 클록 입력으로 연결한다. 또 다른 쌍은 그림 1에서 PLL을 발생시키는 LO의 레퍼런스 입력으로 이용할 수 있다.

ADC를 100 MHz로 클로킹하면 에일리어싱을 방지하면서 이론적으로 달성 가능한 가장 높은 대역폭이 50 MHz이다. 그림 3에서처럼 7차 나이퀴스트 구역을 선택하면 이 50 MHz의 이상적 대역폭으로 300 MHz ~ 350 MHz 주파수 범위를 처리할 수 있다는 뜻이다. 그러기 위해서는 300 MHz ~ 350 MHz 범위에 존재하는 IF 정보만을 통과시키면서 원하는 대역으로 에일리어싱과 간섭을 일으킬 수 있는 나머지 모든 것을 제거하도록 50 MHz의 통과대역으로 325 MHz를 중심으로 이상적인 brick-wall 통과대역 필터를 필요하다.

중심 주파수 허용오차와 더불어 실제적인 필터는 필터 통과대역과 대역 제거 구역 사이의 비-무한소(non infinitesimal) 전이 구역 때문에 이 경우에 좀 더 타당한 IF 대역폭 선택은 약 325 MHz를 중심으로 최대 30 MHz 대역폭의 SAW(surface acoustic wave) 필터 같은 것이 될 것이다. 이 주파수 범위의 SAW 필터들이 시장에 속속 등장하고 있다.

성능 요약

ADC가 경험하는 진폭을 -1 dBFS로 다이얼링하기 위해 IF 선택도 필터와 감쇠기를 모사하는 BPF를 통해 수정된 DC1565A-G의 아날로그 입력으로 315.5 MHz 테스트 톤을 연결했다.

DC1565A-G를 USB를 통해 PC로 연결했다. PC에서는 PScope1 데이터 수집 제어 소프트웨어를 이용하여 리시버의 품질에 영향을 미치는 2개의 주요 파라미터인 SNR와 SFDR을 살펴볼 수 있다. 그림 6은 PScope™의 실행과 ADC 아날로그 입력의 315.5 MHz -1 dBFS 톤, ADC 인코드 클록이 LTC6957-1을 이용해 100 MHz LVPECL 신호 버퍼링 시, 131072-포인트 FFT와 일부 분석을 보여주고 있다.

그림 6에서 볼 수 있듯이 달성된 SNR과 SFDR은 각각 64 dB, 80 dB 이상이다. 이것은 325 MHz IF 샘플러로서 매우 뛰어난 수치이다.

LTC6957-1의 입력은 50 Ω으로 +10 dBm 전력의 100 MHz 사인파이므로 LTC6957 데이터 시트의 권고에 따라 입력이 진폭이나 주파수가 낮을 때 첨가되는 지터를 낮추기 위한 것으로써, 내부적인 대역폭 제한 필터(FILTA와 FILTB)를 둘 다 턴오프하고 있다.

결론

RF 리시버의 한 부분으로서 325 MHz IF 샘플링 시스템을 구축하고 평가해봤다. 낮은 지터 클록 버퍼 및 분배기 제품인 LTC6957-1을 이용해서 ADC 샘플링 클록 및 PLL 레퍼런스로 이용하도록 LVPECL 형식으로 100 MHz 시스템 레퍼런스 클록을 분배했다. 또한 SNR 및 SFDR 수치를 살펴봄으로써, IF 샘플링 시스템의 성능을 측정했다. 이 시스템을 이용하면 64 dB의 뛰어난 SNR 및 80 dB의 SFDR을 달성함으로써, 비교적 높은 IF 샘플링을 가능해 RF 이미지 제거 필터 요구량을 완화할 수 있도록 한다.

비고 1. PScope는 시간 및 주파수 영역으로 ADC로부터 데이터를 수집 및 분석하고 해당 파라미터들을 표시하는 프로그램이다.

(www.linear.com에서 다운로드 가능)

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>