TSV 기술을 적용한 I/O의 경우, 핀당 24 μW 정도의 전력을 소모한다 [1]. 이러한 전력 소모의 감소는 512개의 I/O를 가진 차세대 소자를 구현할 때, 칩 개발자들에게 1000배에 가까운 공간적인 여유를 제공한다.

글 | 토어스텐 마티아스(Thorsten Matthias), 유르겐 부르크그라프(Jurgen Burggraf),

다니엘 버그스탈러(Daniel Burgstaller), 마커스 윔플린저(Markus Wimplinger),

폴 린더(Paul Lindner)

EV Group

Wide I/O 인터페이스 memory-on-logic 소자는 여러 응용분야에 적용할 수 있는 잠재력을 가지고 있으며, 실리콘 관통전극(Through Silicon Via, TSV)과 3D 통합 기술에 의해 급속한 기술 발전을 이루게 됐고 실제 양산 라인에 적용할 수 있게 됐다. 정보 전송 방법이 텍스트 중심의 통신에서 사진 및 비디오 중심의 통신으로 빠르게 전환됐고, 이는 기존의 대역폭으로는 정보 전달을 할 수 없는 상황을 초래하게 되었다. 스마트폰과 미디어 서버의 융합으로 인해 12 GB/s 이상의 DRAM 대역폭이 요구되고 있고, 이는 1080p HD 해상도의 비디오를 대면적의 디스플레이에 표시할 수 있게 했다. 일반적인 memory-logic interfaces (“narrow I/O interface”라고 함)에서는 다수의 입출력(I/O)을 가지고 있기 때문에 많은 전력 소모가 발생하게 되어 I/O 수를 수백 개에서 수천 개까지 증가시키기에는 한계가 있었다. TSV 기술은 I/O에서 상당한 전력을 절감할 수 있다. 기존의 DDR3 DRAM 기술은 핀당 40 mW 정도의 전력을 소모하지만, TSV 기술을 적용한 I/O의 경우, 핀당 24 μW 정도의 전력을 소모한다[1]. 이러한 전력 소모의 감소는 512개의 I/O를 가진 차세대 소자를 구현할 때, 칩 개발자들에게 1000배에 가까운 공간적인 여유를 제공한다.

다음의 이유로 인해 Wide I/O memory-on-logic 소자는 현재 가장 도전적인 3D 응용분야 중 하나다:

- 모바일 분야가 매우 빠르게 성장하면서 폼팩터가 매우 중요하다.

- 현재 각각의 메모리 층은 50 μm 이하의 두께를 요구한다.

- 메모리 분야에서 대역폭 및 전력 소모도 중요한 요소 중 하나지만, 전체적인 데이터 저장 용량 역시 중요한 요소이다.

TSV 통합

이와 같은 이유로, 여러 개의 메모리 다이를 적층해야 할 필요성이 대두되었다. 처음에는 4중 적층 구조에서 갈수록 8중 이상의 적층이 필요하게 되었다. TSV 기술을 이용한 칩 적층 기술로 인해, Wide I/O DRAM은 처음에는 4개의 메모리 다이와 1개의 로직 컨트롤러의 적층이 필요하게 됐다. EVG는 이미 memory-on-logic 업체에 장비를 공급할 수 있는 시설을 갖추었고, 최근에 Wide I/O DRAM 업체에 장비를 공급함으로서 이를 입증했다. 현재 시장에서 성공의 열쇠는 TSV 제조 기술로 전환하는 것이다. 과거에는 상상으로만 가능했던 “one solution fits all”이라는 접근법이 이상적인 TSV 제조 공정 기술의 발전으로 인해 전력 소자, 이미지 센서, 적층형 메모리, GPU-on-CPUs 등의 분야에 활용될 수 있게 됐다. 그러나 Wide I/O memory-on-logic 소자 제조에서는 특화된 TSV 제조 공정이 필요하다.

신뢰성 있는 3D 적층 구조는 계속 개발 중이며, 소자 생산에 필요한 시스템 공학 원리도 다방면에서 동시에 고려돼야 하는 요소이다. 과거의 엔지니어들은 이상적인 전/후 RDL 공정 개발을 추진했다. 그러나 TSV를 제작할 때 여러 가지 융합 기술에 대한 문제를 제기하고 있다. 어쨌든 후면 RDL과 TSV 제조 융합 기술의 성공을 위한 방법에 대해 변화가 요구된다. 그래서 현재 memory-on-logic 소자를 위한 다양한 통합 구조가 논의되고 있다.

다른 중요한 요소인 대역폭 및 전력 소모와 전체 저장 용량에 대한 부분과 마찬가지로 비용 또한 아주 중요한 요소이다. TSV 제조비용은 비아 패턴의 깊이 및 형상 비(aspect ratio)와 관련이 있다. 비아 형성에 필요한 공정 반복 주기는 비아 패턴의 형상 비와 깊이, 식각 공정, 충진 방법과 상관이 있다. 메모리 소자에서, TSV 면적을 감소시키면 웨이퍼 내 소자의 단위 면적을 줄일 수 있어서 웨이퍼 소모를 줄일 수 있다. TSV의 형상 비를 줄이고 면적을 줄일 수 있는 방법은 비아의 깊이를 줄일 수 있어야 한다. 그리고 TSV 기술을 이용한 메모리 소자의 적층은 초박막 양면 웨이퍼 사용을 요구한다.

박막 웨이퍼 처리

후면 RDL, TSV, 다이 적층 공정의 융합을 위해서는 박막 웨이퍼 공정이 반드시 필요하다. 소자 웨이퍼와 캐리어 웨이퍼(carrier wafer)의 임시 접합 방법은 박막 웨이퍼를 제조할 수 있고 양면 공정을 가능하게 한다 [2]. 후면 공정 이후 박막 소자 웨이퍼는 캐리어 웨이퍼로부터 분리된다. 박막 웨이퍼를 적층할 때 하나의 주요 요구사항은 다음과 같다:

(a) 웨이퍼에 먼지(이물질) 및 잔여물이 남지 않아야 한다.

(b) 박막 웨이퍼의 표면 화학 및 물리학 결합, 특히 언더필 공정과 호환되어야 한다.

Memory-on-logic 소자는 적어도 5중(인터포저 제외) 또는 6중 다이 레벨(인터포저 포함)로 제작돼야 하므로 박막 웨이퍼의 양면은 이물질 및 잔여물이 남지 않아야 한다. 열가소성 접착제는 분리 공정 후 단일 웨이퍼 세정을 할 수 있다는 장점이 있고, 소자 웨이퍼의 보호막이 변질되지 않는다는 장점이 있다.

로직 컨트롤러 하부 메모리 소자 적층 구조는 일반적으로 칩투칩(chip-to-chip, C2C) 또는 메모리 다이와 로직 다이가 적층된 칩투웨이퍼(chip-to-wafer, C2W) 방법에 의해 구현되며, 이는 반드시 같은 크기를 가지고 있지는 않다. 메모리 다이의 적층(즉, 메모리 “하부 적층”의 조립)은 C2C, C2W 또는 웨이퍼-투-웨이퍼 (W2W) 방법에 의해 구현할 수 있다. 모든 다이의 크기가 같은 메모리 적층은 W2W 기술에 잘 부합하며 볼륨을 높이고 수율을 향상시킬 수 있다.

박막 웨이퍼가 캐리어 웨이퍼로부터 분리된 상태이거나 또는 박막 소자 웨이퍼가 캐리어 웨이퍼에 접합되어 있는 상태에서도 박막 웨이퍼 적층은 가능하다. 캐리어 웨이퍼와 박막 소자 웨이퍼를 접착하는 기술을 이용하면 쉽고 안전한 웨이퍼 반송이 가능하지만, 웨이퍼 접착 공정에 약간의 복잡성이 추가된다. 초박막 웨이퍼의 경우 분리 공정 전에 적층이 필요할 수 있다. C2W 구조에서는 다이 절단 공정을 위해 다이가 캐리어 웨이퍼 위에 있어야 하고, 이는 불필요한 전체 공정비용 상승을 야기한다. W2W 기술은 캐리어 웨이퍼의 재사용을 가능하게 한다.

메모리 소자의 적층을 위해서는 Cu-Cu 접착 공정 기술이 요구된다. 현재 업체들의 목표는 접착 공정 온도를 낮추는 것이고, 이는 주기 시간 및 소유 비용을 줄이기 위한 목적이며 캐리어 웨이퍼로부터 소자 웨이퍼를 분리 공정하기 이전에 영구적으로 Cu-Cu 결합을 촉진하기 위해서다.

박막 웨이퍼 공정은 주로 외주에 의해 수행되는 반면, 다이 적층은 일반적으로 OSAT에 의해 수행된다. 두 경우 모두 박막 웨이퍼를 선적할 필요가 있다. 필름 프레임에 박막 웨이퍼를 붙여서 선적해야 하고, 그럼에도 50 μm 두께 이하의 초박막 웨이퍼의 선적은 수율 향상에 영향을 미친다. 제조 공정의 관점에서 소자 웨이퍼의 가치(비용)는 증가하게 되고(전면 및 후면 처리 완료된 소자), 이로 인해 수율 비용은 무시할 수 없게 된다.

다른 방법은 소자 웨이퍼를 여전히 캐리어 웨이퍼에 접착한 상태에서 선적하고, 조립 사이트에서 직접 분리하는 방법을 추천하고 있다. 이것은 파운드리 업체에서 일시적인 웨이퍼 접착 공정을 하고, OSAT에서는 분리 공정하는 혁신적인 공급망이 필요하다. 이러한 공급망은 웨이퍼의 접착과 분리 공정이 가능한 장비 및 공정기술의 발전에 의해 가능하다.

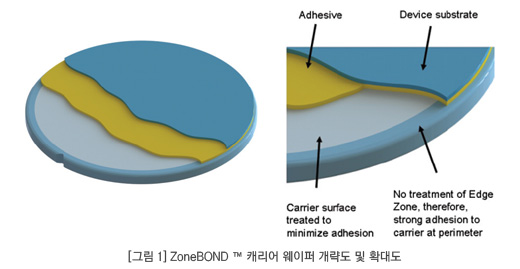

앞서 언급한 바와 같이, 새로운 TSV 제조 공정은 특히 전원 소자 또는 Wide I/O DRAM 제품을 위해 설계되었고 일반적으로 서로 다른 최적의 접착제를 사용할 필요가 있다. LowTemp짋 ZoneBOND™ 분리 공정기술은 혁신적이고 표준화할 수 있다 [2]. 이 기술은 분리 공정 캐리어 웨이퍼 기능이 필요하며 사용된 접착제에 따른 독립적인 분리 공정기술을 가능하게 한다. 그림 1에서 ZoneBOND 캐리어 웨이퍼 형태를 보여준다. 그림과 같이 웨이퍼의 가장자리 영역은 전체적인 접착력을 제공하는 반면, 중앙에는 접착력이 작은 영역이 된다.

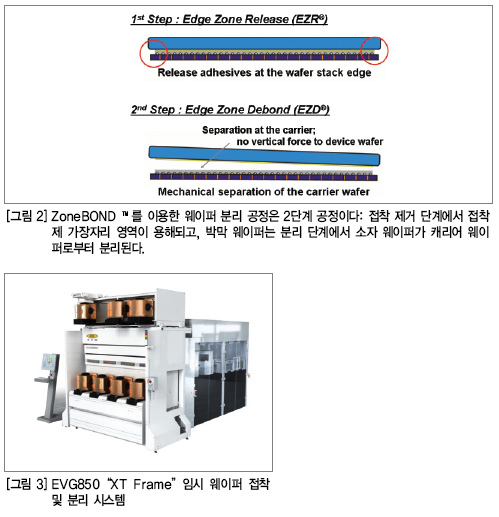

그림 2는 웨이퍼 분리 공정을 나타낸다. 첫째, 웨이퍼 가장자리 영역 제거(Edge Zone Release, EZR짋) 과정을 통해 가장자리 부분의 접착제가 단일 웨이퍼 모드에서 용해된다. 그리고 나면 소자 웨이퍼는 가장자리 분리(Edge Zone Debond, EZD짋) 과정을 통해 캐리어 웨이퍼로부터 분리된다. 그리고 박막 소자 웨이퍼는 필름 프레임부에 고정되고, 동시에 절단 및 어셈블리 공정이 가능해진다. 물리적 분리 공정은 캐리어 웨이퍼 접착 필름 사이의 경계면에서 발생한다. 이러한 물리적인 분리 공정 중에 범프는 안전하게 접착 필름에 붙어 있게 된다. 분리공정 중에는 범프에 무리한 힘은 가해지지 않는다. 이는 접착제 공급업체의 다양한 ZoneBond 재료 공급망을 통해 개방형 플랫폼이 가능해진다.

일시적인 접착 및 분리 공정은 10여 년 전에 화합물 반도체 생산을 위해 소개됐다. 하지만 메모리 생산을 위한 준비를 위해 장비에 큰 변화가 필요하게 됐다. 새로운 임시 접착 및 분리 공정 시스템인 EVG850 “XT Frame”은 대용량 메모리 제조에 최적화돼 있다.

Wide I/O DRAM의 대량생산 준비에는 일반적인 방식과 특히 박막 웨이퍼 처리 TSV 기술이 있어서 대량생산 제조를 가능하게 하는 원동력이 됐다. 박막 웨이퍼 처리는 LowTemp ZoneBOND 장비 및 프로세스의 표준화를 통해 가능하게 됐다. 접착제를 위한 개방형 플랫폼은 여러 접착제 공급업체와의 다양한 공급망을 통해 가능하게 됐다. 새로운 세대의 장비는 모듈 수준, 높은 처리량, 최적화된 웨이퍼 카세트 물류에 대한 통합된 첨단 공정제어를 제공한다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>