- 2013-05-23

- 김창수 기자, cskim@elec4.co.kr

글 | 카이 고스너(Kai Gossner), 필드 애플리케이션 엔지니어(FAE), 텍사스 인스트루먼트

단일 리셋이 가능한 인티그레이터를 이용해 PGA를 구현하는 방법을 설명한다. 여기에는 경제적이며 간편한 설계, 디지털 방식으로 이득 제어 및 보정 등의 이점이 있다.

일부 애플리케이션의 경우, 다이내믹 레인지(dynamic range)가 높은 신호는 디지털화해야 한다. 일반적인 디지털화 방법은 아날로그-디지털 컨버터(ADC) 앞에 외부 PGA(Programmable Gain Amplifier, 프로그램 가능한 이득 증폭기)를 추가하는 것이다. 내장형 PGA를 장착한 마이크로컨트롤러는 소수에 불과하다. 오늘날 PGA는 하나 이상의 입력 채널을 가진 단일 칩에서 사용할 수 있다. 이러한 PGA는 시스템에 추가적인 비용을 요구할 뿐만 아니라, 일반적으로 고정 이득(fixed-gain) 솔루션보다 많은 전력을 소모한다.

이 글은 단일 리셋이 가능한 인티그레이터(integrator)를 이용해 PGA를 구현하는 방법을 설명한다. 여기에는 다음과 같은 이점이 있다.

- 경제적이며 간편한 설계

- 디지털 방식으로 이득 제어 및 보정

- 저역 필터(low-pass filter)로 신호 노이즈 감소. 특히 노이즈가 심한 마이크로컨트롤러 환경과 작은 아날로그 신호에 유용하다. 차단(cutoff) 주파수는 선정된 샘플 레이트에 적합하게 자동 조정된다.

- 0 레벨 기준 전압을 외부에서 제어할 수 있어 일반적으로 0 레벨이 VREF/2로 설정되는 단일 전원 공급 회로를 간편하게 설계한다.

기본 회로

기본 회로

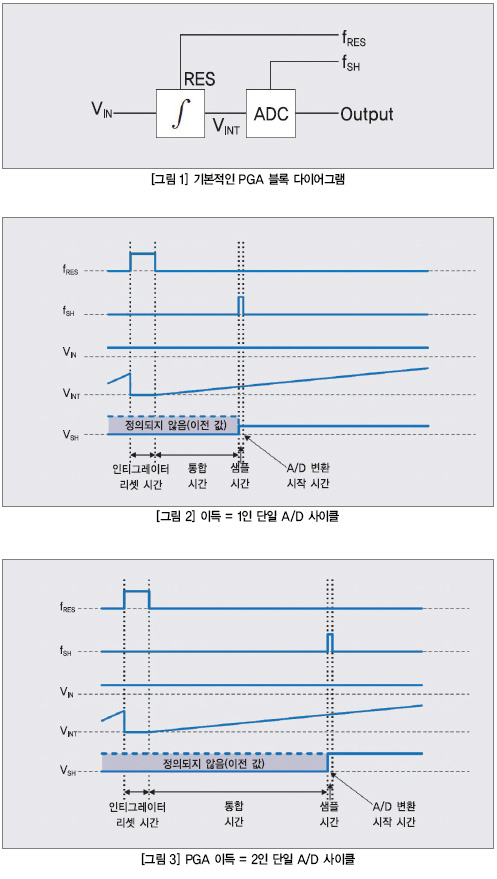

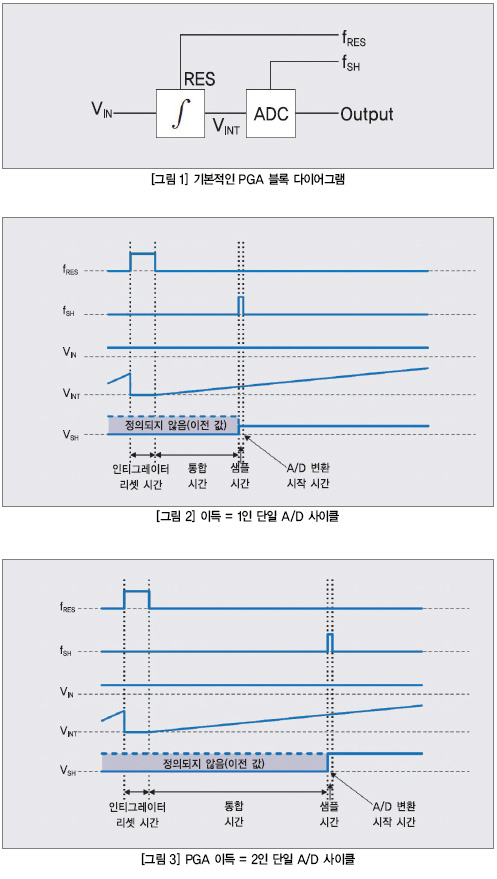

그림 1은 인티그레이터가 ADC 앞에 추가돼 있는 기본 회로이다. 인티그레이터는 신호 fRES(1 = 인티그레이터가 리셋 된다)로 리셋 할 수 있다. ADC는 신호 fSH로 제어되며, ADC의 SH(Sample-and-Hold) 유닛과 연결된다(1 = sample, 0 = hold). 아날로그-디지털 변환 주기는 하강 에지에서 시작된다.

그림 2는 그림 1의 회로가 있는 단일 아날로그-디지털(A/D) 변환 주기를 나타낸 것이다. 주기는 4개의 주기로 구분된다.

1. 인티그레이터 리셋 시간: 인티그레이터를 “0”으로 리셋 한다.

2. 통합 시간: 인티그레이터 리셋 신호가 방출되고 인티그레이터가 통합을 시작한다.

3. 샘플 시간: ADC의 샘플 및 홀드 유닛이 인티그레이터 출력, VINT의 샘플을 추출한다.

4. A/D 변환 시간: 샘플 및 홀드 유닛이 전압을 유지하고 ADC가 변환을 시작한다.

입력에 관한 전압이 기울기에 선형으로 영향을 미치기 때문에 통합 시간의 길이에 따라 PGA 이득이 정해진다. 통합 시간을 2배로 하면 이득도 2배가 된다. 그림 3은 이러한 영향을 보여주고 있다. 통합 시간이 2배로 연장되고 전압 VSH 역시 두 가지 요인 중 하나의 요인으로 인해 2배 증가했다.

이러한 통합 기법이 우수한 점은 입력 신호가 통합 시간 동안 평균적으로 유지된다는 것이다. 이는 입력 신호 VIN의 아웃오브밴드(out-of-band) 노이즈를 줄여준다. 필터의 임펄스 응답은 유한 구간이고, 이는 표준 저역 필터보다는 디지털 FIR 필터의 활동과 유사하다.

PGA의 실제 구성

PGA의 실제 구성

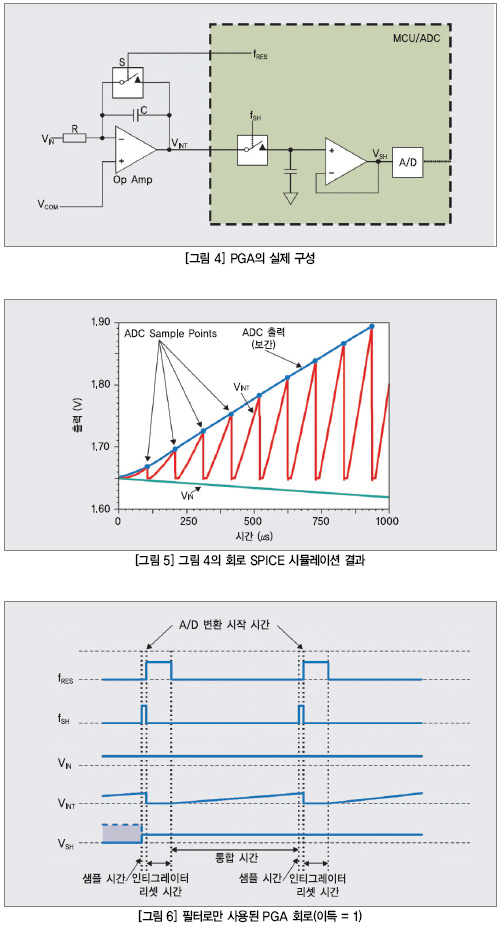

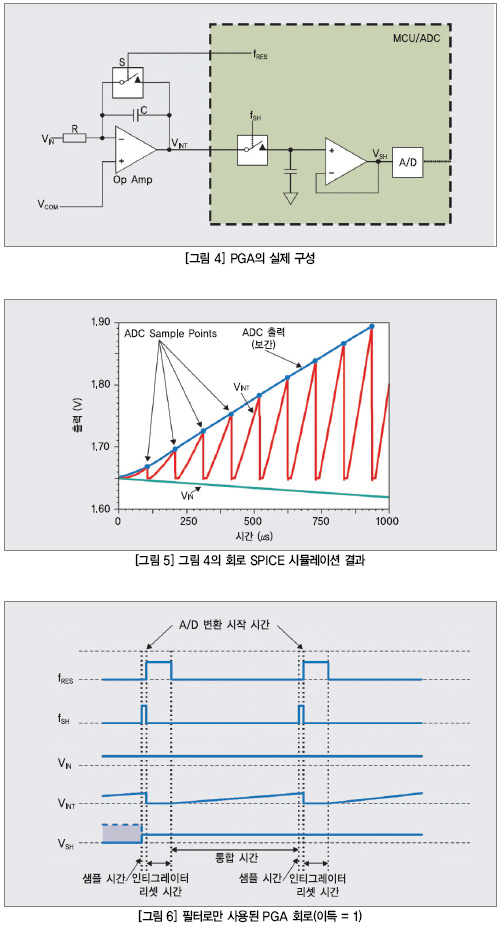

인버팅 증폭기는 단일 연산 증폭기로 구성할 수 있다(그림 4). 스위치 소자 S로 커패시터 C를 단락시키면 인티그레이터는 리셋 된다. 부품 R과 C는 인티그레이터의 이득에 영향을 미친다.

신호 VCOM은 인티그레이터의 0 레벨 전압을 규정하고 VREF/2로 설정될 수 있다. 여기서 VREF는 ADC의 기준 전압이다. 인티그레이터는 커패시터가 방전되면 이 전압으로 리셋 된다. 보통 VCOM 신호는 시스템 내에 존재하고 있다. 종종 이는 단일 공급 아날로그 신호 체인을 위한 가상 접지나 바이어스 전압으로 사용되기도 한다.

그림 5는 그림 4의 회로를 SPICE 시뮬레이션 한 결과이다. 파란색 점은 ADC의 샘플 모멘트를 나타낸다. 보이는 바와 같이 신호 VIN은 -8 정도의 요인에 의해 증폭된다. 빨간색 신호는 인티그레이터의 인버팅 때문에 녹색으로 반전된다.

작동 원리

최대 목표 이득과 샘플 레이트, A/D 변환 시간은 부품 R과 C에 의해 규정된 통합 상수 선별에 영향을 미친다. 그림 2와 3에 제시돼 있는 바와 같이, 인티그레이터가 통합 시간 t 이내에 이득 G에 도달하기 위해서는 충분한 시간이 필요하다. G와 t의 의존성은 다음과 같이 계산된다.

스위치(S)의 종료 시간(인티그레이터 리셋 시간)은 스위치의 임피던스와 커패시터(C)의 값에 좌우된다.

보정

R과 C의 허용오차로 인해 이득 계수가 조정된다. 커패시터는 선형 통합을 수행할 수 있도록 피에조 효과(piezo effect)가 작아야 할 것이다. 커패시터는 특히 허용오차가 20% 정도로 클 수도 있다. 이는 초기 허용오차일 뿐이며, 이는 한 차례 보정할 수 있다. 노후화의 영향으로 인한 허용오차는 연간 1% 미만으로 매우 작다.

이득과 오프셋은 알려진 전압을 입력에 적용하고, 예상 값과 실제 값을 근거로 오프셋과 이득의 보정 값을 계산하는 표준 ADC와 동일한 방법으로 보정을 할 수 있다. 보정은 애플리케이션에 이용되는 각각의 이득 계수마다 실시할 수 있다.

회로 변형

PAC를 저역 통과 필터로만 이용하기(이득 = 1)

입력 신호 증폭을 원하지 않는 경우에는 PGA 회로를 노이즈 필터로만 이용할 수 있다. 인티그레이터 상수는 고정 이득이 1이 되는 값으로 설정할 수 있다. 이러한 경우에는 인티그레이션 페이즈가 표본 추출 이후에 곧바로 시작될 수 있으며, 홀드 단계는 홀드 모드로 설정할 수 있다(그림 6).

비 인버팅 통합

그림 4의 회로는 인버팅 인티그레이터를 사용한다. 반전이 허용되지 않을 때는 단일 전원 공급 인버팅 버퍼를 인티그레이터 앞에 추가해 비 인버팅 인티그레이터를 사용할 수도 있다.

결론

이 글은 비용과 전원에 민감한 애플리케이션에 경제적이고 간단하게 PGA 기능을 구현하는 방법을 제시했다. 주로 ADC 앞에 위치한 외부 필터가 필요하지 않다는 필터링 특성으로 인해 비용을 낮출 수 있다. 그럼에도, 이 방법은 모든 PGA를 대체할 수는 있는 것은 아니다. 예를 들어 샘플 레이트가 높거나 이득 변화가 큰 경우에는 이러한 솔루션을 실현하기 어렵다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>