임베디드 비휘발성 메모리(eNVM) 지적자산(IP) 기업인 킬로패스 테크놀로지(Kilopass Technology)가 7 nm 공정의 DRAM 개발을 앞당기는 혁신적인 VLT(Vertical Layered Thyristor) 기술을 공개했다.

임베디드 비휘발성 메모리(eNVM) 지적자산(IP) 기업인 킬로패스 테크놀로지(Kilopass Technology)가 7 nm 공정의 DRAM 개발을 앞당기는 혁신적인 VLT(Vertical Layered Thyristor) 기술을 공개했다.

미국 산호세에 본사를 둔 킬로패스 테크놀로지(이하 킬로패스)는 2001년 설립 이후 OTP(one- time programmable) 솔루션을 위한 안티퓨즈(Antifuse) 특허 기술로 반도체 시장서 꾸준히 성장해 왔다. 지금까지 킬로패스는 모바일, 소비가전, 아날로그/혼합신호, 산업, 자동차, IoT를 비롯한 광범위한 애플리케이션과 SoC 설계 및 시장에서 eNVM으로 큰 성공을 거뒀다. 특히 삼성, SK하이닉스, SMIC, UMC 등의 기업들이 400여개 이상의 DRAM 설계에 킬로패스 기술을 채택해 왔다.

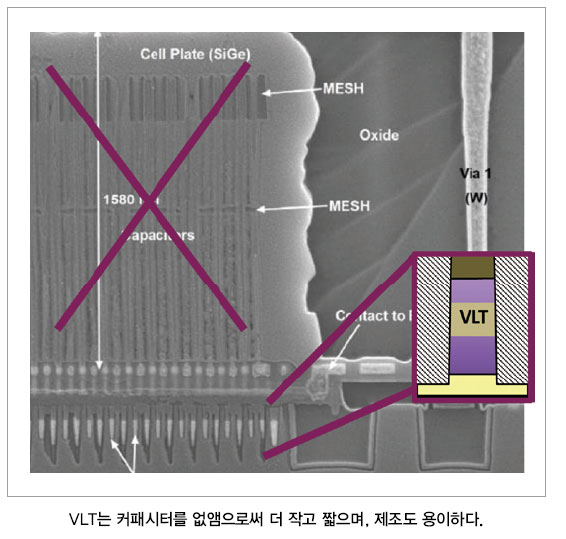

VLT 기술을 공개한 킬로패스의 찰리 쳉(Charlie Cheng) CEO는 “시스템 반도체의 경우 2017년이면 7 nm 공정까지 도달하며 빠른 속도로 발전하고 있는데 비해 DRAM 기술은 커패시터의 용량으로 미세공전 전환이 답보상태이거나 느린 편”이라며 “킬로패스가 공개한 VLT 기술은 커패시터가 필요 없기 때문에 7 nm 공정도 가능하다”고 말했다.

500억 달러 규모의 DDR 메모리 시장은 3,500억 달러 규모에 달하는 전체 반도체 시장에서 가장 큰 비중을 차지하는 분야 중 하나이나 지금 갈림길에서 있다. 프로세서와 기타 SoC, 그리고 NAND 플래시 메모리 제품을 생산하는 로직 파운드리 기업들은 10 nm 이하 공정 노드까지 앞서 가고 있는데 반해, 커패시터 기반 DRAM 기술은 그보다 크게는 2세대 정도까지 뒤쳐진 상태다.

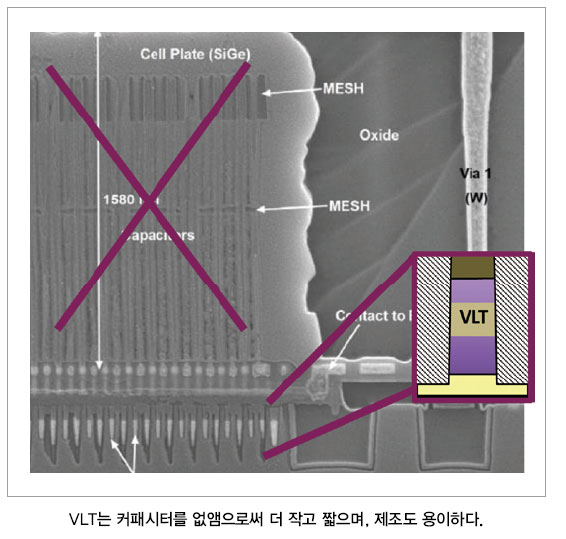

그 이유는 커패시터 스토리지 때문인데, DRAM이 동작하는 동안 전하를 유지할 수 있을 만큼 충분한 정전용량을 지원하면서, 동시에 커패시터의 크기를 줄일 수는 없기 때문이다. 게다가 셀 트랜지스터의 규모가 작아지면 누설전류가 증가하는데, 이는 다시 메모리 콘텐츠를 유지하고 읽는데 더 큰 정전용량 값을 필요로 한다. 하지만 VLT 기술은 DRAM 스토리지 커패시터가 필요없어, DRAM 로드맵의 진척을 가속화할 수 있는 솔루션을 제공한다.

추가 장비 없이 CMOS 기반 기술과 바로 호환

찰리 쳉 CEO는 VLT 기술을 공개하며 이를 통해 향후 이러한 DRAM 시장의 판도를 바꿔 나갈 계획임을 밝혔다.

VLT 비트셀(Bitcell)은 2015년에 검증을 마쳤으며, 메모리 매크로 테스트 칩은 현재 테스트 초기 단계에 있다. 킬로패스는 자사 고유의 초고속 TCAD 시뮬레이터를 이용해 실제 반도체 측정과 동일한 경향을 보여주는 결과들로써 제조가능성을 철저히 검증했다. 현재 킬로패스는 DRAM 제조회사들과 사업제휴 및 라이선스 논의를 활발하게 진행중이다.

찰리 쳉 CEO는 “킬로패스의 VLT 기술은 진정한 게임 체인저(Game Changer)로서, 라이선스 고객들이 자신들의 로드맵 진척을 가로막는 주요 걸림돌을 제거할 수 있는 새로운 DRAM 아키텍처로 나아갈 수 있게 해준다. 또한 VLT는 공간 효율적이고 제조공정이 훨씬 간단해 비용절감은 물론이고 전력소비를 대폭 줄일 수 있으며 성능을 더욱 높일 수 있다”며 “경쟁이 치열한 DRAM 시장의 판도를 바꿀 수 있는 그야말로 혁신적인 기술이다”고 강조했다.

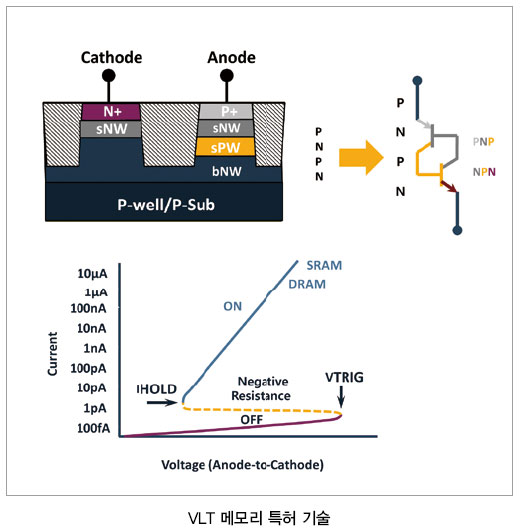

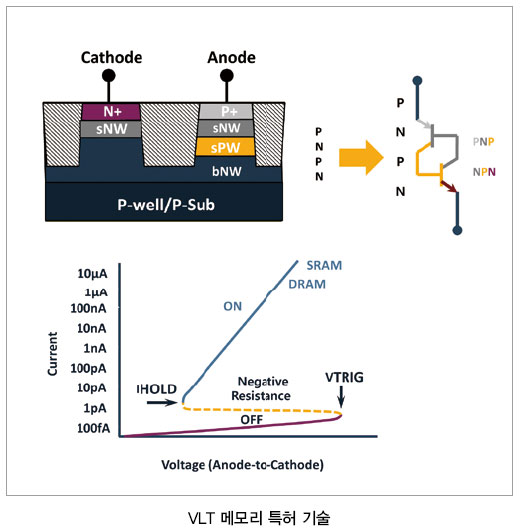

킬로패스의 VLT 기술은 래치를 형성하는 바이폴라 트랜지스터의 교차결합쌍(Cross- coupled Pair)과 전기적으로 대등한 복잡한 구조인 사이리스터(Thyristor) 기술을 기반으로 한다. 이 구조는 값을 저장하기 때문에 메모리 애플리케이션에 적합한데, 현재의 커패시터 기반 DRAM 기술과 달리 리프레시(Refresh)를 요구하지 않는 것이 특징이다. 사이리스터는 1950년대에 처음 개발된 이후 SRAM 시장에서 이를 활용해 보려는 시도가 몇 차례 있었지만 성공을 거두지는 못했다.

VLT는 4.5F2의 고밀도 셀 구조를 위해 사이리스터 구조를 보조 소자와 같이 수직으로 구현한 것을 기반으로 DRAM 비트셀을 실현한 것이다. 즉 반도체의 P- N 접합 구조를 P- N- P- N으로 구성했다. 이로써 제조방식이 간소화되고 크로스포인트 메모리처럼 동작할 수 있게 됐다. VLT는 복잡한 커패시터를 없앴기 때문에 7 nm까지 곧바로 확장이 가능하다.

그 결과 동일한 공정 기술로 제조할 경우, 비용을 45%까지 낮출 수 있는 DDR 호환 기술을 확보할 수 있다. 또한 VLT는 복잡하고 전력을 소비하는 리프레시 동작이 필요 없기 때문에 VLT 기반의 DDR4 DRAM은 대기모드 전력소비를 10배 더 적은 50 fA/bit로 줄일 수 있으며, 성능은 15%까지 높일 수 있다.

찰리 쳉 CEO는 “VLT 기술의 최대 강점은 기존의 공정 장비를 그대로 유지하면서 활용할 수 있다는 점”이라며 “CMOS 기반 기술과 호환이 되므로, VLT를 도입하더라도 기존 공정 장비와 소재, 플로를 그대로 사용할 수 있도록 설계됐기 때문에 별도의 추가 장비를 구입할 필요가 없다”고 말했다.

이어 그는 “스마트폰 시장의 정체로 킬로패스 VLT 기술의 타깃 시장은 DRAM이 반드시 필요한 클라우드, 서버 시장이 될 것”이라며 “이들 시장은 딥러닝, 빅데이터, 인공지능 등의 발달로 향후 DRAM 수요 증가가 예상된다”고 말했다.

VLT 비트셀 동작 및 실리콘 측정은 2015년에 완료했으며, 완전한 매크로 레벨 테스트 칩은 5월에 테이프아웃을 마쳤다. 현재 1차 칩(실리콘) 테스트를 진행 중이다. 한편 킬로패스는 모든 제조 코너에 대해 자사의 혁신적인 TCAD시뮬레이터를 사용해 20 nm, 31 nm 공정기술 노드를 철저히 시뮬레이션 하고 10 nm 노드에서의 실행 가능성을 입증했다. 10 nm 솔루션에 대한 전체 평가는 2017년으로 예정돼 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>