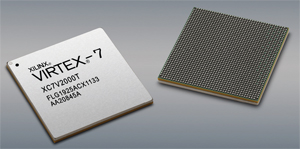

자일링스가 시스템 통합, ASIC 대체 및 ASIC 프로토타입과 에뮬레이션을 위해 68억 개의 트랜지스터를 사용하고, 전례 없는 2천만 개의 ASIC 게이트에 상응하는 2백만 로직 셀에 대한 액세스를 제공하는 세계에서 가장 큰 용량의 프로그래머블 로직 디바이스인 최초의, 2.5차원 스택 실리콘 인터커넥트 기술을 사용한 ‘버텍스-7 2000T’ FPGA를 발표했다.

자일링스의 ‘버텍스-7 2000T’ FPGA 제품은 스택 실리콘 인터커넥트(SSI, Stacked Silicon Interconnect) 기술을 채택한 첫 번째 양산 제품이며, 대만 TSMC의 28나노 HPL 프로세스를 사용하여 발표한 세 번째 FPGA이다.

자일링스의 ‘버텍스-7 2000T’ FPGA 제품은 스택 실리콘 인터커넥트(SSI, Stacked Silicon Interconnect) 기술을 채택한 첫 번째 양산 제품이며, 대만 TSMC의 28나노 HPL 프로세스를 사용하여 발표한 세 번째 FPGA이다.

이 디바이스는 최초의 2.5D(차원) IC 스태킹 애플리케이션 된 제품으로 사용자는 대용량 ASIC 대신 버텍스-7 2000T FPGA를 이용해 1/3에 해당하는 시간에 전반적으로 비슷한 수준의 총 비용을 사용하고, I/O 인터커넥트를 제거하여 시스템 대역은 늘리고 전력 소모는 줄일 수 있는 통합 시스템을 생성하며, 최신 ASIC 시스템의 프로토타입과 에뮬레이션을 가속할 수 있다.

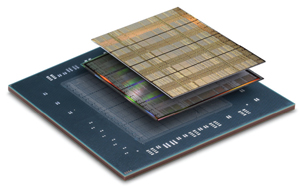

스택 실리콘 인터커넥트 아키텍처는 하나의 실리콘 인터포저(interposer) 상에 여러 개의 다이스를 연결하는 처리 기술이다. 4개의 다이스를 한데 묶어 실리콘 인터포저 위에 얹은 구조를 갖고 있는 버텍스-7 2000T 디바이스는 2백만 개의 로직 셀로 이루어져 있고 2천만 개의 ASIC 게이트에 상응하는 68억 개의 트랜지스터로 구성되어 있다.

이 스택 실리콘 인터커넥트 아키텍처로 만들어진 디바이스는 동일한 28나노 처리 구조의 모놀리식 방식으로는 제공할 수 없었던 ASIC 대체 능력, 더 큰 시스템 집적도 및 ASIC 프로토타입을 전달하면서 경쟁사 대비 두 배의 용량을 제공한다.

역사적으로 FPGA 제품군을 구성하는 대용량 디바이스를 사용하는 것은 거의 불가능했다. 새로운 반도체 공정에서 대용량 디바이스를 효율적으로 사용 가능하도록 웨이퍼 당 수율을 개선하는 데 많은 시간이 걸리기 때문이다.

자일링스의 스택 실리콘 인터커넥트 기술은 패시브 실리콘 인터포저 위에 연결된 4개의 분리형 FPGA 다이로 세계에서 가장 큰 용량의 프로그래머블 로직 디바이스를 제작함으로써 결함이 없는 양산, 대용량 일체식 다이 양산의 문제점을 해결했다.

빈센트 통 자일링스의 품질 및 신제품 출시 담당 수석 부사장은 “버텍스-7 2000T FPGA는 자일링스의 혁신과 업계 협력의 새로운 역사를 쓰고 있다”며, “고객에게 중요한 것은 스택 실리콘 인터커넥트 기술이 최소한 다른 공정의 FPGA에서 불가능한 트랜지스터 용량을 제공한다는 것”이라고 말했다.

그는 이어 “ASIC을 포기하면서 기존 디자인에 새로운 기능들을 즉시 추가할 수 있으며, 차세대 제품을 위하여 최소한 1년 더 앞서 최대 FPGA를 사용하는 시스템 에뮬레이터 구축 및 프로토타이핑 하거나 3 또는 5개의 FPGA 솔루션을 하나의 FPGA로 비용을 절감할 수 있다”고 밝혔다.

버텍스-7 2000T 디바이스는 장비 제조업체에게 통합 플랫폼을 제공하여 제조업체들은 성능과 용량을 늘리면서 전력 소모를 줄이고자 하는 문제를 해결할 수 있다. 회로 보드에서 여러 IC 간 I/O 인터페이스를 제거함으로써 시스템의 전반적인 전력 소모량을 상당히 줄일 수 있다.

회로 보드에 요구되는 IC 디바이스 수가 적을수록 고객은 BOM 및 테스트 개발 주기 비용을 절감할 수 있다. 다이를 실리콘 인터포저 위에 나란히 배치하기 때문에, 이 기술은 여러 다이가 쌓이게 되어 발생하는 전력 및 안정성 문제를 해결할 수 있다. 이 인터포저는 다양한 애플리케이션에 요구되는 고성능 통합을 가능하게 하는 각각의 다이 사이에서 10,000개 이상의 고속 인터커넥트를 포함한다.

버텍스-7 2000T FPGA는 재프로그래밍 기능의 이점과 함께 고객에게 대용량 ASIC에서만 경험할 수 있는 용량, 성능, 전력을 제공한다. 시스템 수가 지속적으로 증가하고 ASIC 개발에 호의적이지 않은 시장 상황에서, 버텍스-7 2000T FPGA는 지나치게 빠른 성장과 28나노 맞춤 제작 IC에 대한 5천만 달러 이상의 NRE(Non-reoccuring engineering) 비용에 대한 우려를 불식시키기 위해 확장 가능한 고유의 대안을 제시하고 있다.

자일링스의 모든 28나노 디바이스(아틱스-7, 킨텍스-7, 버텍스-7 FPGA, Zynq-7000 EPP)는 제품군 내에서 디자인 및 IP 재사용을 지원하는 단일화 된 아키텍처를 공유한다. 이 제품들은 모두 경쟁사 제품과 비교하여 50퍼센트 적은 정적 전력을 소모하는 FPGA를 제공하기 위해 TSMC의 28나노 HPL(HKMG를 통한 저전력) 프로세스에서 구축된다.

낮은 정적 전력은 디바이스 용량이 증가함에 따라 중요한 요소가 되고 있기 때문에, 28나노 HPL은 여러 FPGA에서 구현된 디자인보다 버텍스-7 2000T 디바이스의 더 낮은 전력 소모를 가능하게 하는 주요인이 되고 있다.

ARM의 디자인 기술 및 자동화의 부사장인 쟌 구데노는 “ARM은 자일링스와 협력하여 당사의 검증 인프라에 동급 최강의 버텍스-7 2000T 디바이스를 사용하게 된 것을 기쁘게 생각하고 있다”라며, “새로운 디바이스는 아직 목표가 되지 않았지만, 유연한 에뮬레이션 아키텍처를 보강하면서 차세대 프로세서를 위한 완벽한 시스템 검증 및 확인을 더욱 쉽게 실행할 수 있도록 용량을 매우 향상시켰다”고 말했다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>