글|Martin Eibelhuber 박사, 비즈니스 개발 Thomas Glinsner 박사, 프로덕트 매니저 Thomas Uhrmann 박사, Paul Lindner, EV G

NIL(Nanoimprint Lithography)은 3D 패터닝 뿐 아니라 보우(bow), 랩(warp) 혹은 단차가 있는 표면에도 스티칭 에러(stitching-error) 없이 웨이퍼 단위로 나노급 패턴을 만들어낼 수 있어 다양화되고 있는 포토닉스 시장의 요구를 이상적으로 충족한다.

포토닉스의 적용은 새로운 기능, 더 작은 폼팩터, 성능 향상, 비용 감소 등 반도체 산업의 공정 인프라 덕분에 빠른 속도로 성장하고 있다. 그러나 오늘날의 반도체 기술의 대부분은 광자보다는 전자의 흐름을 제어하는데 기반을 둔 전자제품을 개발하기 위해 사용된다. 전자제품의 프린팅 혹은 나노패터닝 솔루션은 기하학적 구조의 미세화가 중요하게 여겨지고 있다.

이와 대조적으로, 포토닉스 제품 개발의 우선 과제는 나노 단위 빛 조절, 즉 패턴의 모양과 반복성이 중요 변수가 된다. 그러므로 나노패터닝 솔루션은 포토닉스 시장에서 중요 공정으로 자리잡을 것으로 기대된다.

태양전지, LED, 광센서와 같은 성숙 단계의 기술들도 이와 같은 빛 조절을 통해 많은 이점을 얻을 수 있는데, 이는 파장 별 흡수, 투과, 반사를 조절함으로써 성능을 획기적으로 향상시킬 수 있기 때문이다. 또한 광결정(photonic crystal), 격자(grating), 위상 변이 구조(phase shift structure), 도파관(wave guide) 등 다양한 방법으로 광 관련 상호작용을 조절할 수 있어 칩 단위 광동작 적용을 가능하게 한다.

.jpg)

.jpg)

실리콘 포토닉 분야에서는 이미 나노급 광구조를 활용해 인터넷 광대역/전기 통신 분야에 랙(rack) 간 데이터 전송 속도를 월등하게 높이는 기술의 적용 가능성을 시현한 바 있다. 나노 단위 광 관련 상호작용 조절은 의료 및 웨어러블 기기 포함 MOEMs(micro-optoelectromechanical systems)를 활용하는 여러 분야에 상당한 영향을 줄 것으로 예상된다.

포토닉스는 매우 다양한 분야에 활용되고 있지만, 양산 시 대부분이 공통된 요구조건을 가지고 있다. 이와 같은 이유로 광학 구조의 연구 및 개발에 직접 구조를 만드는 방법이 광범위하게 사용돼 왔다. 그러나 이와 같은 기술은 비용 효율적 생산을 위한 대형화가 쉽지 않다. 다른 패턴 제작 방법 중 스테퍼(stepper) 같은 경우 대량생산 시 비용적으로 효율적이지만, 포토닉스 산업이 아닌 전자 분야에 적합하게 설계됐다.

하지만 이미 다른 산업분야에서 R&D와 양산 간 격차를 줄인 NIL 공정은 표준화 수준이 낮고 다양화된 포토닉스 시장의 요구를 더욱 간단하게 충족할 수 있다. 특히 UV-NIL은 스티칭 에러 없이 넓은 면적에 패터닝이 가능하다. 이 기술은 3D 포함 다양한 크기와 형태의 패터닝을 지원하고 다수의 광소자에서 요구되는 단차가 큰 거친 표면에도 적용 가능하다.

제한된 노광 면적 때문에 패턴 스티칭에 의존하는 스테퍼는 LED 분야에서 PSS(Patterned Sapphire Substrate)를 생산하는데 널리 사용되고 있다. LED는 일반적으로 사파이어 기판에 GaN 층을 성장시킨 후, 절단/패키지를 거쳐 개별 소자로 생산된다. LED 생산의 주요 목표는 빛 방출(LED로부터 GaN 층을 투과하는 광량)을 최대화하는 것이다. 많은 양의 빛은 도광 효과로 인해 GaN 층에서 걸린다. 그러나 기판 표면에 패턴을 형성함으로써 더 많은 양의 빛을 소자 윗면과 방출되는 방향으로 산란시킬 수 있다.1 또한 이와 같은 구조는 GaN 성장 공정에도 이점이 있는데, 더욱 얇은 완충 층과 현저히 낮은 전위 밀도를 얻을 수 있다.2

크기와 모양 이외에 또 다른 주요 변수는 패턴 간 간격이다. 그림 1a에 제시된 바와 같이 스테퍼로 패터닝하는 경우, 실제 패턴 크기가 마이크론 단위라고 하더라도 일반적으로 스티칭 에러가 발생한다. 약간의 공정 오차에도 큰 간격 오차가 발생하여 제품 품질을 저하시킨다.

마이크로 단위 PSS는 이미 고휘도 LED 생산에서 광범위하게 사용되고 있다. 그러나 nPSS(nanopatterned sapphire substrates)로 알려진 나노급 패턴 구조가 있는 사파이어 기판을 사용하면 LED 성능을 향상시키고, 에피택셜 공정비용을 더욱 감소시킬 수 있다.2 특히 각광받고 있는 UV LED 분야는 방사되는 빛을 UV 파장으로 변환시키기 위해 필요한 AlN(aluminum nitride) 에피층의 낮은 표면 유동성으로 인해 nPSS 구조의 사파이어 기판이 요구된다.3

nPSS가 적층 성정과 발광 효율 측면에서 PSS보다 장점이 많다는 사실은 이미 증명됐지만, 기존의 step-and-repeat 패터닝 공정의 한계로 인해 광범위한 적용이 저하되고 있다. 미세 패터닝을 위해 스테퍼 해상도와 정렬 성능 향상이 필요하지만, 이로 인해 증가하는 생산비용은 LED 성능 향상으로 충분히 상쇄되지 못한다.

스테퍼는 광학적 한계로 노광 영역이 제한되지만, NIL 해상도는 크기에 제한받지 않는다.

NIL용 마스터 템플릿(master template)은 매우 높은 해상도의 e빔 리소그래피를 통해 필요한 필드 사이즈 혹은 기판 크기로 제작한다. 뒤에 마스터 템플릿의 패턴은 워킹 스탬프(working stamp)로 복제되고, 이것이 실제 웨이퍼 공정에 사용된다. 이 같은 방법으로 마스터 템플릿 수명을 노광 공정에 사용되는 마스크 수명에 상응하는 수준으로 연장할 수 있다.

실제 패터닝을 위해 기판에 UV 경화 레지스트를 코팅한다. 다음 투명한 워킹 스탬프를 기판에 접촉시킨다. 레지스트를 UV로 경화한다. 마지막으로, 워킹 스탬프를 분리하고 재사용한다. 이는 위의 설명과 같다(그림 1b). full-field UV NIL을 포함해 이와 같은 공정은 스티칭 에러를 발생시키거나 현저한 비용 증가없이 효율적으로 패턴 사이즈를 감소시킬 수 있다. 그림 2와 같이 스티칭 에러 없는 나노급 패턴 구현은 이미 최대 6인치 웨이퍼까지 적용되어 현재 LED 생산에 사용되고 있다.

nPSS에서 해결해야 하는 과제는 광 응답이 패턴 크기와 주기에 의해 정의되는 브래그 격자(Bragg grating)와 광결정 등 순수한 광구조에서 더욱 중요하게 된다. 광결정은 공기-반도체 계면에서의 손실을 현저히 감소시켜, 고휘도 LED와 태양전지의 효율을 향상시키는데 특히 유용한 것으로 간주된다.

.jpg)

UV-NIL은 하드(hard) 혹은 소프트(soft) 스탬프를 적용할 수 있다. UV가 통과되는 고체로 제작되는 하드 스탬프는 더욱 정확한 정렬을 얻을 수 있지만 균일하지 못한 표면에 대해서는 폴리머로 된 소프트 스탬프가 더 유리하다. 소프트 스탬프의 이점을 적용하는 경우, UV-NIL은 다른 패턴닝 기술과 비교해서 웨이퍼 보우, 랩에 대해 민감도가 낮은 장점이 있으며, 단차에 대해서도 다른 노광 장비보다 유리하다. 위에서 언급한 바와 같이, 스테퍼는 초점 심도에 제한이 많다. 특히 포토닉스 분야에서 필요한 것처럼 패턴 CD(critical dimension)가 마이크론 이하일 경우 더욱 제한적이다.

마이크론보다 작은 CD 구현에 필요한 높은 개구수(numerical aperture)로 인해 초점 심도는 수백 nm 밖에 되지 않는다. 이와 대조적으로 UV-NIL은 40 nm 이하 수준까지 패터닝이 가능하고, 소프트 스탬프를 사용하는 경우(‘soft UV-NIL’라고 불림), 단차가 있거나 곡면에도 패터닝이 가능하다(그림 3). 이와 같은 나노구조는 마이크로 분광기의 스펙트럼 필터 또는 도광 구조의 격자 구조를 적용할 때 적합하다.

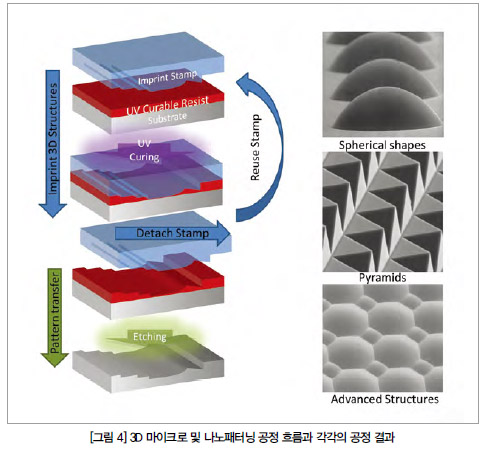

일반적인 노광에서는 구조물을 층층이 쌓을 수 있도록 할 뿐이다. 이것은 전자산업 요구에는 이상적이지만, 광구조 공정에는 적합하지 않다. 이와 대조적으로 soft UV-NIL은 첫 장에서 3D 패터닝이 가능하기 때문에(그림 4), 광 관련 상호작용이 대부분 형태 및 기하학적 구조에 따라 결정되는 포토닉스 산업에 적합하다. soft UV-NIL은 한 번의 공정으로 다양한 높이의 패턴을 생성할 수 있기 때문에, 높은 정렬 정확도가 요구되지 않는다.

원하는 패턴을 레지스트에 프린팅 후 다음 식각 단계에서 기판으로 전송한다. 결과적으로, 곡면 패터닝의 한계(언더컷이 큰 구조)는 크지 않다. e-빔 리소그래피로 제작한 구조물은 대량생산 시에도 soft UV-NIL을 사용해서 패턴 작업을 할 수 있기 때문에 복잡한 광구조물을 더욱 용이하게 구현할 수 있게 된다. 이와 같은 장점은 복잡한 구조도 생산비용이 반드시 높은 것이 아니기 때문에 광구조 설계 시 제약을 더욱 감소시킨다.

UV-NIL은 표준 광을 사용해서 100 nm 이하까지 높은 정렬 정확도를 확보할 수 있어 3D 광결정 등 복잡한 구조가 필요한 3D 구조도 구현이 가능하다.4,5 이와 같은 공정은 그림 5a 삽화에 표시된 바와 같이 3D 광결정이 층층이 적재된다. 대면적의 선 격자를 사용해 3D 스택을 쌓으면서 90도씩 회전시켰다. 이 경우 원하는 디바이스 성능 구현을 위해서는 정확한 정렬이 필수적이다. 그러므로 소프트 스탬프가 선호되는 첫 장 사진 공정과 달리 하드 스탬프의 사용이 필수적이다.

.jpg)

또한 스택 간 정렬정확도 향상을 위해 2단계 정렬 공정이 진행됐다. 우선, 근접 정렬(proximity align) 이후 모아레(moire) 정렬을 진행한다. 층간 정렬을 최적화하기 위해 사용되는 최대 및 최소 이동을 관찰하기 위해 그레이 스케일 이미지 프로세싱(그림 5b)으로 중첩된 모아레 패턴을 평가한다. 이 경우 수십 nm 수준의 정렬 정확도를 관찰한다. 결과적으로, 그림 5a SEM 이미지에서 나타난 바와 같이 5개 층으로 구성된 고품질의 광결정이 제작됐다.

R&D 단계에서 3D 광결정 제작은 단순하고 비용 효율적인 절차라는 것이 증명됐다.4,5 3D 광결정 상용화를 위해서는 더 많은 연구가 필요하지만, 광 트랜지스터 구동에 필요한 광학 비선형성 등 추가적인 장점을 제공할 수 있다. 결과적으로 광결정은 광 컴퓨팅 등 향후 다양한 분야에서 중요한 역할을 담당할 수 있다.

참/고/문/헌

1. Y.C. Lee and S.H. Tu (2011). Improving the light-emitting efficiency of GaN LEDs using nanoimprint lithography. InTechOpen (doi: 10.5772/20712).

2. J.K. Huang et al (2013). Investigation and comparison of the GaN-based light-emitting diodes grown on high aspect ratio nano-cone and general micro-cone patterned sapphire substrate. J Disp Technol, Vol. 9, Issue 12 (doi: 10.1109/JDT.2013.2270276).

3. P. Dong et al (2013). 282-nm AlGaN-based deep ultraviolet light-emitting diodes with improved performance on nano-patterned sapphire substrates. Appl Phys Lett, Vol. 102, 241113 (doi: 10.1063/1.4812237).

4. T. Glinsner et al (2007). Fabrication of 3-D-photonic crystals via UV-nanoimprint lithography. J Vac Sci Technol B, Vol. 25, Issue 6 (doi: 10.1116/1.2798733).

5. M. Muhlberger et al (2007). A moire method for high accuracy alignment in nanoimprint lithography. Microelectron Eng, Vol. 84, pp. 925-927 (doi: 10.1016/j.mee.2007.01.081).

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>