새로운 전자기기의 보급과 성능 향상에 대한 고객의 요구가 늘면서 과거에 단순 제조로 취급됐던 패키지 공정에 고난도 기술이 요구되고 있다. 이런 가운데, 사물인터넷(IoT)과 모바일기기를 위한 미래 기술로 팬아웃 웨이퍼레벨 패키징이 새롭게 주목받고 있다.

팬아웃 웨이퍼레벨 패키징(FOWLP) 공정기술이 성장의 보폭을 크게 확대하고 있다.

기존 패키징 공정 대비 원가 경쟁력이 높은 데다 하나의 패키지에 여러 칩을 넣는 시스템인패키지(System in Package, SIP)가 가능하다는 장점 때문이다. 관련업계는 팬아웃 웨이퍼레벨 패키징이 미래의 모바일 기기와 사물인터넷(IoT) 등에 유리한 공정이라고 평가하고 미래 가능성에 주목하고 있다.

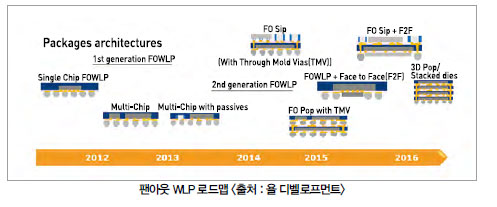

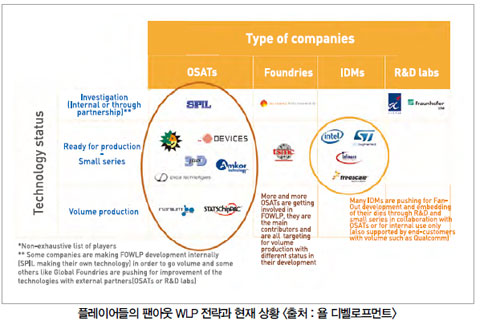

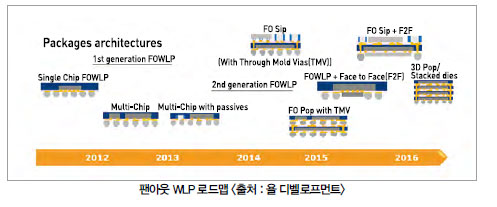

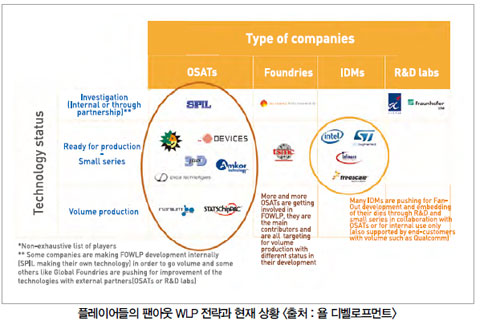

팬아웃 웨이퍼레벨 패키지 공정은 인텔 모바일에 의해 추진돼 2009년과 2010년 관련업계의 주목을 받으며 상용화되기 시작했다. 그러나 핸드폰 베이스밴드 칩의 단일 다이 패키지 등을 제외하곤 적용되는 범위가 좁았기에 2011년 시장의 한계에 도달했다. 그러나 2012년, 대형 펩리스 무선·모바일 업계는 충분한 기술을 갖춘 후 팬아웃 웨이퍼레벨 패키지 공정 기술로 서서히 생산을 시작했다.

2013년과 2014년 두 해에 걸쳐 팬아웃 웨이퍼레벨 패키징 기술은 웨이퍼 레벨 칩 스케일 패키징(wafer level chip scale packaging)과 같은 다른 패키지 기술과 경쟁해야 했으며, 이 시기에 인텔 모바일은 팬아웃 웨이퍼레벨 패키징 기술에서 손을 뗐다. 관련된 주요 업체들 역시 2014년 가격을 절감하며 과도기를 겪었다.

하지만 오늘날 이 시장은 2억 달러(한화 약 2,230억)의 가치를 가진 것으로 평가된다. 향후 연평균 성장률 역시 30%를 웃돌 전망이다. 이는 새로운 팬아웃 웨이퍼레벨 패키징의 시대가 도래했기 때문이다. 2세대의 팬아웃 웨이퍼 레벨 패키징 기술은 과도기를 통해 완성됐으며, 영향력을 갖춘 펩리스 플레이어들에 의해 성장의 불씨가 당겨졌다. 많은 업체들이 이 기술로 전향하면 할수록, 적용되는 애플리케이션의 범위 역시 넓어지고 있다.

가격과 성능, 두 마리 토끼 잡는 팬아웃 WLP

대부분의 모바일 고객들은 저렴한 동시에 고성능·소형 제품에 대한 많은 기대를 갖고 있다. 이러한 고객들의 요구는 관련 제조업체들을 가격·성능 경쟁력을 갖춘 웨이퍼레벨 패키지(WLP) 공정으로 자연스럽게 이끌고 있다.

팬아웃형 웨이퍼 레벨 패키지는 가격과 성능 면에서 최상의 조건을 갖췄다.

이전 세대에서 보여준 낮은 가격 경쟁력과 소형화의 장점은 현재 새로운 세대로 진입해 높은 수준의 통합 역량을 강화하고 있는 상황이다.

.jpg)

3D-TSV(Through Silicon Via)는 실리콘 웨이퍼를 수십 μm 두께로 얇게 만든 칩에 구멍을 뚫고, 동일한 칩을 수직으로 적층하여 관통 전극으로 연결하는 패키징 기법이다. 하지만 3D-TSV 아키텍처 도입이 지연됨에 따라 부각된 팬아웃형 웨이퍼 레벨 패키지는 모바일·무선 시장의 높은 시장 수요에 최적화된 것으로 오늘날 여겨지고 있으며, 고성능과 소형화를 추구하는 시장에 많은 주목을 받고 있다.

반도체 패키징 기업 네페스 홍보팀 관계자는 “구리 재배선 층(Redistribution Layer, RDL)을 칩 바깥으로 형성하는 팬아웃(Fan-out) 방식 특성상, 팬인(Fan-in) 방식과 달리 많은 입출력단자(I/O)를 배선할 수 있기에 칩 크기를 크게 줄일 수 있다”며 팬아웃 방식의 장점을 설명했다. 이어 “팬아웃 웨이퍼레벨 패키징은 미래의 웨어러블, IoT, 센서와 관련해 높은 시장 잠재력을 갖췄으며, 2015년 들어 개발요청이 급격히 증가하고 있는 상황”이라고 밝혔다.

임베디드 다이 패키지의 미래와 과제

팬아웃 웨이퍼레벨 패키징과 비슷하게 임베디드 다이 패키징은 많은 고객들을 끌어 모을 수 있는 잠재력을 갖췄다. 완성된 공급체인을 통해 낮은 가격대를 유지하면서 스몰 폼팩터를 가능케 하며, 짧은 커넥터로 인해 높은 단열성능과 높은 통합 역량, 낮은 인덕턴스(inductance)를 갖췄다.

임베디드 다이 패키징은 미래가 기대되는 공정이지만, 해결해야 할 과제가 남아있다. 바로 공급체인의 문제다. 공급체인은 에이티앤에스(AT&S)와 같은 PCB(인쇄회로기판) 제조업체들에 의해 주도되고 있으며, 이 업체들은 신생업체들을 반도체 산업으로 끌어들이면서 신규 공급 체인을 형성할 수 있을 만큼의 역량을 갖추고 있다.

많은 경험을 보유한 제조업체 공급 체인을 이용하면 비용절감의 효과를 달성할 수 있으며, 이런 장점은 칩의 양면에 쉬운 액세스와 함께 컴포넌트 통합을 쉽게 가능하게 한다. 그러나 신규 공급체인을 이용하면 임베딩 프로세스와 관련된 기술적 경험의 부족으로 인해 새로운 문제를 야기할 가능성도 있다.

단일 다이는 기술 역량을 앞세워 최근에 판매되고 있는 낮은 I/O의 애플리케이션이다. 많은 사람들은 단일 다이 기술이 파워 애플리케이션 시스템인패키지처럼 부가된 복합 시스템과 함께 잠재력을 보일 것이라고 기대하고 있다.

기술적인 요구사항 중에 중요한 것은 바로 다이의 패드 피치(pad pitch)다.

모바일과 무선 시장의 요구량을 충족시키기 위해선 150 μm 이하의 패드 피치 기술을 갖춰야 한다. TDK-EPCOS와 같은 업체는 이미 50 μm 패드 피치의 기술을 갖췄다고 밝혔다. 이와 같은 기술적인 목표가 달성되고 활용하는 애플리케이션이 늘어난다면, 시장은 가까운 미래에 급속하게 성장할 것으로 전망된다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)