글 | 존 먼슨(Jon Munson)애플리케이션 엔지니어 리니어 테크놀로지

isoSPI는 셀을 직렬 연결하여 수백 볼트를 발생시키는 에너지 저장 시스템에 매우 유용한 기능이지만, 인명적 상해를 방지하기 위해 완벽한 절연 분리를 해야 한다. 이글에서는 isoSPI 시스템의 절연과 비용을 낮출 수 있는 방법에 대해 알아본다.

isoSPI™ 기능을 가진 LTC6804 배터리 스택 모니터링 디바이스와 LTC6820 isoSPI 통신 인터페이스 디바이스를 결합하면 전압 장벽이 높더라도 안전하고 견고하게 정보를 전달할 수 있다.

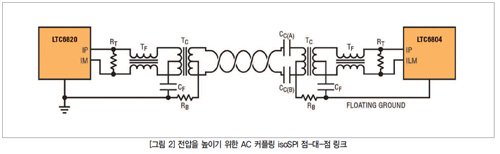

통상적인 isoSPI 애플리케이션(그림 1)은 펄스 트랜스포머를 이용해서 절연을 제공하고 배선으로 가해진 공통 모드(common mode) 간섭을 제거한다. isoSPI 기능은 공통 모드 라인 잡음을 향상하는 공통 모드 초크 섹션(그림 1 참조), 보통의 100 W 라인 종단 저항, 공통 모드 디커플링 커패시터를 비롯한 쉽게 구매할 수 있고 가격이 저렴한 이더넷 LAN 자기 소자들을 이용해 동작할 수 있다.

이더넷 타입이나 게이트 드라이버 타입 같은 일반적인 신호 트랜스포머는 에나멜 와이어를 이용해서 권선을 이루므로 바늘구멍 크기의 절연 결함이 있을 수 있고 그럼으로써 구리를 습기에 노출시켜 트랜스포머가 승인을 받은 권선 간 바이어스를 근본적으로 제한할 수 있다. 이러한 소자들은 생산 시에 조잡한 절연 문제를 찾아내기 위해서 통상적으로 1.5 kV의 높은 전위를 이용해서 테스트한다(이를 흔히 hi-pot(high potential) 테스트라 한다). 이렇게 하는 것이 60 V의 장기적 바이어스의 안전한 설계 마진으로 자리 잡고 있다. 작게라도 부식 부위가 있으면 권선 간에 전도 경로를 형성하기 위해서 60 V 이상을 필요로 할 수 있기 때문이다.

문제: 고전압 = 고비용

배터리 스택 전압이 400 V 대이면 트랜스포머에 강화(이중) 절연을 이용하도록 하고 3750 V 이상으로 hi-pot 테스트를 하는 것이 좋은 설계 관행이다. 그런데 이러한 트랜스포머는 요구되는 연면 거리(표면적)와 공간 거리(절연에 필요한 최소한의 공간) 때문에 소형으로 구하기가 쉽지 않고 비교적 가격이 비싸다. isoSPI는 1 kV에 이르는 배터리 시스템에 적용되며 그러기 위해서는 보수적인 설계 마진을 위해서 5 kV로 hi-pot 테스트를 한 트랜스포머가 필요하다. 이러한 수준이면 절연 장치가 크기가 커지고 가격이 비싸지며 펄스 충실도를 떨어트릴 수 있다.

.jpg)

해결책: ‘분할 지배(divide and conquer)’

강화 트랜스포머를 이용해야 하는 것에 대해서 가능한 대안은 추가적 절연을 커플링 커패시터로 옮김으로써 자기 소자들의 바이어스 요구량을 분할하는 것이다. 커패시터 자체만으로는 완벽한 절연 옵션을 제공하는 것으로 보일 수 있으나 트랜스포머가 제공하는 공통 모드 제거나 충격 방지 절연 특성은 제공하지 못한다. 따라서 실제적으로는 L-C 기법이 적합하다. 이 방법으로 커패시터는 공칭 DC 바이어스로 충전하고 트랜스포머는 트랜션트를 처리하도록 할 수 있다. 그러면 보통의 소자들을 이용하더라도 잘 맞는다.

그림 2에서 보는 것처럼 통상적으로 트랜스포머 센터 탭으로 연결된 높은 값의 저항을 이용해서 커플링 커패시터를 바이어스한다. 그럼으로써 부가적으로 바이어싱 저항의 DC 전류를 모니터링한다면 절연이 무너지는 것을 결함으로써 검출할 수 있다. 이 저항은 10 MW 같이 높은 값으로 선택할 수 있다. 따라서 결함 전류가 안정적으로 트랜스포머의 와이어 정격 이내가 되고 인명 피해 위험성을 최소화할 수 있다.

트랜스포머 자기 디자인의 고전압 요구를 제거함으로써 상대적으로 비용을 낮출 수 있는 여러 가지 기법들이 가능해진다. 그 하나는 단순히 적합하게 승인을 받은 이더넷 트랜스포머를 이용하는 것이다. 또 다른 가능한 방법은 규격형 로우프로파일(높이가 낮은) 자기 소자를 이용해서 장치의 높이를 낮추고 부피를 줄이는 것이다(그럼으로써 납땜을 손쉽게 할 수 있다.).

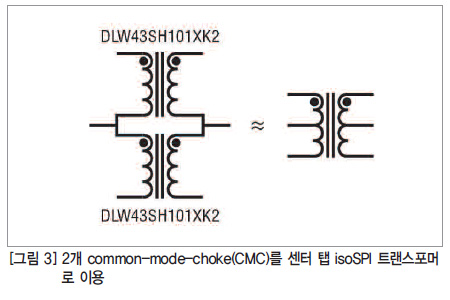

이러한 소자들은 여타 부품들과 마찬가지로 표면실장 자동화 어셈블리 기법을 이용해 설치할 수 있으므로 제조비용을 낮출 수 있다. 이렇게 이용하기에 적합한 것이 바로 이산적 CMC(common-mode-choke)이다. 이는 필터링 소자로 통상적으로 이용되는 트랜스포머 구조이다. 이러한 소자는 최대 100 mH로 이용할 수 있고 자동차 시스템에 이용하도록 승인을 받아 isoSPI 구성에도 이용하기에 바람직하다.

적합한 CMC는 가격이 저렴하다. 칩 크기 페라이트 형태에 기계로 감은 와이어 쌍으로 쉽고 빠르게 제작할 수 있다. isoSPI 디자인은 긴 펄스 파형을 효과적으로 전달하기 위해서 다소 높은 인덕턴스를 필요로 하고 2개 초크를 권선을 직렬로 해서 이용해서 200 mH를 발생시킴으로써 적정한 인덕턴스를 달성할 수 있다. 이렇게 함으로써 부가적으로 가상적인 센터 탭 커넥션을 형성할 수 있는 이점이 있고 그러면 공통 모드 바이어싱과 디커플링 기능에 이용하기에 유용하다.

그림 3은 2개 CMC를 이용해서 구현한 등가 트랜스포머 모델을 보여준다. 이 그림에 표시된 초크는 1812 SMT 풋프린트 사이즈에 bifilar(복선) 권선이다. 그러므로 일차와 이차를 밀접하게 매칭하고 있으므로 누설 인덕턴스를 최소화할 수 있고 고주파 성능을 보존할 수 있다. 권선이 물리적으로 분리되는 타입은 과도한 누설 인덕턴스 때문에 펄스 충실도가 떨어진다. 이 그림의 소자들은 50 V DC 연속 정격이다.

전체적 솔루션

그림 4는 L-C 솔루션과 트랜스포머로 CMC를 이용했을 때 전체적인 회로를 보여준다.

통상적인 isoSPI 애플리케이션은 유용한 CMC 필터링 섹션을 포함하므로(표준적 LAN 소자는 내부적으로 통합) 이 회로는 이 기능을 위해서 권장 이산 소자를 포함한다. 커플링 커패시터는 1812 풋프린트 크기의 고품질 10 nF ~ 33 nF 소자이다(630 V 또는 1 kV 정격). 여기서는 LTC6820을 새시 접지 전위로 동작하는 것으로 간주한다. 따라서 꼬임쌍선(Twisted pair)의 바이어싱이 안전한 수준이다.

그림 5에서 보는 것처럼 데이지 체인으로 연결한 LTC6804-1 모듈 간의 링크와 같이 양쪽 단이 부동 전위인 경우에는 링크의 양쪽 단에 커패시터를 이용할 수 있으며 각 라인으로 높은 값의 저항을 이용해서 ‘어스’ 전위로 바이어스할 수 있다.

이 경우에는 커패시터들이 직렬이므로 최소한 22 nF이 권장된다(이 그림에서는 33 nF/630 V 타입을 이용하고 있음).

.jpg)

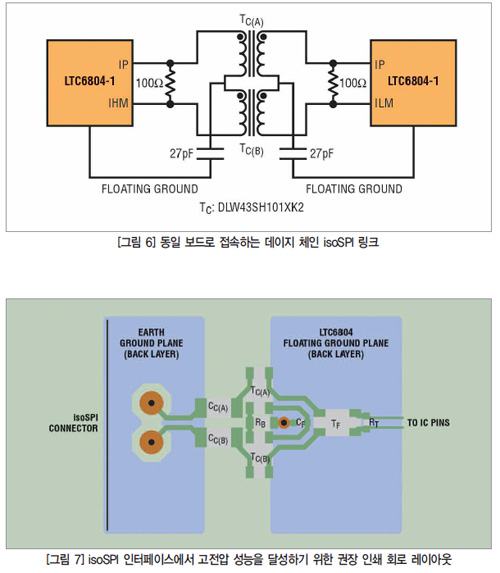

동일 보드 상에서 LTC6804-1를 데이지 체인으로 연결하는 링크는 전위가 보통 50 V 이하이기 때문에 커패시터 커플링이 필요하지 않고 또한 케이블을 이용하지 않아서 잡음 유입이 훨씬 작아 통상적으로 단일 트랜스포머 섹션만을 필요로 한다(그림 6).

고전압 레이아웃

인쇄 회로 레이아웃은 메인 절연 장벽 상에 다시 말해서 커패시터들로 넓은 절연 간격이 필요하다. 그림 7은 우수한 고전압 성능을 달성하는 탑재 예를 보여준다. 파란색 부위는 프레임 접지(왼쪽, 꼬임쌍선 커넥터)와 IC 공통 접지(오른쪽)를 나타낸다.

트랜스포머는 HV 트랜션트 전위를 견뎌야 하므로 여기서도 1206 사이즈 바이어싱 저항을 이용해서 간격을 유지한다. HF 디커플링 커패시터와 임피던스 종단 저항은 소형을 이용할 수 있다(그림에서는 0602 사이즈).

HV 장벽 상에서 누설 전류를 방지할 수 있는 또 다른 좋은 설계 관행은 HV 소자 부위(접지 사이 간격 상의 소자들)에서 솔더마스크를 최소화하는 것이다. 이렇게 함으로써 소자 하단의 플럭스 잔류물을 효과적으로 세척할 수 있고 구멍이 생긴 솔더마스크 층으로 수분을 머금는 것을 방지할 수 있다.

isoSPI 버스의 특수한 고려사항

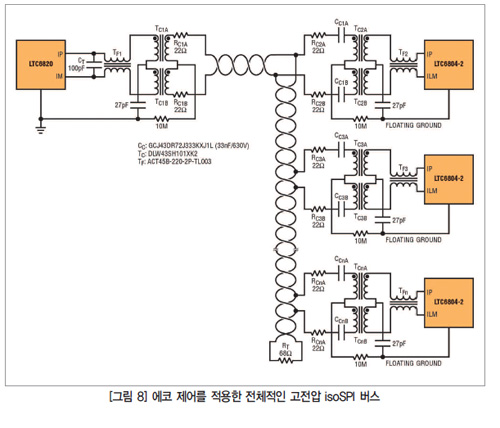

위의 회로들은 점-대-점 isoSPI 링크에 적용하기 위한 것이다. 그런데 고전압 솔루션을 구현하기 위한 또 다른 중요한 방법은 그림 8에서 보는 것과 같이 어드레스가능 LTC6804-2를 버스로 연결하고 꼬임쌍선 링크의 각기 ‘탭’ 접속을 통해서 전달하는 것이다. 이 버스 애플리케이션은 모든 트랜스포머에 고전압이 필요하다. 같은 꼬임쌍선 전위가 부동 셀 스택 상의 어떤 전압과도 인터페이스해야 하기 때문이다.

추가적 절연을 위해서 CMC와 AC 커플링 커패시터를 이용하는 것은 앞서 설명한 것과 마찬가지이다. 다만 이 예에서는 다중의 반사를 약화하고 통신을 위해서 네트워크상의 물리적 위치에 상관없이 일관된 파형 형태를 제공하기 위해서 몇 가지 다른 커플링 회로를 제안한다. 이 회로 예에서는 크게 다음과 같은 세 가지 차이점이 있다.

·LTC6820 종단을 100 pF 커패시터(CT)로 변경한다.

·버스 라인의 가장 끝 종단 라인에 종단 저항(RT) 68 W으로 설정한다(LTC6804-2 들에는 종단 저항을 이용하지 않는다).

·부유 커패시티브 로딩을 디커플링 하기 위해서 모든 버스 접속 지점에 22 W 커플링 저항(RC)을 달아준다.

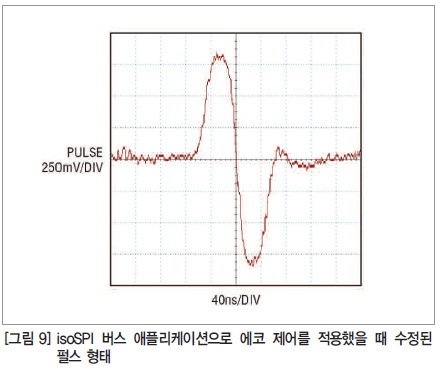

이것을 보여주고 있는 것이 바로 그림 8의 회로이다. 이 예에서도 역시 LTC6820이 안전한 ‘어스’ 전위로 동작하는 것으로 간주한다. 수정된 파형은 대역 제한을 해서 반사로 인한 왜곡을 제어함으로써 IC 핀에서 수신되는 펄스는 그림 9에서처럼 좀 더 둥근 형태가 된다. 그렇지만 isoSPI 펄스 판별(discriminator) 회로가 이렇게 필터링 된 형태를 이용해서 잘 작동하고 전체적인 16 어드레스 버스를 지원할 수 있다. 특정 시스템에서 실제로 발생하는 손실에 따라서 최적 동작을 위해서 펄스 검출 임계값을 낮춰야 할 수 있다(임계값을 차동 신호 피크의 40 ~ 50퍼센트가 되도록 구성).

5개 혹은 그 미만의 어드레스를 가지고 있는 네트워크일 때는 반사가 대체로 중대한 문제가 되지 않는다. 그러므로 표준적 저항 종단을 그대로 유지할 수 있다(그림 8에서 CTERM 및 RTERM 위치에 100 W, RC들은 제거).

결론

AC 커플링 기법을 이용해서 고전압 isoSPI 시스템의 비용 문제를 완화할 수 있고 자기 소자에 대한 이중 절연 요구를 제거할 수 있다. 특수한 도넛형 트랜스포머 자기 소자를 저렴한 보빈 권선 common-mode-choke(CMC) 소자로 대체함으로써 비용을 추가로 더욱더 낮출 수 있다. 커패시터와 CMC는 둘 다 비교적 높이가 낮은 표면실장 칩 소자이고 가격대가 저렴하고 자동차용으로 높은 신뢰성을 달성하는 것을 이용할 수 있다. AC 커플링에 이용되는 바이어스 저항은 시스템의 절연 무결성을 모니터링할 수 있는 유용한 수단을 제공한다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>