글 | 엘레인 라프라디(Alain Laprade) 온 세미컨덕터

OTA(operational transconductance amplifier)는 차동 입력 전압과 비례하는 전류 소스이다. 다이의 OTA 출력과 패키지 핀-아웃 사이에 전류 제한 직렬 보호 저항기(RESD)와 전압 클램프를 배치하면 ESD 견고성이 유지된다. 디바이스 제조사는 이 ESD 보호 저항기의 영향이 미미하다고 여기고 데이터시트에 매개 변수를 수록하지 않는다. 하지만 출력 임피던스의 영향을 간과하면 피드백 루프 보상 게인 및 위상 오차로 이어질 수 있다. 전원 공급 OTA 보상 전달 함수는 ESD 보호 저항기를 포함하여 도출된다.

서론

OTA는 출력 전류가 증폭기의 차동 입력과 비례하는 전류 증폭기(그림 1)로 제어되는 전압이다. 증폭기 transcon-ductance gain은 gm으로 정의된다. 전압 증폭기보다 적은 다이 면적을 요구하는 OTA는 주로 전원 공급 제어 장치 및 레귤레이터 IC의 피드백 증폭기로 구현된다.

패키지 핀-아웃 옵션으로 보상 핀이 제공될 경우, OTA 출력부의 전압 클램프와 전류 제한 직렬 저항기를 사용하여 다이 레벨 ESD 보호가 실행된다(그림 2). 그뿐 아니라 OTA는 병렬 합성 저항기(R0)와 콘덴서(C0)로 구성된 출력 임피던스를 통해 접지된다. 증폭기 전달 함수는 외부 보상 회로망과 결합한 OTA의 출력 임피던스 구조에 의해 결정된다.

.jpg)

.jpg)

특정 응용 분야의 경우, Resd가 OTA 전달 함수에 미치는 영향이 미미하다. PFC 용도가 그러한 경우이다. 글의 후반부에서 표현되겠지만, 참고문헌[1]의 359 ~ 381P에 나타난 OTA 설계 예시의 보상 값이 적용될 경우, 입력 전압 피드백 분할기에 의한 최종 DC 게인 감쇠는 Resd에 의한 미미한 보상 오차로 이어진다.

낮은 입력 전압 소스로 작동하는 부스트 컨버터는(자동차 배터리와 같은) OTA 입력 분압기가 제공하는 큰 폭의 입력 전압 게인 감쇠 혜택을 보지 못한다. 보상 회로망 저항값은 원하는 중대역 게인 감쇠를 달성하기 위해 더 낮은 값이 필요할 것이다. 펄스 폭 변조(PWM) IC 제어 로직은 ESD 저항기의 OTA 측에서 나오는 Vctrl 신호를 피드백 제어 신호로 활용한다. 피드백 루프 측정 과정에서는 OTA 출력(Vctrl )에 직접 접근할 수 없는데 Resd의 값이 pin Vc와 연결된 보상 회로망 저항과 크기가 비슷할 경우 전원 공급 피드백 루프 게인과의 위상 오차가 초래된다.

전자 업계에서 Types-1/-2/-3 보상 회로망으로 묘사하는 개정된 도식을 이상적 OTA[1]를 위한 도식과 비교해보자. IC의 보상 핀 Vc로부터 얻어진 경험적 측정을 통해 올바른 OTA 전달 함수를 구하려면 보정 계수가 필요할 수 있다. 그림 2 OTA 모델은 Type-1esd / -2esd / -3esd 보상 회로망 도출을 위한 빌딩 블록이다(그림 6, 그림 9 및 그림 12). 설계 예시를 뒷받침하는 데 사용하기 위해 NCV8871[4] 부스트 컨트롤러 IC OTA의 매개 변수를 사용하면 Ro = 3 MΩ, gm= 1.2 mS, internal Vref = 1.2 V의 결과값이 나오는데 NCV8871 IC 설계 집단으로부터 공개되지 않은 매개 변수 Resd = 542 Ω 및 Co 쩁 10 pF를 얻을 수 있다.

.jpg)

.jpg)

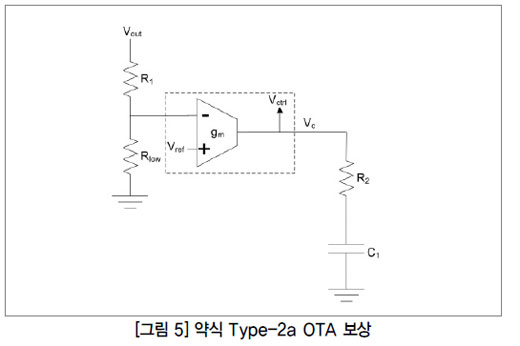

2차 전달 함수의 루트 풀이

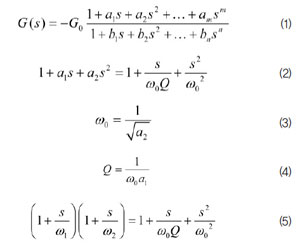

도출할 OTA 보상 회로망 전달 함수는 등식 (1) 일반 다항식 표현으로 설명된다. 전달 함수 순서 m과 n은 독립적인 저장 요소의 수에 의해 결정되는데 여기서 m < n이다. 높은 순서의 도식은 분자와 분모를 통한 루트를 식별시키지 못한다. Middlebrook [3]은 2차 표현의 직관적인 인수 분해 방법을 설명하고 있는데 등식 (2) ~ (7)로 요약된다. 등식 (2)의 루트는 등식 (6)과 (7)에서 정의된다. OTA 보상 회로망의 경우 실제 값은 ω1와 ω2이다.

그림 3의 약식 OTA 모델에서 도출된 Type-1 보상 OTA가 [1]에 설명되어 있다. 보상 핀 VC와 지면 사이에 콘덴서 C1이 위치한다. Resd i가 보상 콘덴서 C1과 직렬로 존재하므로 Type-1esd OTA(그림 4)는 다음에 설명된 Type-2aesd OTA로 올바르게 분석된다.

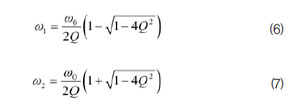

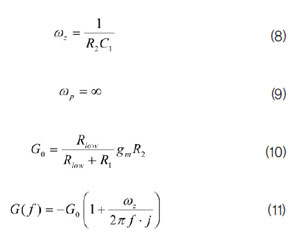

Type-2aesd OTA

그림 5 약식 OTA 모델의 Type-2 OTA 보상이 [1]에 묘사되어 있다. R2 - C1의 직렬 조합이 핀 VC와 지면 사이에 배치된다. (8) ~ (10)에서 해당 OTA 전달 함수 개념이 재판된다. 핀 VC와 지면 사이에 고주파 바이패스 콘덴서 C2를 배치하는 방안은 하반부에서 설명하기로 한다.

.jpg)

.jpg)

그림 6에 Type-2aesd OTA 보상값이 나와 있는데 이의 전달 함수는 등식 (12)로 설명된다.

.jpg)

등식 (12)의 0은 등식 (14)에서 설명된다. 등식 (6)과 (7)을 통한 루트 추출을 활용하면 등식 (15), (16)으로 설명되는 극이 결정된다. C0 << C1을 가정하고 R0 >> R2eq일 경우, 극은 등식 (16)과 (18)로 더욱 간략해질 수 있다.

.jpg)

.jpg)

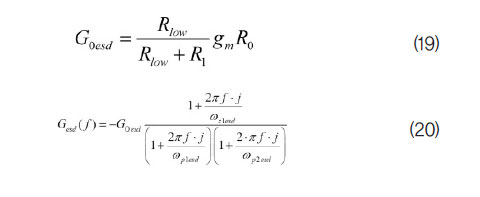

Type-2aesd OTA 전달 함수는 이제 더욱 직관적인 등식 (20)의 형태로 표현된다.

설계 예시처럼, Type-2a 및 Type-2aesd OTA 보상 전달 함수는 R2= 2.0 kΩ, C1= 33 Nf에 대하여 그림 7에서 점으로 표시된다.

Type-2a OTA, ωz = 1.514·1041/s의 경우, Go = 0.282이다. Type 2-aesd OTA의 경우, ωz1esd = 1.192·1041/s, ωp1esd = 3.934·1071/s, ωp2esd = 10.10 1/s, Goesd = 422.368이다.

.jpg)

.jpg)

Type-2besd OTA

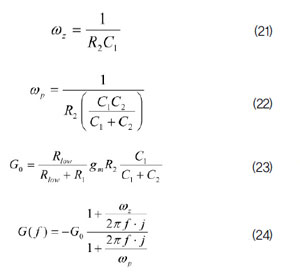

Type-2a 보상 회로망과 병렬로 고주파 바이패스 콘덴서를 추가하여 Type-2b OTA 보상 회로망(그림 8)을 실행한다. [1]에서 도출된 전달 함수 개념은 (21) ~ (24)에서 재판된다.

그림 9의 Type-2besd OTA 보상을 관찰하면 세 개의 독립적인 저장용 콘덴서를 파악할 수 있는데 이는 등식 (25)를 통해 3차 다항식 전달 함수로 이어진다.

.jpg)

계수 ai, bi는 다음과 같이 표현될 수 있다:

설계 예시에서 보듯 구성요소 값으로 R1 = 66 kΩ, Rlow = 10 kΩ, R2 = 2.0 kΩ, C1 = 33 nF, C2 = 470 pF를 선택했다. ~1 MHz 미만 관심 주파수 범위에서 계수 b3의 기여도는 미미한데 b3 = 0을 선택하면 등식 (32)와 같이 G(s)가 2차 표현으로 축소된다. R2eqC1 >> ResdC2, (R0 + R2eq)C1 >> R0C0 및 (R0 + R2eq)C1 >> (R0 + Resd)C2로 인식해보면 이 표현을 더욱 간소화시킬 수 있다.

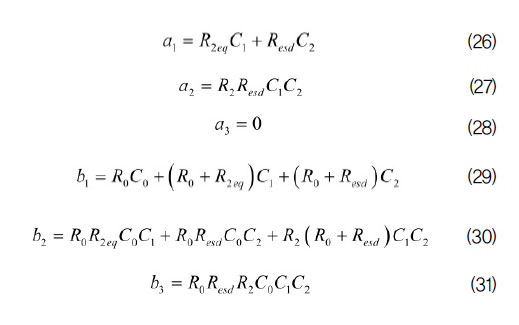

전극, 제로 및 계수 ai, bi는 다음과 같이 나타난다:

.jpg)

그림 10에서 전달 계수 G(f)와 Gesd(f)는 점으로 분포된다. Resd는 ~100 kHz 이상에서 현저해지는 중대역 게인 및 위상 오차를 유발한다.

Type-2b OTA 설계 예시에서 보듯이 ωz1 = 1.515?041/s,ωp1 = 1.079?061/s이다. Type 2-besd OTA의 경우는 ωz1esd = 1.195?041/s,ωz2esd = 4.977?061/s,ωp1esd = 10.10 1/s, ωp2esd = 1.064?061/s이다.

.jpg)

.jpg)

Type 3esd OTA

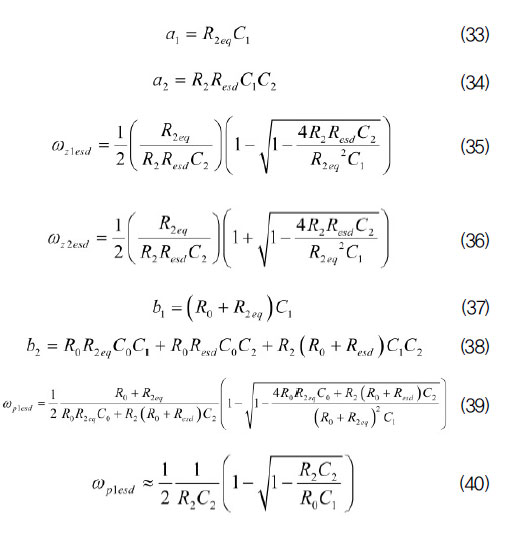

입력 분압기 R1(그림 11, 그림 12)과 병렬로 직렬 R3 - C3 진상 회로망을 배치하면 Type-3b OTA가 보상된다. 진상 회로망의 전극과 제로는 쉽게 식별되므로 제로/전극 전달 함수를 이전에 도출된 Type-2b 및 Type-2besd전달 함수와 곱하면 된다. 진상 회로망 제로 및 전극이 등식 (45)와 (46)에 의해 정의됨을 알 수 있다. Type-3 전달 함수는 등식 (47)로 구해진다.

.jpg)

.jpg)

Type-3besd 전달 함수는 등식 (48)에서 유사하게 정의된다.

Type-3b 설계 예시의 경우 진상 회로망 구성요소에 대하여 R3 = 1 KΩ and C3 = 47 nF가 선택된다. ωz3 = 317.6 1/s, ωp3 = 2.197?031/s가 구해진다.

Type-3b 및 Type-3besd OTA의 최종 전달 함수가 그림 13에 점으로 분포되어 있다. 진상 회로망은 Resd에 의해 초래되는 오차에 영향을 미치지 않음을 설명하기 위해 R1, C1, C2 보상 회로망을 변경하지 않았다. Type-2와 Type-3 보상이 모두 고려될 경우, Type-3 보상(그림 13)에 따른 중대역 게인은 Type-2 보상(그림 10)보다 ~15 dB 높다. R2가 더욱 감소되면서 Type-3 중대역 게인을 낮추면 Resd/R2 비율이 증가하고 Type-3x 및 Type-3xesd 전달 함수 게인 및 위상 간의 분기가 확대된다.

.jpg)

.jpg)

Resd 보정 계수

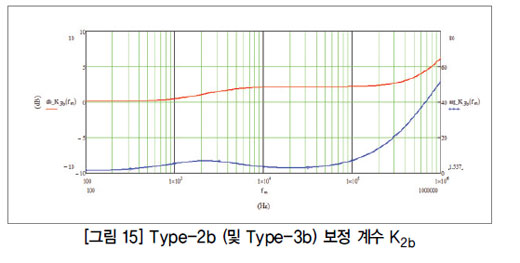

전원 공급 설계 과정에서 일반적으로 피드백 루프 매개변수를 측정하여 게인 및 위상 여유를 검증한다. OTA 전극 및 제로 위치를 선택할 때 데이터를 주파수 종속 보정 계수와 곱하여 핀 Vc에서 반응을 경험적으로 측정함으로써 IC의 내부 제어 신호(Vctrl)게인과 위상 거동을 도출할 수 있다. 보정 계수는 Type-2a 및 Type-3a 보상의 경우 등식 (49), Type-2b 및 Type-3b 보상의 경우 등식 (50)과 같이 Gesd(s)/G(s) 비율을 표현함으로써 결정된다.

앞서 설명한 Type-2esd 예시에 해당하는 보정 계수 곡선 K2a(f)과 K2b(f)이 그림 (14)와 (15)에 나와 있다.

.jpg)

결론

출력 직렬 ESD 보호 저항을 포함한 OTA 모델을 설명했다. 전원 공급 Type-1 보정은 Type-2a 보상으로 올바르게 모델링된 것으로 나타났다. Type-2 및 Type-3 보상과 관련한 전달 함수가 도출됐다. 보상 게인이 피드백 입력 분압기에 의한 대폭적 감쇠에 따른 혜택을 보지 못할 경우, 낮은 입력 전압 용도에서 이상적 OTA 모델의 중대역 고주파 게인 및 위상 오차가 확연해질 수 있다. 경험적 측정을 통해 피드백 제어 전달 함수 표현을 도출하기 위해 보정 계수를 도입했다.

.jpg)

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>