글 | 매스웍스

이 글은 FPGA 통합 워크플로우에서 매스웍스의 HDL CoderTM가 알테라(Altera짋) DSP와 함께 어떻게 사용되는지 설명한다.

서론

매트랩(MATLAB짋)과 시뮬링크(Simulink)는 디자인, 모델링, 시뮬레이션, 코드 생성 및 적용에 걸친 개발 플랫폼을 구현하는 엔지니어에게 신호, 이미지, 비디오를 제공한다. FPGAs 또는 ASICs를 대상으로 모델 기반 설계를 사용하는 엔지니어들은 매트랩, 시뮬링크와 스테이트플로우(Stateflow짋)를 활용하여 시스템을 설계, 시뮬레이션할 수 있다. 또한 비트-트루(bit-true)와 사이클 정확성(Cycle-Accurate), 통합 가능한 Verilog, VHDL 코드를 HDL Coder를 사용하여 만들 수 있다.

대신에 특별히 알테라 FPGAs를 대상으로 하는 엔지니어들은 시뮬링크 코드 생성 소프트웨어(Simulink Code Generation Software)의 DSP Builder 플러그인을 사용하여 선-최적화된(Pre-Optimized) 구현을 가능하게 하는 통합할 수 있는 하드웨어 기술 언어(Hardware Description Language, HDL) 코드를 제작할 수 있다. DSP Builder는 상위 레벨이 시한적이지 않은 넷리스트(Netlist)와 낮은 레벨의 파이프라인식 하드웨어를 대상으로 한 알테라 FPGA 기기와 알맞은 클록 속도에 맞게 최적화하는 상위 합성 기술(High-Level Synthesis Technology)인 DSP Builder Advanced Blockset가 포함됐다.

몇몇 프로젝트는 기존의 시뮬링크 워크플로우와 장치 독립형 코드(Device-Independent Code), 코드 가독성(이 가독성은 알테라에 특화된 특징들(Altera-Specific Features)과 최적화 기술이 포함된 HDL Coder에게서 제공된다.)을 동시에 가진 워크플로우를 사용하여 혜택을 받는다 .

이 문서는 시뮬링크와 DSP Builder의 블록(Blocks)으로 만들어지는 설계에 필요한 새로운 워크플로우를 서술하고 있다 .

필요 소프트웨어

이 문서에서 언급되는 모델은 알테라 DSP Builder Advanced Blockset을 사용하는 HDL Coder에 포함되는 예제들이다. HDL Coder의 시뮬레이션과 코딩은 아래의 소프트웨어에서 검증됐다:

-- MATLAB(R2013b 또는 이후 버전)3

-- Simulink

-- HDL Coder(MATLAB CoderTM와 Fixed-Point DesignerTM가 필요)

-- Altera DSP Builder(13.0sp1 또는 이후 버전)

DHL Coder의 코딩을 검증, 통합 그리고 적용하기 위해선 아래의 소프트웨어도 필요하다:

-- Altera Quartus II(13.0sp1 또는 이후 버전)

HDL Code 제작과 DSP Builder Advanced Blockset 통합을 위한 매트랩 환경 설정

모델을 작업하기 전, MATLAB 환경 설정이 DSP Builder와 매트랩이 연동하여 사용될 수 있는지를 확실히 알아야 한다. DSP Builder를 시작하기 위해선 아래의 단계 중 하나를 따라 해야 한다(DSP Builder Handbook - Volume 1 참조: 더 자세한 사항을 원한다면, Introduction to DSP Builder 참조):

Microsoft Windows에서는 시작 단추를 클릭하여 모든 프로그램에 접근해 Altera<버전>을 클릭, DSP Builder를 클릭, 그리고 Start In MATLAB<버전>를 클릭한다.

- 여러 버전의 MATLAB이 설치되어 있다면, 여기의 메뉴에서 원하는 버전의 MATLAB에서 DSP Builder를 사용할 수 있다.

Linux OS에서는 자동으로 매트랩을 찾는 명령어를 사용한다:

-- 다른 매트랩 방향(Path)을 주려면-m

-- 32-bit DSP Builder를 사용하려면 -glnx86

매트립 환경 또한 Quartus II 설치에 따라 만들어져야 한다. 이것은 매트랩의 명령어 hdlsetuptoolpath를 통해 할 수 있다. 아래의 명령어는 Windows PC Quartus II 설치를 위한 일반적인 방향을 보여준다.

>> hdlsetuptoolpath(‘ToolName’, ’Altera Quartus II’, ’ToolPath’,

’C:\altera\13.0sp1\quartus\bin64\quartus.exe’);

hdlsetuptoolpath가 이번 매트랩 작업에 국한된 시스템 방향과 시스템 환경 변수들(The System Path and System Environment Variables)을 바꾸었다는 것을 알 수 있다. 매트랩 시작 시 자동으로 hdlsetuptoolpath 명령어를 실행하려면 setup.m 스크립트에 추가하면 된다.

예제: 시뮬링크와 DSP Builder Advanced Blockset의 블록을 이용한 디자인

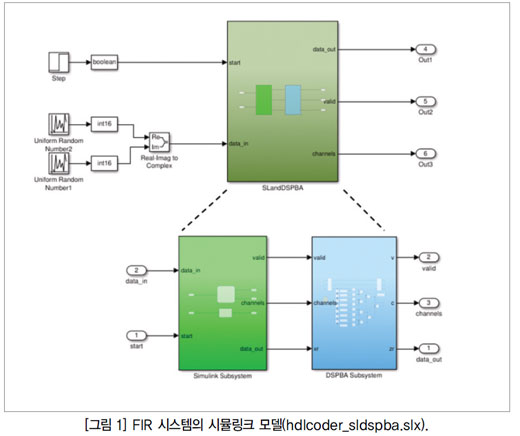

예제 모델(hdlcoder _ sldspba.slx)은 FIR Filtering을 구현한다. 이 상위 레벨의 설계는 두 가지의 하위 시스템을 포함한다. 하나는 DSP Builder Advanced Blockset의 블록을 이용한 것이고 다른 하나는 일반 시뮬링크 블록을 이용한 것이다(그림 1). 이들은 알테라 기기에 통합을 위해 설계됐기 때문에 알테라 블록들은 알테라 FPGA 위에 FIR Filter의 최적화된 실행을 해낼 수 있다. 이 시뮬링크의 하위 시스템은 복잡한 통제 알고리즘을 모델링하는데 유동성을 제공하는 스테이트플로우 블록과 매트랩 기능 블록(MATLAB Function Block)을 포함한다. 또한 사용자들은 HDL Coder를 통한 시뮬링크 하위 시스템의 다양한 최적화 기능을 경험할 수 있다.

HDL 코드 제작을 위한 모델 준비

일반적인 개발 워크플로우에서 엔지니어는 준비과정으로 시뮬링크의 설계를 가지고 반복적인 모델링과 시뮬레이션 작업을 통해 디자인 문제를 찾아 제거한다. HDL Coder와 DSP Builder Advanced Blockset을 사용하여 코드를 만들기 전, 아래의 과정을 거친 후 모델을 준비해야 한다:

-- DSP Builder(DSPB) 하위 시스템 생성

--- DSPB 하위 시스템의 코드 제작 옵션(Code Generation Options) 설정

-- HDL Coder의 코드 제작 옵션 설정

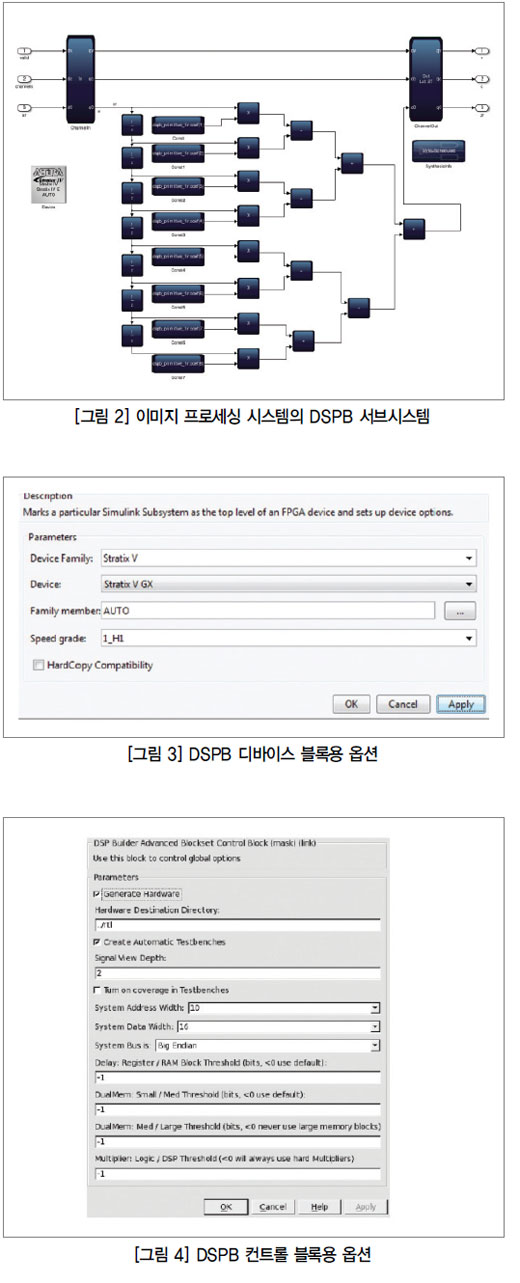

DSPB 서브시스템 생성

DSPB 서브시스템을 만들기 위해선:

1. 모든 알테라 블록들을 한 서브시스템에 넣는다.(주의: 일반적으로 HDL Coder는 모든 알테라 블록들을 반드시 포함하는 다수의 DSPB 서브시스템의 사용을 지원한다; 하지만 이러한 예제는 단 한 개의 DSPB 서브시스템의 사용을 보여준다.)

2. 이러한 서브시스템의 아키텍처 매개변수가 모듈로 맞춰져 있는지 확인한다(디폴트 값). 이 설정의 더 많은 것을 필요하다면 HDL Coder를 위한 코드 제작 옵션(8면)을 참조한다.

3. 기기 블록(Device Block)을 서브시스템의 가장 윗부분에 놓는다. DSPB 서브시스템은 계층적인 구조(Subsystem Hierarchy)를 지닐 수 있지만, 기기 블록이 계층적 구조의 꼭대기에 항상 있어야 한다.

4. 통제 블록과 신호 블록을 모델의 가장 윗부분에 놓는다.

밑의 MATLAB 명령어를 사용하여 예제 모델의 DSPB 서브시스템을 열 수 있다(그림 2).

>> open _ system(‘hdlcoder _ sldspba/SLandDSPBA/

DSPBA Subsystem’);

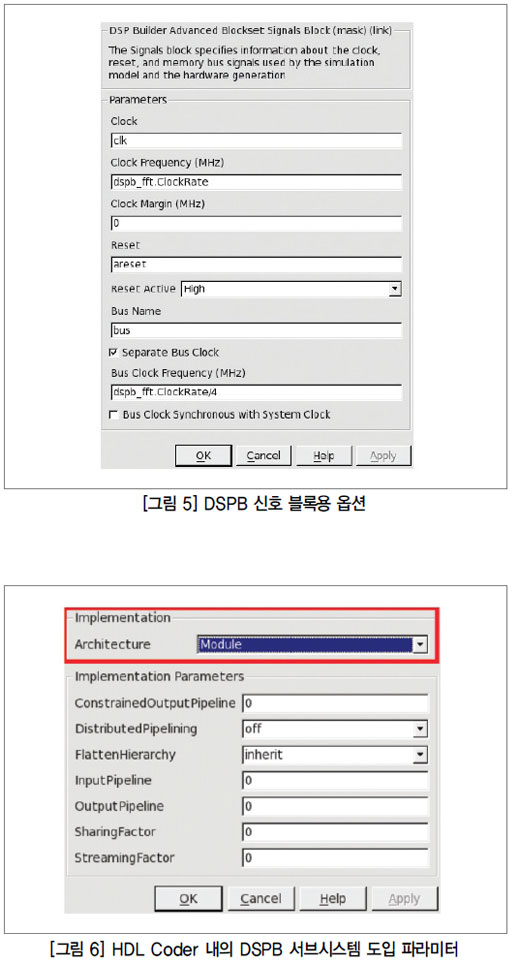

DSP Builder를 위한 코드 제작 옵션 설정

HDL Coder는 밑의 설정만을 가진 DSP Builder 코드 제작을 지지한다:

기기 블록 (그림 3):

- 가능하면, 모든 기기 블록들과 HDL Coder에 의해 같은 기기가 반드시 선택되어야 한다.

통제 블록 (그림 4):

- Generate Hardware는 반드시 체크되어야 한다.

- Create Automatic Testbenches는 체크되지 않아야 한다.

신호 블록 (그림 5):

Reset Active는 반드시 HDL Coder의 설정과 같아야 한다.

이 설정은 직접 할 필요는 없다. HDL Coder가 DSP Builder 블록의 이 설정 코드를 제작하는 동안 수정하고 복원시킬 것이다.

HDL Coder를 위한 코드 제작 옵션 설정

위에 설명된 HDL Coder 제작의 설정보다 좀 더 추가하면 HDL Coder는 DSPB 하위 시스템의 아키텍처 매개변수가 모듈로 설정돼있어야 한다(그림 6).

만약 코드 제작이 HDL Workflow Advisor에 의해서 실행된다면 그림 3과 7에서 보이는 것처럼 Workflow Advisor와 DSPB 기기 블록의 기기 설정은 반드시 일치해야 한다.

HDL 생성

다른 모델을 사용하는 것처럼 HDL 코드도 이미 설정돼있는 모델을 사용하여 명령 라인 인터페이스(Command Line Interface) 또는 GUI를 통해 생성할 수 있다. 코드 생성을 위한 이번 예제 모델에 필요한 명령어는 아래와 같다:

>> makehdl(‘hdlcoder _ sldspba/SLandDSPBA’)

GUI를 사용하여 코드를 생성하는 자세한 내용은 HDL Coder에서 제공되는 HDL Code Generation from a Simulink Model 튜토리얼을 통해 참조할 수 있다.

HDL 테스트 벤치와 시뮬레이션 스크립트 생성

테스트 벤치와 시뮬레이션 스크립트 생성을 위한 이 예제 모델에 필요한 명령어는 아래와 같다:

>> makehdltb(‘hdlcoder _ slsysgen/SLandSysGen’);

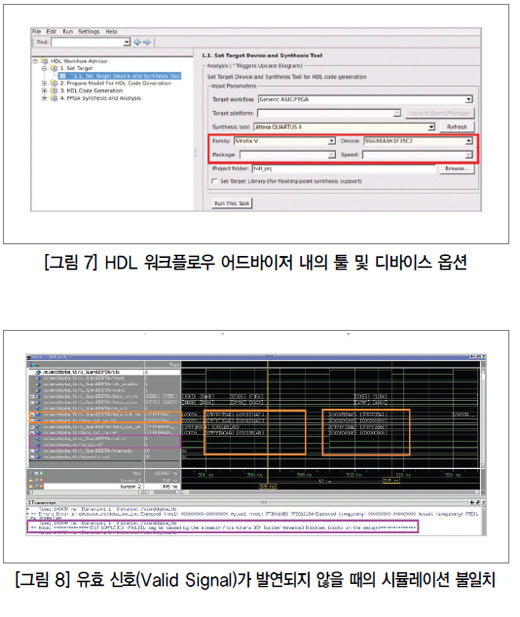

유효 신호가 발연 되지 않을 때의 시뮬레이션 불일치 처리

특정 상황에 따라 유효 신호가 발연되지 않으면, 이 DSPB 서브시스템 시뮬레이션은 생성된 코드의 행동에 맞지 않은 시뮬레이션이 보일 수 있다. 예를 들어 디자인이 접힘, 최적화 또는 부동 소수점 지원을 사용할 때 이런 불일치를 보일 수 있다.

이 불일치는 hdlcoder _ sldspba/SLandDSPBA/DSPBA Subsystem/ChannelIn hdlcoder_sldspba/SLandDSPBA/DSPBASubsystem/ChannelOut에 있는 Folding 설정을 활성화하는 것을 통해 관찰할 수 있다. 또한 후속 시뮬링크 설계에 영향을 주고 테스트 벤치 시뮬레이션의 실패를 가져온다. 이러한 불일치를 보기 위해 ChannelIn과 ChannelOut의 Folding 설정을 활성화할 수 있다:

>> set _ param(‘hdlcoder _ sldspba/SLandDSPBA/DSPBA Subsystem/ChannelIn’,

‘FoldingEnabled’, 1);

>> set _ param(‘hdlcoder _ sldspba/SLandDSPBA/DSPBA Subsystem/ChannelOut’,

‘FoldingEnabled’, 1);

이 후, HDL 코드와 테스트 벤치를 다시 생성한다:

>> makehdl(‘hdlcoder _ sldspba/SLandDSPBA’);

>> makehdltb(‘hdlcoder _ sldspba/SLandDSPBA’);

이렇게 생성된 코드와 테스트 벤치를 시뮬레이션하면, HDL Coder에서 나온 결과와 참고 데이터가 그림 8에서 보이는 것처럼 유효 신호가 발연되었을 때만 일치한다는 것을 볼 수 있다.

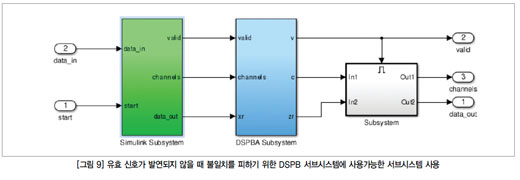

테스트 벤치에서 나온 메시지가 가리키는 것처럼 이 불일치는 예상된 것이다. 시뮬레이션 불일치를 피하기 위해선 DSPB 서브시스템 출력 신호들(DSPB Subsystem Output Signals)이 설계의 시뮬링크 부분 또는 출력 포트(Output Port)에 도달하기 전, DSPB 서브시스템 출력 신호에 사용할 수 있는 서브시스템을 삽입해야 한다. 그림 9는 신호들을 어떻게 사용 가능한 서브시스템과 연결하는지를 보여준다.

>> open _ system(‘hdlcoder _ sldspba/SLandDSPBA2’);

추가 자료

추가적인 HDL Coder 비디오와 예제들은 mathworks.

com/products/hdl-coder/examples.html.에 방문하여 찾을 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>