온도 사이클링 환경에서는 CTE 불일치가 전자기기 어셈블리 속의 솔더 조인트 피로 및 PTH 피로의 주원인이다. 여러 가지 분석적인 도구들이나 모델들이 솔더 조인트나 PTH 피로를 예측하는 데 사용될 수 있다. DfR Solutions 사의 Sherlock 소프트웨어는 실제 수명 조건을 모델로 만들기 위해 PoF(Physics of Failure, 고장물리)을 사용하는 강력한 차별적 도구이다.

열 사이클링 피로

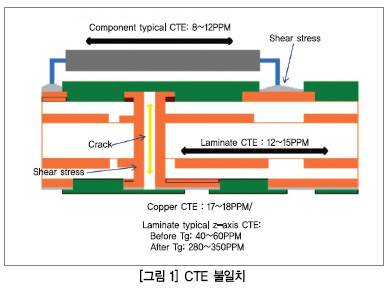

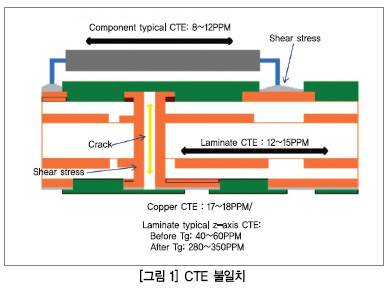

대부분의 전자기기 고장은 열이 초래한 스트레스와 함께 사용된 재료들 간의 과도한 열팽창계수(Coefficient of Thermal Expansion, CTE)의 차이 때문에 야기된 변형으로 발생한다. 이러한 CTE의 불일치는 전자기기 조립과정에서 1단계 및 2단계 상호접점(Interconnects)에서 일어난다. 1단계 상호접점은 다이(die)를 서브스트레이트(substrate)에 연결하는 것이다. 1단계 연결에는 언더필 처리(Underfilled)가 될 가능성이 있으며, 전체 또는 국부적인 CTE 불일치를 염두에 두어야 한다. 2단계는 이 서브스트레이트 또는 패키지를 인쇄회로기판(Printed Circuit Board, PCB)에 연결하는 것이다. 이 경우 컨포멀(conformal) 코팅을 사용하는 것과 같은 스트레스 완화 테크닉이 존재한다. 이런 것들이 “보드 레벨” CTE 불일치로 간주되고, 그림 1은 이러한 조건들을 도식적으로 보여준다.

현장에서의 온도 사이클링

현장 조건은 어떻게 사용하는 지와 어떤 응용 환경이냐에 따라 다르다. 동일 전자제품이라도 산업과 응용분야에 따라서 여러 현장 조건을 가질 수 있다. LCD 터치패널, 전압 레귤레이터, 네트워킹 모듈이 그 예이다.

각 산업분야로 구분된 몇몇 공통 온도 사이클링 조건이 그림 2에 나타나 있다.

단기간 사용 후 오랜 기간 저장하는 특수한 현장 조건이 있을 수 있다. 군수품, 발사대, 심장박동전기충격기(Automatic External Defibrillator, AED), 에어백 등이 이 부류에 속한다.

가속수명테스트(Accelerating Life Tests)

가속수명테스트(Accelerating Life Tests)

전자기기를 하루 1사이클씩 20년을 테스트 하는 것은 바람직하지도 않고 가격대비효과가 낮으며 효율적이지 않은 전략이다. 그래서 가속화한 조건에서 수명 테스트를 실행한다. 일반적으로 그 목표는 동일한 주 고장 모드를 유지하면서도 정상적인 수명 조건을 초과하는 스트레스를 사용하는 것이다. 공통된 프랙티스는 더 높은 온도와 더 큰 부하를 사용하는 것이다. 가속 테스트는 다른 고장 모드 결과를 가져올 수 있기 때문에 테스트 조건의 검증은 대단히 중요하다. 하나의 테스트가 얼마나 가속될 수 있는 지에도 역시 한계가 있다. 가속화한 열 사이클은 우리에게 시간적인 장점을 제공한다. 15분간 램프(위 또는 아래방향)하고 15분간 온도한계치로 유지하면 시간당 1회의 열 사이클링을 수행하는 것이다. 이는 하루에 24사이클, 42일(6주)이면 1,000 사이클을 완료할 수 있다. 만약 이것이 하루에 1사이클의 사용조건을 표현하다고 하면, 이는 2.7년에 해당하는 현장 열 사이클링과 일치하는 것이다.

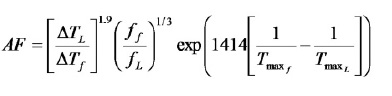

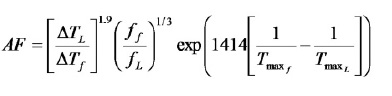

적절한 가속계수(Acceleration Factor, AF)를 사용하는 것은 유용한 자료를 만드는 데 매우 중요하다. 이 가속계수(AF)는 다음과 같은 Norris Landzberg 가속계수 공식으로 계산된다.

조건:

ㆍ L = 실험실 조건

ㆍ f = 현장 조건

ㆍ f = 주파수 [사이클/일]

열팽창계수(CTE)의 관리

사용자나 설계자가 부품 속성에 영향을 미칠 가능성은 낮다. 부품 패키징은 대체로 다이와 어셈블리에 의해 좌우된다. 리드프레임 재료나 JEDEC표준 패키지 테스트를 통과하는 부품 제조업체 디자인에는 선택이 제한되어 있다.

과거에는 전자 패키지가 구리 CTE 값인 17.6 ppm/℃와 비슷한 값을 가졌다. 그러나 산업계가 패키지 크기 대비 더 커진 다이나 하단 터미네이션 부품(Bottom Termination Components, BTC)을 사용하게 되면서 상황이 바뀌었다.

BTC들은 리드가 없는 패키지(Leadless Package)로서 호환성과 견고성이 떨어지는 리드가 된다. 전형적인 비 리드형 세라믹 칩 저항기는 ~5.6 ppm/℃의 CTE 값을 가지고 있는 반면, QFN(Quad Flat No-leads)은 8~12 ppm/℃의 CTE 값을 가지고 있다. 더 커진 패키지는 훨씬 큰 CTE 불일치 효과를 가진다.

보드 속성의 영향

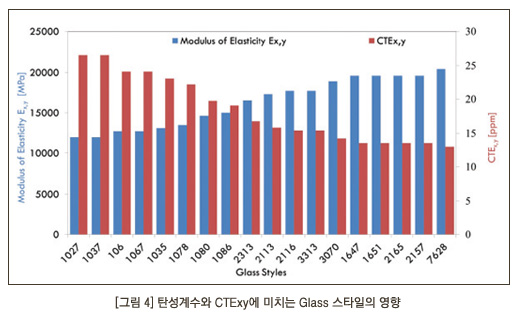

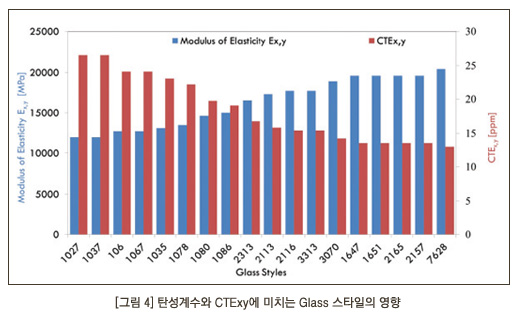

PCB의 CTE에 영향을 주는 주요 원인은 Glass 스타일, 라미네이트 타입, 구리 두께 및 보드 전체 두께이다. 일반적으로 라미네이트의 CTE 값은 감소하는 중이다. 그러나 PCB 라미네이트 제조업체들은 이를 결정하기 쉽도록 만들지 않는다. 면외 CTE(Out-of-Plane CTEz) 값은 대개 라미네이트 데이터시트를 보면 알 수 있다. 그러나 몇몇 데이터시트에서는 자료가 유리전이온도(Glass Transition Temperature) Tg에서 더 높거나 낮은 ppm/℃으로 나타내지만 다른 데이터시트에서는 50C ~ 260C 사이에서 %로 표시되기도 한다. 따라서 사용자는 항상 문서에 인쇄된 부분을 신경써서 읽어야 한다. 낮은 CTE 값을 가진 라미네이트는 고유한 문제들을 가지고 있기 때문에 낮은 CTE 값과 가격은 서로 상충되는 조건이기 마련이다.

PCB Glass 스타일의 영향

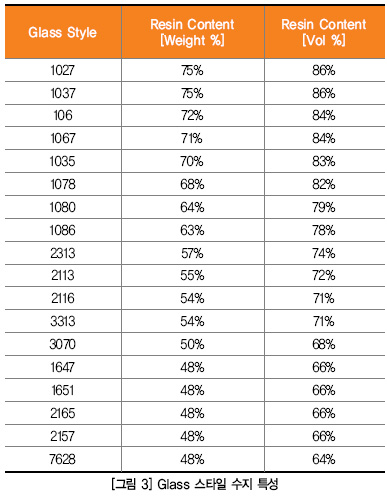

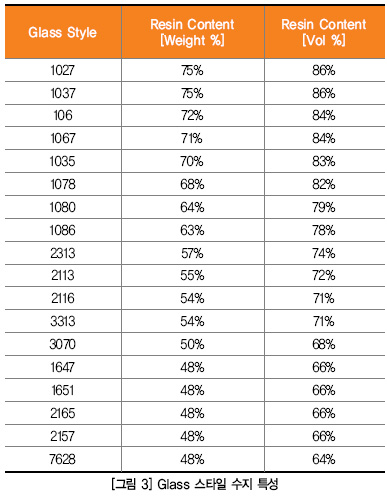

보드 CTE 값의 현실적인 목표는 15~17 ppm/℃이다. 대부분의 라미네이트 공급자들은 CTEz 값들과 함께 CTExy 값도 제공한다. 그러나 이러한 값들은 무게 기준으로 46% ~ 50% 수지함유율을 가진 7682 glass 스타일을 사용하는 낮은 수지함유 라미네이트에 대한 것이다. 대부분의 범용 라미네이트는 더 높은 수지함유율을 가지고 있고, 더 높은 수지함유율은 더 높은 CTE 값과 더 낮은 탄성계수(modulus)에 해당한다.

탄성계수 계산의 예

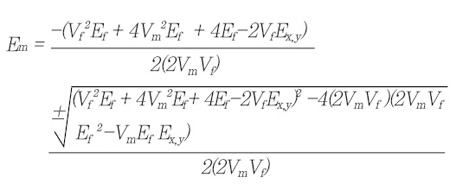

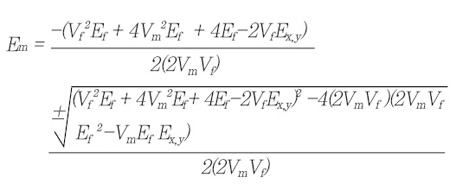

수지만의 탄성계수를 계산하고 Glass 함유물에 해당하는 탄성계수를 다시 계산해라. FR-4 보드는 X와 Y 방향의 섬유(Fibers)가 있다. 절반의 섬유는 X 방향에, 나머지 절반은 Y 방향이라고 가정하고 Ex 또는 Ey를 다음 공식을 사용해 계산한다.

다음은 아래 공식을 사용해 Em를 계산하고 양수값의 Em을 솔루션으로 고려한다.

Glass 스타일 효과

Glass 스타일 효과

수지 함유율이 증가하면 탄성계수는 감소한다. 반면, 수지함유율이 증가하면 CTE가 증가한다. 구리 함유율 역시 PCB 속성에 중요한 역할을 한다. 이들 값들이 솔더 접점 피로예측에 사용될 수 있다. 그림 3은 Glass 스타일에 따라 수지함유율이 어떻게 변하는지 보여준다.

솔더 합금과 결정(grain) 구조

솔더 조인트는 꽤 복잡한 구조로 되어 있다. 솔더 조인트는 PCB 표면에 있는 베이스메탈, 솔더와 PCB 베이스메탈 간 금속간 화합물(intermetallic compound, IMC), 그리고 IMC 형성으로 인해 감소한 솔더층으로 구성되어 있다. 그 다음, 솔더 결정 덩어리 구조, IMC 형성으로 감소한 솔더층, 솔더와 부품 베이스메탈 사이의 IMC 고형 솔루션, 그리고 부품 종단에 있는 베이스메탈이 있다.

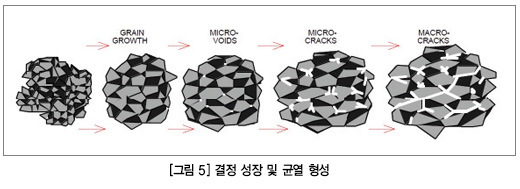

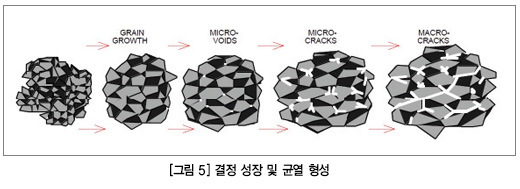

솔더 조인트의 잔여 스트레스는 크리프(creep)로 인해서 시간이 흐르면 완화된다. 솔더 속에서 CTE 불일치로 인해 생긴 스트레스는 더 높은 온도에서 더 빠르게 결정 성장에 기여한다. 결정 성장은 마이크로 보이드(void)를 형성하게 된다. 마이크로 보이드는 마이크로 균열(crack)로 이어지고, 결국 매크로 균열로 발전한다. 그림 5가 이 발전 단계를 보여준다.

여러 유형의 부품 리드 구성을 전자기기에서 볼 수 있다. 비준수, 준수, 초과 준수형 리드를 가진 부품들이 있다. 리드가 없는 부품들 또한 있는데, 이것들은 필릿(fillet)을 가지거나 그렇지 않을 수 있다. 필릿이 첨가된 리드 없는 부품으로서는 칩 저항기, 칩 커패시터, Metal Electrode Face (MELFs) 부품, 리드 없는 칩 캐리어가 있다. 필릿이 없는 리드 없는 부품은 Flip-Chip C4(Controlled Collapse Chip Connection) “범프(bump)”, BGA C5 (Controlled Collapse Chip Carrier Connection) “볼(Ball)”과 CGA (Column Grid Array) “기둥(Column)”을 포함한다.

다른 표면실장 솔더 부착 유형은 상당히 다른 고장 모드를 가질 수 있다. BGA는 균일하게 분산된 부하를 가지는 반면, 칩 부품과 리드를 가진 부품은 부하기 균일하게 분산되지 않는다. 이런 점이 매크로-균열이나 국부적인 결정 성장성 마이크로-균열로 발전될 수 있다.

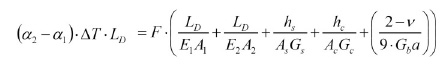

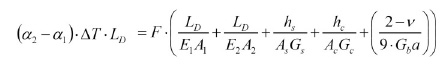

수정 Engelmaier 솔더 피로 모델은 에너지 기반의 피로를 사용하는 부분-경험적 분석예측 접근법이다. 첫째로, 아래의 공식을 사용해서 변형 범위 (Δg)를 결정한다.

조건:

ㆍ C는 교정 계수, α는 CTE, h는 솔더 조인트 높이

ㆍ C는 활성화 에너지, 온도 및 유지시간의 함수

ㆍ LD = 대각선 거리

ㆍΔα = a2-a1

ㆍΔT = 온도 사이클

ㆍ hs 기본 설정값은 0.1016 mm(5 mils)

다음으로 솔더 조인트에 적용된 전단력을 결정한다.

여기서 F는 전단력, LD 길이, E 탄성계수, A 넓이, h 솔더 두께, G 전단계수, 그리고 a가 접합부 패드의 가장자리 길이이다. 작은 첨자는 1이 컴포넌트, 2가 보드, s가 솔더 조인트, c는 접합 패드, b는 보드이다. 이 모델은 기초부 견고성과 전단 및 축부하 모두를 고려한다. 리드가 있는 모델들은 리드 견고성을 포함한다.

솔더 조인트로 소멸된 변형 에너지를 결정한다.

Amkor 사의 A. Syed가 개발한 에너지 기반의 SAC 피로 모델을 사용해서 고장까지 사이클 (N50)을 계산한다.

에너지 기반 SnPb(주석납) 피로 모델을 사용해서 고장까지 사이클 (N50)을 계산한다.

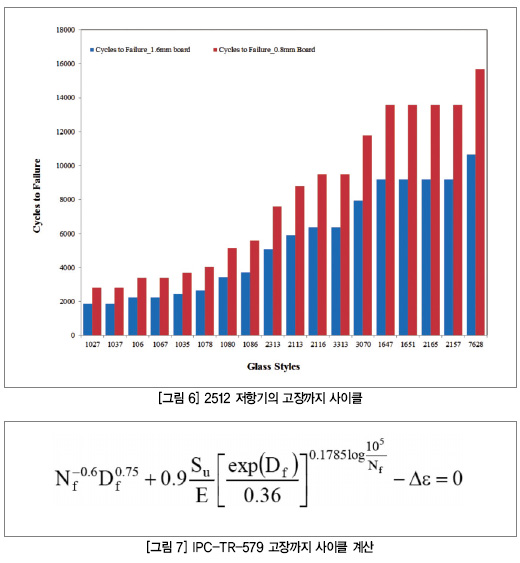

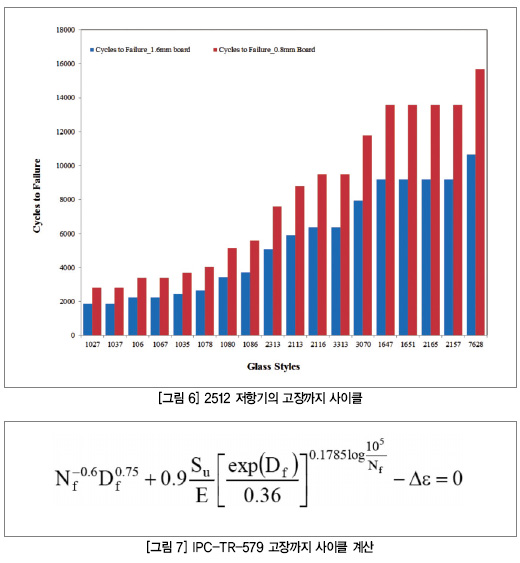

그림 6은 Alumina와 유사한 낮은 CTE 값(5.6 ppm/℃)을 가진 2512 저항기의 피로 계산을 나타낸다. 두 가지 보드 두께 1.6 mm와 0.8 mm를 상대로 고장까지 사이클이 계산되었다. 0.8 mm 두께의 보드가 성능이 나았다. 이 도표는 왜 몇몇 부품 제조업체들이 얇은 라미네이트를 테스트하는지 보여준다.

솔더 합금: SnPb, 무연합금들, SAC

솔더 합금: SnPb, 무연합금들, SAC

주석납 솔더는 일반적으로 SAC 솔더보다 높은 스트레스가 있는 열 사이클링 조건에서 성능이 더 우수하다. 그러나 유해물질사용제한규제(Reduction of Hazardous Sub-

stances regulations, RoHS)의 시행으로 대부분 고성능 부품들은 무연인 SAC 솔더 합금으로 제조된다. SAC 합금은 보통의 열 사이클에서 더 성능이 우수한 경향이 있다.

주석납은 크리스털, 오실레이터, 저항기 네트워크, SMT 저항기 및 세라믹 BGA를 포함해서 리드 없는 세라믹 부품, 리드 없는 세라믹 칩 캐리어 상에서 무연납의 성능을 초과한다. 이런 점은 특히 -40 ~ 125 ℃ 또는 -55 ~ 125 ℃와 같은 열악한 온도 사이클에서 특히 잘 적용된다.

도금된 스루홀(Plated Through Hole, PTH) 피로

PCB의 z 방향의 팽창/수축은 x-y 평면에서 보다 더 크다. 유리섬유(Glass Fibers)는 x-y 평면으로는 보드를 제약하나 두께 방향으로는 아니다. 결과적으로 구리 속의 비아 배럴에 스트레스가 쌓이며 배럴의 중앙 근방에 결국 균열이 발생한다.

PWB 속의 소규모 직경(< 20mil) 도금 스루홀에 대한 IPC-TR-579 라운드로빈(Round Robin) 신뢰성 평가 활동이 IPC에 의해 시작되었고 1988년에 출판되었다. 그 목적은 충분한 신뢰성을 확정하고 다른 테스트 절차들을 벤치마크하며 하나의 모델을 개발하기 위해 PTH 설계와 도금의 영향에 대한 평가를 하는 것이었다.

모델을 사용해서 고장까지 사이클을 예상하는 것은 다단계의 계산 과정이 요구된다. 첫째로, 적용된 스트레스를 결정한다(σ). 모델은 항복강도(Sy)보다 낮을 때는 완벽한 탄성 변형이라고 가정하고 항복강도보다 높으면 선형의 스트레스-변형 관계에 따른다고 가정한다. 다음은 변형 범위(Δε)를 결정하며, 유효 변형 범위(Δεeff)는 IPC-TR-579 교정 상수를 사용해 계산한다. 여기서:

ㆍ 변형 분포 계수, Kd (2.5-5.0), 바람직한 추천값 2.5

ㆍ 품질지수, KQ (0-10), 몇몇 기업들은 KQ를 5로 가정.

ㆍ 특별(Extraordinary) (KQ = 10)

ㆍ 탁월(Superior) (KQ = 8.7)

ㆍ 우수(Good) (KQ = 6.7)

ㆍ 보통(Marginal) (KQ = 4.8)

ㆍ 부족(Poor) (KQ = 3.5)

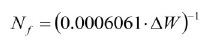

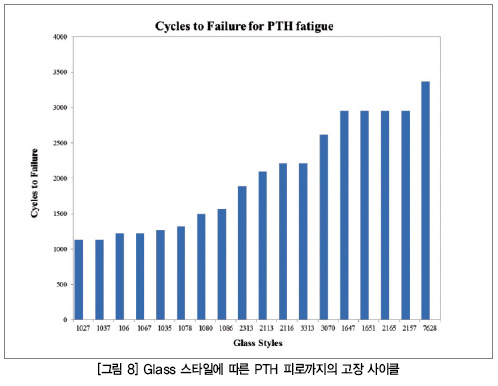

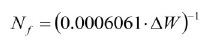

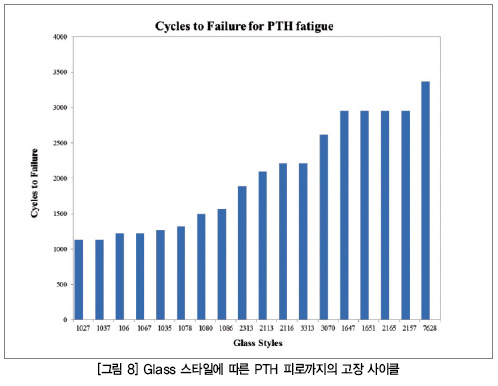

마지막으로, 그림 7에서 제시한 공식을 사용해서 고장까지 사이클 수(Nf)를 반복 계산한다. 이 계산값은 두 개의 주요 도금 속성인 Df와 Su에 의존한다. Df는 연장률이고 약 30%정도라고 가정한다. Su는 인장강도(tensile strength)이고 약 40,000 PSI라고 가정한다.

IPC-TR-579 평가

IPC-TR-579 모델의 장점은 간단 명료한 계산으로 분석적이며, 테스트로 통해 검증되었고, 디자인과 재질 파라미터의 상대적인 영향에 대한 지침을 제공한다는 점이다. 이 모델의 단점은 검증된 자료가 이미 18년이 지났다는 점이다. 이것으로는 수명을 늘리는 경향이 있는 복잡한 기하학적 구조를 평가할 수 없으며 복수의 온도 사이클 효과를 판단하기도 어렵다. 이 모델은 또한 항복점 이상에서 선형의 스트레스-변형 관계를 포함한 간단한 가정을 사용한다. 마지막으로 이 모델은 비아 필(Via Fill)의 효과를 산정할 수 없고 골절 균열(Knee cracking)이나 벽과 패드 분리(Wall to Pad Separation)와 같은 다른 고장 모드를 고려할 수 없다.

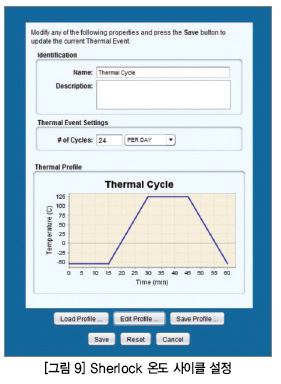

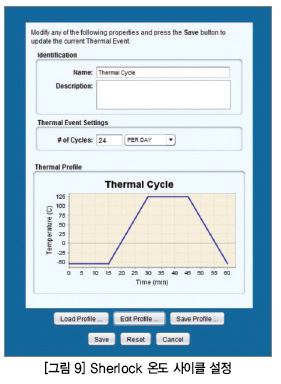

PTH 피로 수명을 개선하기 위해서는 적절한 특성을 가진 라미네이트를 선택해야 한다. 라미네이트 CTEz 값이 구리의 CTE 값에 더 근접할수록 더욱 바람직하다. 라미네이트의 CTE는 Glass 스타일과 수지 시스템의 선택으로 영향을 받는다. 항상 그렇듯이, 트레이드오프가 있다. 높은 유리 함유율은 CTE를 향상시키나 라미네이트에 드릴을 하기가 어려워진다. 드릴을 하기가 어려워진 라미네이트는 더 많은 구멍 벽의 결함을 가져오게 된다. 구리의 연성 또한 중요하다. 그림 8은 PTH 피로 수명에 미치는 glass 스타일 영향을 보여준다. Glass 섬유 함유율은 좌에서 우로 증가되며 높아지는 피로수명과 일치한다.

몇 가지 예외가 있다. 언더필(underfills), 포팅 화합물(potting compounds), 두꺼운 컨포멀 코팅(conformal coatings)의 사용은 열 사이클 하에서의 고장 발생에 지대한 영향을 미치기 때문에 신중하게 선택해야 한다. 충격에 대한 견고성을 증대시키는 언더필은 열 사이클링의 견고성을 개선하지 못하는 경향이 있다.

프로세스가 신중하게 검증되지 않는 이상, 컨포멀 코팅이 PCB와 부품 사이에 적용되면 안 된다. 코팅이 부품 아래로 스며들면 굳으면서 생기는 팽창으로 실제 솔더 조인트에 균열을 내거나 스트레스를 줄 수 있다. 그리고 항상 유리전이온도에서 재료를 사용하는 것을 피해야 한다. 재질 속성이 크게 바뀌고 문제가 일어나는 경향이 있기 때문이다.

Sherlock과 온도사이클링

Sherlock ADA™(Automated Design Analysis™)는 DfR Solutions 사가 개발한 소프트웨어 도구이다. 이 소프트웨어는 전자기기 산업분야의 디자인 및 신뢰성 엔지니어들은 물론 관리자들도 사용할 수 있도록 만들어졌다. Sherlock은 회로 카드 어셈블리 단계의 분석을 실행하며 제품 신뢰성을 예측하고 검증한다.

Sherlock을 사용한 열 피로 예측

Sherlock 분석은 다음 4가지 주 요소가 있다:

1. 설계 내용 취합(Design Capture )-모델링 소프트웨어와 계산 도구에 산업계 표준 형태로 된 입력 값들을 제공한다.

2. 수명-사이클 특성화(Life-Cycle Characterization)-신뢰성 목표치를 정의하고 제품 작동이 요구되는 기대 환경 및 사용조건들을 정의한다.

3. 스트레스 변형의 시각적 평가(Load Transformation)-회로 보드 전체에 가해진 환경 및 동작 부하를 개별 부품으로 변환하고 배분하는 계산을 자동적으로 수행한다.

4. PoF 내구성 시뮬레이션/신뢰성 평가 & 리스크 분석(Durability Simulation/Reliability Analysis & Risk Assessment)-PCBA 모델에 PoF 알고리즘을 적용함으로써 수명 예측과 신뢰성 분포를 계산하고 리스크에 우선순위를 정하는 과정으로, 설계 및 응용환경에 맞추어진 내구성 시뮬레이션을 실행한다.

Sherlock의 도금된 스루홀 피로 분석

Sherlock의 도금된 스루홀 피로 분석

도금된 스루홀(PTHs) 또는 도금된 스루비아(PTV)는 전도성 금속(보통은 구리)으로 전기화학적 도금이 된 다층 PCB에 뚫어진 구멍이다. 이런 도금 구멍들은 층 간에 전기적인 연결을 제공한다. 이런 도금 구멍들은 PCB의 위와 아래 부분에 있는 고리 모양의 링에 야금학적으로 연결되어 있기 때문에, 리벳처럼 작용하고 PCB에 제한을 가한다. 이 제한으로 PCB가 온도 변화를 경험할 때에는 PTH에 스트레스가 된다. 시간이 경과함에 따라 PTH에는 피로가 생기고 결국 균열 전파(crack propagation)로 인해서 고장이 난다. PTH 피로는 여러 가지 원인에 의해 생기게 되는 데 온도 범위, PTH 지름, PTH 구리 도금 두께, 구리 도금 재료 속성, 회로 보드 두께, 회로 보드 면외 재료 속성, 그리고 구리 도금의 품질 등을 포함한다. Sherlock은 IPC-TR-579(PWB에 있는 작은 직경 도금 스루홀에 대한 라운드로빈 신뢰성 평가)에 명시된 산업계통용 모델을 사용해서 고장까지의 시간을 계산한다. 열 사이클링의 영향 하에 있는 PTH 수명 계산은 스트레스 계산, 변형 범위 계산, 반복적 수명 결정의 3단계 과정으로 이루어진다.

PTH 피로 분석 모듈은 분석 계산을 하기 위해 수명 사이클 신뢰성 목표, 모든 PTH와 비아의 크기/위치, 회로 보드 기계적 특성(스택업 데이터), 그리고 열 이벤트 및 관련 열지도(thermal maps)를 사용한다.

Sherlock의 솔더 피로 분석

Sherlock의 솔더 피로 분석

솔더 조인트는 전자기기 부품과 PCB 사이의 전기적, 열적, 기계적 연결을 제공한다. 온도 변화 중에 부품과 회로기판은 열팽창계수(CTE) 값의 차이로 인해 서로 다른 양만큼 팽창하거나 수축한다. 팽창과 수축의 크기 차이는 2단계 솔더 조인트를 전단 부하에 노출시킨다. 매일 주기로 전원을 껐다 켰다하는 것과 같은 식의 반복된 온도 변화에 노출되면 솔더 덩어리에 손상이 올 수 있다. 각 추가 온도 사이클마다 이 손상이 쌓여서 균열 전파를 초래하고 언젠가는 솔더 조인트의 고장으로 이어진다.

열기계적 솔더 조인트 피로는 최고 온도, 최저 온도, 최고 온도 유지 시간(dwell time), 부품 디자인, 부품 재질 속성, 솔더 조인트 기하학적 구조, 솔더 조인트 재료, 회로 보드 두께, 그리고 회로 보드 평면 내 재질 속성에 영향을 받는다. Sherlock은 변형 에너지를 사용해서 고장까지 시간을 계산하는 데, 이것은 적용된 힘, 변형 범위, 그리고 원인이 된 변형 에너지로부터 고장에 이르는 사이클을 추정하여 만든다.

솔더 피로 분석 모듈은 분석 계산을 위해 수명 사이클 신뢰성 목표, 부품 리스트, 회로기판 기계적 속성(스택업 데이터), 부품 크기 및 위치, 솔더 속성, 열적 이벤트와 관련 열지도를 사용한다.

중점이 온도 사이클링 성능이기 때문에 Sherlock의 열적 기능들이 관심사이다.

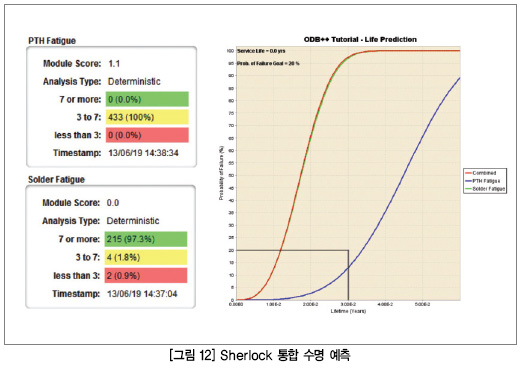

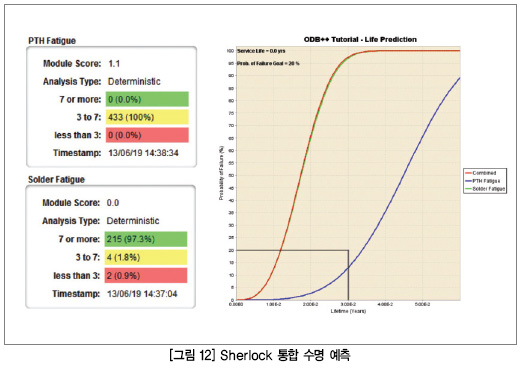

열 사이클 추가

Sherlock은 매우 유연하기에 여러 가지 열 사이클링 환경에 완벽하게 맞출 수 있다. 파라미터는 직접 입력될 수도 있고 저장된 프로파일에서 불러올 수 있고, 또는 현재의 프로파일에서 복사하거나 붙여 넣을 수 있다. 그림 9와 10은 Sherlock에서 -55 ~ 125 ℃ 범위의 한 시간 사이클이 지정된 것을 나타낸다.

모델의 예측 정확성을 개선하기 위해서 실제 테스트에서 얻어진 열 이미지들(thermal images) 또한 Sherlock으로 받아들일 수 있다.

PoF라는 전문적 접근법을 사용하는 Sherlock은 솔더 피로 계산을 부품 하나하나에 대하여 수행한다. 각각의 부품은 열지도에 따라 적용된 온도를 가지게 된다. 보드는 솔더 피로고장 가능성에 대한 스코어카드가 부여된다. 그림 11은 Sherlock 솔더 피로 분석의 예를 나타낸다.

예측 곡선들도 생성된다. 그림 12는 PTH와 솔더 조인트 피로에 대한 통합 신뢰성 예측 분석을 나타낸다. ES

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>