SoC 검증은 기존의 로직 시뮬레이션을 압도하고 있음에도 그 속도를 높이기 위해 세 가지 하드웨어적인 옵션을 널리 사용한다.

SoC 검증은 기존의 로직 시뮬레이션을 압도하고 있음에도 그 속도를 높이기 위해 세 가지 하드웨어적인 옵션을 널리 사용한다.

현재 일반적으로 사용하고 있는 하드웨어 옵션 세 가지는 FPGA 프로토타이핑, 검증 IP를 이용하여 가속되는 시뮬레이션, 그리고 인서킷 에뮬레이션(ICE)이다. 이들은 일부 시나리오에는 적합하지만 끊임없이 진화하면서 멀티프로세서, 멀티 프로토콜에 소프트웨어 비중이 높은 SoC를 개발하는 팀에게는 상당히 불리한 면들이 있다.

FPGA 프로토타이핑은 기존에 있던 수정되지 않은 하드웨어에 대한 소프트웨어 스핀에는 문제가 없지만, 일정 수준으로 설계 마무리가 이루어지고 있는 하드웨어에는 적합하지 않다. 이는 FPGA 프로토타이핑이 설계 프로세스에 동시병행성을 전혀 제공하지 않기 때문이다. FPGA 보드들은 하드웨어가 완성되기 전에는 소프트웨어 팀에서 사용할 수 없으며, 문제가 발생할 때마다 재 컴파일 하는 데 몇 시간이 아니라 며칠이 걸릴 수 있다. 게다가 수백만 게이트급의 SoC를 여러 개의 FPGA에 나누어 사용하는 것 자체가 문제를 자초하는 것이나 다름없다. 이 때문에 FPGA 프로토타이핑이 저렴한 옵션처럼 보일지는 몰라도 하드웨어 디버깅이 아직 진행중인 SoC에 사용하기에는 길고도 위험한 프로세스인 것이다.

심층 테스트 시퀀스, 코드 커버리지, 단언문 기반의 검증, 오류 처리, 프로토콜 점검 등을 이용하는 가속된 시뮬레이션은 새로 개발된 ASIC이나 핵심적인 IP 부분에 아무런 버그도 없음을 검증해야 하는 하드웨어 개발자들에게 적합하다. 그러나 다수의 기존 하드웨어 블록들이 함께 동작해야만 하고 이를 소프트웨어로 구동해야 하는 SoC를 검증하고자 할 때는 소프트웨어팀 전체가 이용할 수 있는 검증 방법이 필요하다. 임베디드 프로세서가 소프트웨어를 포함하는 프로세스가 되기 위해서는 테스트가 필요하다.

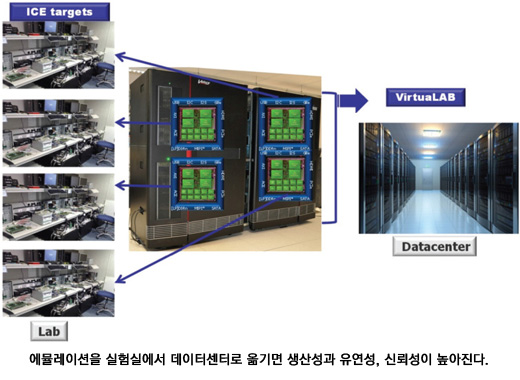

2012년까지는 인서킷 에뮬레이션(ICE)이 소프트웨어-하드웨어 동시 검증을 위한 유일한 선택이었으며, 하드웨어는 프로토타입 하드웨어가 나올 때까지는 정기적인 변경의 대상이었다. ICE는 단일 사이트에 기반을 두면서 실험실에 대해 완전하고도 개인적인 통제력을 갖는 비교적 작은 프로젝트 팀에, 그리고 디자인이 다수의 상이한 하드웨어 타깃 인터페이스들을 수반하지 않는 경우에 적합하다. 그러나 이것은 유연성, 신뢰성 및 투자수익 면에서 심각한 단점이 있다. 타깃 주변장치나 호스트의 모델들이 실험실의 에뮬레이터에 케이블 연결된 외부 하드웨어 상에서 동작하고 있어야만 하기 때문이다.

케이블과 외부 하드웨어 장치들은 복잡성과 잠재적인 비신뢰성의 원인이 되며 에뮬레이션의 이용도 제한하기 때문에 실험실 장비는 병목 지대가 되고 만다. ICE가 서로 멀리 떨어진 곳에서 다수의 프로젝트에 참여하고 있는 여러 하드웨어 및 소프트웨어 엔지니어 팀들에게 에뮬레이션을 이용할 수 있도록 하는 유일한 길은 여러 에뮬레이터 상에서 동일한 프로젝트 설정을 실행하는 것뿐이다. 그러나 이는 비용이 많이 들고 전력 소모가 크며 관리하기도 복잡할 것이다.

다행히도, 이제는 “버추얼랩(가상 실험실)” 에뮬레이션 환경을 사용하는 네 번째 옵션을 사용할 수 있게 됐다. 버추얼랩은 복잡한 SoC 개발에서 흔히 직면하게 되는 대규모 팀, 다분야, 비균일 집적(rolling integration)과 같은 문제들에 보다 적합하다. 이 새로운 접근방법은 SoC 디자인을 개발하고 있던 팀들이 에뮬레이션 랩을 가상화 할 길은 없을까 고민하기 시작하면서 등장하게 됐다. 어지럽게 널린 실험실 케이블 없이, 그리고 다수의 ICE 장치들을 마치 RAID처럼 운영하는 것보다 낮은 비용으로 자신들의 소프트웨어 엔지니어들 모두가 에뮬레이터를 융통성 있게 액세스 할 수 있도록 말이다. 분명한 것은 이 문제를 해결하기 위해서는 더 많은 검증 프로세스가 소프트웨어로 이루어져야 한다는 것이었다.

십 년 넘게 축적해온 통합 모델링 연구 경험을 통해 멘토 그래픽스는 타깃 주변장치의 모델을 실행하는 외부 하드웨어 장치에 의존하지 않고, 그 대신 에뮬레이터를 일반 데이터센터에 두고 이를 그저 평범한 컴퓨팅 자산처럼 취급할 수 있도록 해줄 새로운 에뮬레이션 접근방법을 2012년 발표할 수 있었다.

이 새로운 에뮬레이션 접근방법은 설계자들이 자신들의 타깃 프로토콜을 에뮬레이터 상에 디자인과 함께 올려놓고 테스트 프로세스의 소프트웨어 측면을 PC로부터 구동할 수 있도록 해준다. 실제 타깃 OS와 드라이버 그리고 애플리케이션들은 이 PC의 가상 머신 내에서 안전하게 동작한다.

이 버추얼랩 솔루션은 하드웨어와 소프트웨어가 개발 초기 단계에 있으며 잦은 변경이 이루어질 경우 다른 접근방법들보다 SoC 검증에 보다 적합하다. 임베디드 프로세서와 다수의 주변 장치들 그리고 복잡한 소프트웨어 테스트 기능들을 갖는 수백만 게이트급의 디자인에 있어서 버추얼랩은 사용의 유연성과 생산성을 크게 향상시켜 준다.

버추얼랩은 기능적으로는 ICE와 동일하지만 더 많은 프로세스가 소프트웨어로 이루어진다. 이것은 PC나 워크스테이션으로부터 제어되고, ICE 솔루션에 사용되는 것과 동일한 하드웨어 정확 모델들이 공급되며, 엔지니어는 제대로 사전인증된 IP를 사용한다. 프로토콜 RTL 모델과 소프트웨어 스택, 애플리케이션들을 단지 에뮬레이터에 다운로드하는 것만으로 에뮬레이터는 SoC 검증 프로세스를 움직인다. 버추얼랩 접근방법도 ICE처럼 소프트웨어 엔지니어들이 RTL에 남아 있으면서도 하드웨어 디자인을 액세스할 수 있도록 해준다. 차이점은 이를 유연하게 해내며 다수의 셋업과 에뮬레이터 정지 시간이 필요 없다는 것이다.

하드웨어 엔지니어들의 경우에는 에뮬레이터를 실험실 밖으로 꺼내 데이터센터로 옮기면 케이블 뽑힘이나 핀 파손, 사용 가능한 핀의 결여로 인해 또는 멀리 떨어져 있는 실험실의 스탭이 외부 하드웨어 타깃들 간에 케이블을 교체해 주기를 밤새 기다리느라 정지 시간이 야기되던 일도 사라지게 된다. 버추얼랩 에뮬레이션을 사용하게 되면 엔지니어들은 더 이상 테스트를 수행하기 위해 맞춤형 타깃 보드에 의존할 필요가 없다.

소프트웨어 엔지니어들에게 있어서 버추얼랩은 실제 타깃 OS를 가상 머신에서 실행시키는 보다 안정되고 탄력적인 환경이다. 예를 들어 코드에서 아직 준비되지도 않은 메모리 부분을 어드레스 하더라도 하드웨어 크래시는 일어나지 않는다. PC는 계속 동작하며 단지 가상 머신만이 리부팅 될 뿐이다.

투자수익은 에뮬레이터의 액세스가 늘어남에 따라 함께 증가한다. 버추얼랩 환경에서 에뮬레이터는 여러 팀과 프로젝트, 지역들에서 사용할 수 있는 서버처럼 다뤄진다. 더 이상은 소수 특권층만이 사용할 수 있는 값비싼 기계가 아닌 것이다. 그 목표는 한 조직의 모든 프로젝트를 같은 시간에 진행하고 있는 모든 소프트웨어, 하드웨어 및 통합 엔지니어들이 에뮬레이션을 유연하게 항상 이용할 수 있도록 하는 것이다.

동시병행적 엔지니어링을 통해 투자수익과 품질, 생산성이 향상되기까지는 오랜 시일이 걸렸다. 버추얼랩 에뮬레이션은 SoC 검증이 실험실의 울타리를 벗어나게 함으로써 이러한 혜택들이 마침내 제공되는 검증 환경을 구현하고 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>