업계 직렬 인터페이스 표준 JESD204B를 통해 고속 데이터 컨버터와 FPGA 및 기타 장치 간의 디지털 입출력 수를 줄일 수 있다. 인터커넥트 수가 감소하므로 레이아웃은 단순해지고 필요한 폼팩터의 규모를 소형화할 수 있다. 이와 같은 이점은 무선 인프라스트럭처 송수신기, 소프트웨어 정의 무선 시스템, 의료 화상 시스템, 레이더 및 보안 통신 등 다양한 고속 데이터 컨버터 애플리케이션을 위해 중요한 의미를 지닌다.

글 | 조지 디니즈(George Diniz),

고속 데이터 컨버터 제품 라인 담당자

아나로그디바이스(ADI)

JESD204B

직렬 인터페이스용 JESD204A 산업 표준은 최신 광대역 데이터 컨버터와 타 시스템 IC 간의 인터커넥트 관련 문제를 효율적이고 경제적인 방식으로 해결할 목적으로 개발됐다. 그리고 이는 확장형 고속 시리얼 인터페이스를 활용해 데이터 컨버터와 FPGA(Field-Programmable Gate Array) 및 SoC(Systems-on-Chip) 등의 다른 장치 간의 디지털 입출력 수를 줄일 수 있는 인터페이스를 표준화하려는 노력에서 비롯됐다.

최근 추세를 보면 새로운 애플리케이션은 물론 기존 애플리케이션의 향상된 기능에 따라, 크게 강화된 샘플링 주파수 및 데이터 분석 기능을 갖춘 광대역 데이터 컨버터의 필요성이 점차 증가하고 있는 상황이다. 이와 같은 광대역 컨버터를 통한 데이터 전송은 중대한 설계상의 문제를 드러내기 마련인데, 이는 곧 기존 입출력 기술의 대역폭 제한으로 인해 컨버터 제품에 요구되는 핀 개수가 더욱 증가하기 때문이다. 그 결과 시스템 PCB 설계는 배선 집적도 면에서 한층 더 복잡해지게 됐다. 이 경우 전기적 잡음을 통제하면서 다수의 고속 디지털 신호를 전달하는 문제가 대두된다. 인터커넥트를 최소화하며 광대역 데이터 컨버터에 Gsps급 샘플링 주파수를 제공하는 기능을 통해 PCB 레이아웃 문제를 단순화하고 폼팩터 규모를 줄일 수 있는 동시에 전반적인 시스템 성능은 그대로 유지할 수 있다.

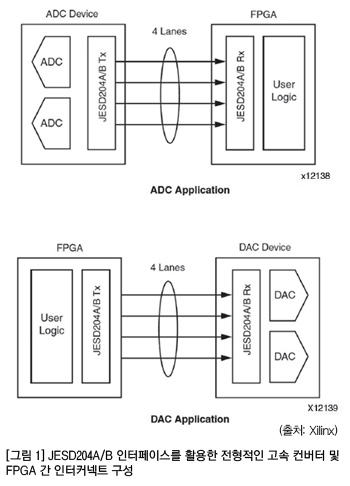

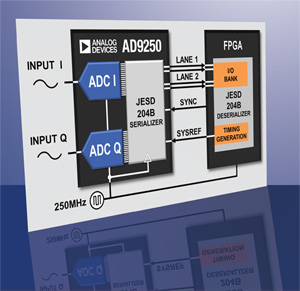

시장의 흐름은 주어진 시스템에서 계속적으로 더 많은 기능과 성능을 요구하는 동시에 데이터 처리 용량 또한 더욱 향상될 것을 요구하고 있다. 고속 A/D 컨버터 및 D/A 컨버터-FPGA 간 인터페이스로 인해 일부 시스템 OEM은 차세대의 데이터 집약적 요구사항을 충족하는데 있어서 일종의 한계를 지닐 수밖에 없었다. JESD204B 직렬 인터페이스 규격은 이처럼 중요한 데이터 링크를 지정해줌으로써 이와 같은 문제를 해결하도록 특별히 작성됐다. 그림 1은 JESD204A/B를 활용한 전형적인 고속 컨버터 및 FPGA 간 인터커넥트 구성을 보여준다.

이 글에서는 이와 같은 규격을 배치하도록 유도하는 일부 주요 종단 시스템 애플리케이션과 직렬 LVDS 및 JESD204B 간의 차이에 대해 다룬다.

JESD204B의 필요성을 촉진하는 애플리케이션

Wireless infrastructure transceivers

현대의 무선 인프라스트럭처 송수신기에 사용되는 LTE 같은 OFDM 기반 기술에서는 FPGA 또는 SoC 장치에 구현된 DSP 블록을 이용해 안테나 어레이 소자에서 개별 가입자의 송수신 장치로 전파를 생성하도록 한다. 각 어레이 소자가 작동할 때 송신 모드나 수신 모드에서 FPGA 및 데이터 컨버터 사이에 초당 수백 메가바이트의 데이터가 이동해야 할 수도 있다.

Software defined radios

무선 시스템으로부터 정의되는 최근의 소프트웨어는 작동 중에 재구성이 가능한 고급 변조 방식이 활용되며, 이는 채널 대역폭을 빠르게 증가시킬 수 있으므로 무선 데이터 속도가 대폭 향상된다. 안테나 경로 내 데이터 컨버터 인터페이스에 대한 FPGA는 효율화되고 필요 전력 및 핀 개수는 최소화됐으며, 이는 해당 성능에 있어서 중요한 역할을 담당한다. 소프트웨어 정의 무선 시스템 아키텍처는 GSM, EDGE, W-CDMA, LTE, CDMA2000, WiMAX, TD-SCDMA 등을 지원하는 멀티캐리어 및 다중 모드 무선 네트워크용 송수신기 인프라스트럭처에서 필수적인 부분을 차지한다.

Medical imaging system

초음파, CT(Computational Tomography: 컴퓨터 단층 촬영), 스캐너, MRI(Magnetic Resonance Imaging: 자기 공명 영상법) 등을 비롯한 의료 화상 시스템은 데이터 컨버터를 통해 FPGA 또는 DSP로 흐르는 다수의 데이터 채널을 생성한다. 입출력 수가 지속적으로 증가하면 FPGA와 컨버터의 핀을 서로 일치시키기 위해 인터포저를 활용해야 하고 PCB는 더욱 복잡해지므로 필요한 부품의 수도 그만큼 증가한다. 이 경우 고객 시스템은 더 많은 비용을 필요로 하고 구성은 더욱 복잡해지는데, 이 문제는 좀 더 효율적인 JESD204B 인터페이스로 해결할 수 있다.

레이더 및 보안 통신

최근에 고급 레이더 송수신기의 펄스 구조는 더욱 정교해지고 있으며, 이에 따라 신호 대역폭은 1 GHz 이상으로 높아지고 있다. 최신의 AESA

(Active Electronically Scaled Array) 레이더 시스템에는 수천 개의 인터페이스 소자를 가진다. 들어오는 데이터 스트림을 처리하고 나가는 데이터 스트림을 생성하는 FPGA 또는 DSP에 어레이 소자 데이터 컨버터를 연결하려면 고대역폭 SERDES 기반 직렬 인터페이스가 필요하다.

직렬 LVDS 및 JESD204B 상호 비교

직렬 LVDS와 JESD204B 인터페이스 사이에서의 선택

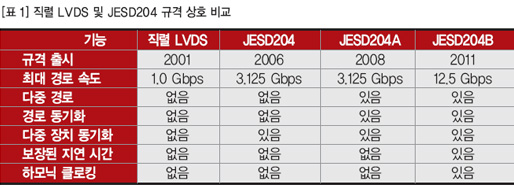

LVDS 또는 다양한 버전의 JESD204 직렬 인터페이스 규격을 채택한 컨버터 제품들을 올바르게 선택하려면 각 인터페이스의 기능을 면밀히 비교하는 것이 좋다. 표 1은 이러한 비교 내용을 간단히 도표화한 것이다. SERDES 수준에서 LVDS 및 JESD204 간의 주목할 만한 차이는 경로 데이터 속도이며, JESD204는 LVDS와 비교해볼 때 3배 이상 더 빠른 경로당 직렬 링크 속도를 지원한다. 다중 장치 동기화, 보장된 지연 시간 및 하모닉 클로킹 등 고급 수준 기능의 차원에서 고려하면, JESD204B는 해당 기능을 지원하는 유일한 인터페이스라고 할 수 있다. 모든 경로 및 채널에 걸쳐 보장된 지연 시간에 민감한 광대역폭 다중 채널 컨버터가 필요한 시스템에서는 LVDS 또는 병렬 CMOS를 효과적으로 활용할 수 없다.

LVDS

LVDS(Low-Voltage Differential Signaling)는 데이터 컨버터를 FPGA 또는 DSP와 연결하는 기존의 방식이다. LVDS는 1994년에 기존의 RS-422 및 RS-485 차등 전송 표준보다 더 높은 대역폭과 더 낮은 전력 손실을 지원할 목적으로 도입됐다. 1995년에 LVDS는 TIA/EIA-644의 공개와 함께 표준화됐다. LVDS는 1990년대 후반부터 널리 사용되기 시작했으며 이 표준은 2001년에 TIA/EIA-644-A의 공개와 함께 개정됐다.

LVDS는 고속 데이터 송신을 위해 저전압 진폭과 함께 차등 신호를 활용한다. 송신기는 일반적으로 논리 레벨과 일치하는 양극성을 띤 ±3.5 mA를 공급하여 100 Ω 저항을 통해 전송하며, 이에 따라 수신기는 ±350 mV 전압 진폭을 생성한다. 상시 전류는 서로 다른 방향에서 전달되어 여러 논리 1과 0을 생성한다. 싱글엔드형 기술에서 트랜지스터가 켜지고 꺼질 때 가끔 발생하는 동시적 전환 잡음 극파와 잠재적 전자기 방해는 LVDS의 상시적 특성으로 인해 쉽게 제거된다. 또한 LVDS의 차등적 특성 덕분에 공통 모드의 잡음 원인에 대한 면역성은 크게 높아진다. TIA/

EIA-644-A 표준에서는 최대 655 Mbps의 데이터 속도를 권장하며 이는 이상적인 송신 매체에서 1.9 Gbps 이상의 속도가 가능하더라도 마찬가지로 적용된다.

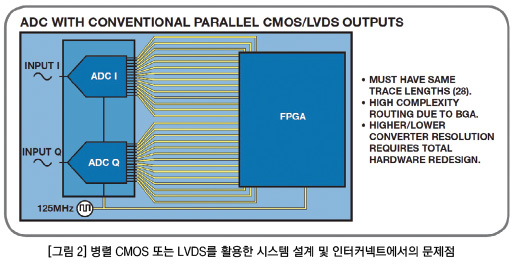

FPGA 또는 DSP와 데이터 컨버터 간의 데이터 채널의 수와 속도가 크게 향상됨에 따라, 특히 앞서 설명된 애플리케이션에서 LVDS 인터페이스에 몇 가지 문제가 대두됐다(그림 2 참조). 차등형 LVDS 통신선의 대역폭은 실제 환경에서 약 1.0 Gbps로 제한된다. 현재 보급된 여러 애플리케이션에서 이 문제로 인해 상당한 수의 고대역폭 PCB 인터커넥트가 필요해지며 각 연결은 잠재적인 장애 지점이 된다. 또한 수많은 연결과 배선으로 인해 PCB 또는 전체 폼팩터는 더욱 복잡해지므로 설계 및 제조 관련 비용이 상승한다. 데이터 컨버터 인터페이스는 항상 충분한 대역폭이 요구되는 일부 애플리케이션에 필요한 시스템 성능을 구현하는 데 있어서 제한 요인으로 작용할 수 있다.

JESD204B

JESD204 데이터 컨버터 직렬 인터페이스 표준은 JEDEC 반도체기술협회 인터페이스 기술에 관한 JC-16 위원회(JEDEC Solid State Technology Association JC-16 Committee on Interface Technology)에서 고속 데이터 컨버터와 기타 장치 간의 대역폭을 늘리고 디지털 입출력 수를 줄이기 위해 데이터 컨버터에 고속 직렬 인터페이스를 제공할 목적으로 작성했다. 이 표준은 IBM에서 개발한 8b/10b 인코딩 기술을 기반으로 작성됐으며, 이 인코딩 기술은 프레임 클록과 데이터 클록의 필요성을 없앰으로써 더욱 빠른 속도로 단일 회선 페어 통신을 지원한다.

2006년에 JEDEC에서는 단일 3.125 Gbps 데이터 경로를 위한 JESD204 규격을 공개했다.JESD204 인터페이스는 자체 동기식이므로 클록 편차를 방지하기 위해 PCB 유선의 길이를 조정할 필요가 없어진다. JESD204는 여러 FPGA에서 제공되는 SerDes 포트를 활용하므로 범용 입출력 포트는 다른 용도로 활용할 수 있다.

2008년에 공개된 JESD204A에는 다중 시간 정렬 데이터 경로 및 경로 동기화에 대한 지원이 추가됐다. 이러한 개선으로 향상된 대역폭 데이터 컨버터와 다중 동기화 데이터 컨버터 채널을 사용할 수 있게 됐으며, 이는 특히 무선 전화 기지국에 활용되는 무선 인프라스트럭처 송수신기에 중요하다. JESD204A에서는 또한 의료 화상 시스템과 같이 많은 수의 ADC가 사용되는 장치에 도움이 되는 다중 장치 동기화 기능을 지원한다.

이 규격의 세 번째 개정판인 JESD204B에서 최대 경로 속도는 12.5 Gbps로 향상된다. 또한 JESD204B에서 수신기와 송신기 사이에서 동기화 상태를 전송할 수 있도록 지연 시간의 제한을 해주는 기능을 추가한다. 또한 JESD204B에서 도입된 하모닉 클로킹을 활용하면 보장된 위상 조정을 통해 고속 데이터 컨버터 클록을 저속 입력 클록에서 유도해낼 수 있다.

요약

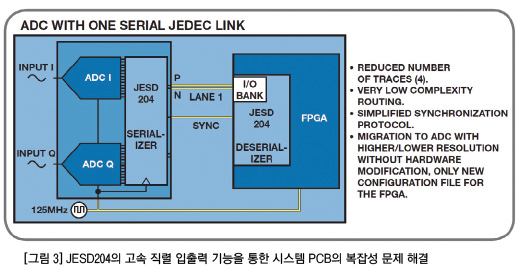

JESD204B 업계 직렬 인터페이스 표준을 통해 고속 데이터 컨버터와 FPGA 및 기타 장치 간의 디지털 입출력 수를 줄일 수 있다. 인터커넥트 수가 감소하므로 레이아웃은 단순해지고 필요한 폼팩터의 규모를 소형화할 수 있다(그림 3 참조). 이와 같은 이점은 무선 인프라스트럭처 송수신기, 소프트웨어 정의 무선 시스템, 의료 화상 시스템, 레이더 및 보안 통신 등 다양한 고속 데이터 컨버터 애플리케이션을 위해 중요한 의미를 지닌다. 아날로그 장치는 JESD204 표준 위원회에 속하는 원래의 구성 항목이며, 이와 동시에 ADI는 포괄적인 제품 로드맵 오퍼링과 함께 표준 데이터 컨버터 기술 및 도구들을 개발했다. ADI는 최첨단 데이터 컨버터 기술과 JESD204A/B 인터페이스가 통합된 제품을 제공함으로써, 엔지니어들이 자체의 시스템 설계 문제를 해결하는 한편 이러한 중차대한 인터페이스 상의 돌파구를 마련할 수 있길 기대한다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>