.jpg)

무선 전력 전송에서 GaN HEMT의 장점 알아보기

GaN 기술은 가장 가까운 대안인 실리콘에 비해 많은 고유한 특징을 갖고 있다. 이 글에서는 무선 충전 애플리케이션에 사용되는 class-D 무선 주파수(RF) 전력 증폭기에서 GaN 전력 소자의 장점을 소개하고, 특히 GaN HEMT 디바이스가 MOSFET에 대해 갖는 장점에 대해 중점적으로 살펴보기로 한다.

휴대용 기기를 위한 무선 충전은 기존의 충전기 어댑터와 관련 케이블, 커넥터의 필요성을 없애준다. 무선 충전 기술은 등장한지 꽤 되었지만 최근에서야 스마트폰과 태블릿, 노트북에 도입되고 있으며, 앞으로 몇 년 내에 광범위하게 채택될 것으로 보인다.

GaN 기술은 가장 가까운 대안인 실리콘에 비해 많은 고유한 특징을 갖고 있다. 이 글에서는 무선 충전 애플리케이션에 사용되는 class-D 무선 주파수(RF) 전력 증폭기에서 GaN 전력 소자의 장점을 소개하고, 특히 AFA(Air Fuel Alliance)의 기준 규격에 따라 무선 전력 전송을 위해 제안된 2가지 전력 증폭기 토폴로지에서 GaN HEMT 디바이스가 MOSFET에 대해 갖는 장점에 대해 중점적으로 살펴보기로 한다.

공진 방식 무선 충전과 AFA 표준

현재 일부 스마트폰과 태블릿 및 기타 휴대용 기기에서 사용할 수 있는 무선 충전 시스템은 대부분 100~300kHz 범위의 주파수에서 유도 결합에 의해 동작하는 자기 유도(Qi) 표준을 기반으로 한다. 이 시스템은 한 대의 기기만 충전할 수 있고, 또 특정 방향으로 충전기에 매우 가까이 놓아야 한다. 소비자 시장에서 전력 전송을 위한 무선 애플리케이션에 대한 관심이 높아지면서 공진 결합의 이점을 이용하고자 하는 전력 변환 설계자들에게 Class-D와 같은 다른 토폴로지가 공식적으로 주목받고 있다.

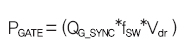

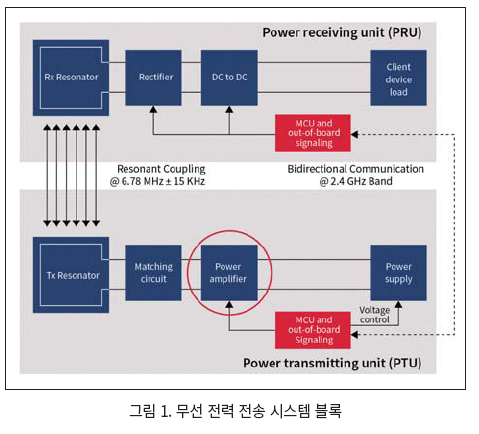

이 토폴로지는 새로운 것은 아니며, “증폭기”라는 용어가 이를 설명하는 데 광범위하게 사용되는 RF 애플리케이션에서 이미 성공적으로 사용되고 있다. 그림 1에서 보듯이 무선 충전 시스템의 송신부에 사용되는 이 토폴로지의 주요 매력은 MHz 범위의 동작 주파수에서 높은 효율을 달성할 수 있다는 점이다.

AFA(Air Fuel Alliance, 2015년에 결성)는 ISM(industrial, scientific and medical) 주파수 대역의 6.78MHz에서 공진 유도 결합을 사용하는 스위칭 방법을 제안한다. 이 방식은 높은 Q 값을 갖는 공진기가 주변 지역의 훨씬 약한 자기장을 사용하여 훨씬 먼 거리에 걸쳐 전력을 전송할 수 있다. 또한 동시에 여러 대의 기기를 아무 방향으로나 놓아도 충전이 가능하다.

패러데이의 법칙에 의하면 전위차는 코일로 감싼 자기 선속의 변화로 코일에 의해 발생한다. 무선 전력 전송에서 RF 전력 증폭기는 튜닝된 회로에서 코일로 구성된 PTU(power transmitting unit)를 구동하여 가변 자속을 발생시킨다. 마찬가지로 튜닝된 회로에서 코일로 구성된 PRU(power receiving unit)는 동일한 주파수로 튜닝되어 자기장을 교차시켜 전압을 유도한다. 전압은 자속의 변화율과 권선 수에 따라 달라진다.

수신기 코일의 출력은 정류되어 충전 중인 휴대용 기기에 바람직한 레벨로 변환된다. 결합은 결합 계수 k로 정의되는 두 코일 간의 분리에 따라 달라진다. 0.5 미만의 k는 자기 공진 결합과 같은 느슨하게 결합된 시스템을 나타낸다. 그림 1은 PTU 및 PRU의 시스템 블록을 보여준다. 블루투스 통신을 지원하는 마이크로컨트롤러는 충전 중인 기기의 요구에 따라 전송되는 전력의 양을 요청하고 레귤레이트하는 데 사용된다.

Class-D 전력 증폭기에 GaN을 사용하는 이점

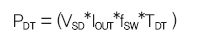

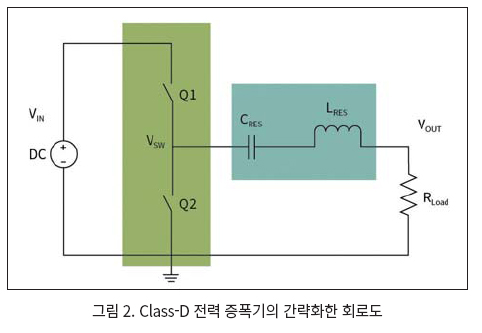

그림 2는 DC 입력을 AC 출력으로 변환하는 인버터와 매우 유사한 Class-D 증폭기의 간략화한 회로도를 보여준다.

Class-D 기능을 이해하려면 회로도를 다음 두 개의 주요 블록으로 나누어 보는 것이 유용하다.

1. 스위치: V

IN 진폭으로 사각형의 주기적 파형을 생성한다.

2. 필터: LC 필터는 정현파 파형을 생성하고, 수신되는 사각 파형과 동일한 주파수에서 가능한 많은 고조파를 제거한다. LC 공진기에 의해 수행되는 추가적인 동작은 DC 전압을 차단하므로, 부하에 걸쳐 약 제로 레벨에서 AC 신호만 존재한다.

이러한 간단한 이해를 통해 필터의 첫 번째 고조파에 의해 제공되는 정현 전류를 고려하여 부하에 걸친 전압을 쉽게 계산할 수 있다. 공진 주파수에서 LC 임피던스는 영(0)이다.

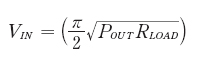

첫 번째 고조파를 고려하면 부하에서 출력 전압(피크-투-피크)은 다음과 같이 구할 수 있다. 따라서 출력 전력은 다음과 같이 나타낼 수 있다.

무선 충전 송신기의 설계 단계에서 일반적으로 송신 코일의 출력 전력은 입력의 하나이며(P

OUT로 표시), 반면에 입력 전압은 설계 파라미터의 하나이다.

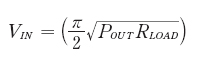

위의 두 번째 식에서, 출력 전력을 알면, 해당 전력에 도달하는 데 필요한 입력 전압을 결정하는 방법을 얻을 수 있다(100% 효율 가정).

Class-D 토폴로지는 ZVS 턴온 시 정류 동작을 수행하는데 6.78MHz 동작 주파수로 정류 손실이 매우 높아 효율이 낮을 수 있다. 또한 입력 전압에 따라 다르지만, 일반적으로 송신 안테나가 고전류 동작(송신 안테나의 일반적인 전류는 1-2A 범위)을 수행할 수 없기 때문에 상당한 전력을 송신할 수 있도록 하려면 비교적 높은 입력 전압(50-100V)을 사용해야 한다.

따라서 높은 전압과 높은 스위칭 주파수의 결합은 ZVS 동작을 필요로 한다. ZVS 동작을 구현하는 가장 일반적인 방법의 하나는 추가적인 직렬 LC 네트워크를 사용하여 부하 전류보다 높은 삼각형 모양의 전류를 생성하는 것이다.

.jpg)

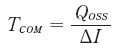

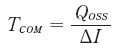

ZVS 동작을 보장하기 위해서는 이러한 방식으로 생성되는 전류는 데드 타임이 만료되기 전에 하프 브리지(그림 3의 VSW)의 중간 지점에서 전환을 보장해야 한다. 이에 따라 Class-D 토폴로지에 다음과 같은 설계 규칙이 적용된다.

Q

OSS는 입력 전압에서 평가된 스위치의 출력 전하이며, ΔI는 ZVS 네트워크에 의해 생성된 리플 전류이다(LZVS + CZVS). 이 식은 스위치의 출력 전하가 낮을수록 ZVS 리플 전류가 낮다는 것을 보여주며, 달리 말하면 리플 전류가 고정된 경우 Q

OSS가 낮을수록 더 쉽게 ZVS 전환을 보장할 수 있다.

ZVS 네트워크와 관련된 전력 손실은 지배적인 손실이다. 이는 다음과 같이 계산할 수 있다.

.jpg)

여기서 I

ZVS_RMS는 ZVS 네트워크를 통과하는 R

MS 전류이고, ESR

ZVS는 ZVS 네트워크의 기생 등가 저항으로, 주로 ZVS 인덕터에 집중된다.

ZVS 동작은 저항을 나타내는 부하에 따라 달라지기 때문에 적합한 임피던스 정합 네트워크를 포함시켜야 한다. 시스템은 임피던스 박스로 알려진 코너 임피던스 값의 정의된 세트 내에서 ZVS 동작을 유지한다. ZVS 동작이 아닌 경우 손실을 낮추려면 낮은 Q

GD를 갖는 스위치를 사용하는 것이 바람직하다.

그렇다면, GaN이 Class-D 에 어떤 이점을 제공할 수 있을까? 시스템 레벨에서 가장 큰 손실 요인은 ZVS 인덕터의 DC 저항과 ZVS 경로에 삽입되는 다른 저항으로 이는 50% 이상을 차지한다. ZVS 인덕터를 선택하면, 이 손실은 리플 전류와 Q

OSS 디바이스 파라미터와 관련된다. 따라서 Q

OSS를 낮추면 손실이 크게 향상된다. 나머지 손실은 토폴로지가 50% 듀티 사이클로 동작하므로 상부 및 하부 스위치 간에 균등하게 분배된다.

디바이스 레벨에서 가장 높은 요인은 게이트 차지(Q

G)에 있으므로 낮은 게이트 차지를 갖는 디바이스가 필수적이지만, 낮은 임계값 전압도 바람직하다. 이렇게 하면 구동 전압을 낮출 수 있어 구동 손실을 추가로 줄일 수 있다.

위의 시뮬레이션은 순수한 저항성 부하로 실행되었지만, ZVS가 모든 동작 조건에서 보장되지 않는다는 것을 고려하여 스위칭 손실도 고려한다. 이 경우 과도한 손실을 피하려면 낮은 Q

GD가 바람직하다.

손실과 관련하여 GaN은 또한 실리콘 솔루션에 비해 이점을 갖는다. ZVS 네트워크를 이용한 완전한 Class-D 토폴로지를 시뮬레이트하여 디바이스 모델에 따른 성능을 검사하고 실리콘을 대체하여 GaN 기술을 사용할 경우 예상되는 향상을 확인할 수 있다.

그림 4에서 볼 수 있듯이 실리콘과 GaN 간의 전력 손실 감소는 30% 범위에 있다. 시뮬레이션은 동일한 데드 타임으로 실행됐지만, 데드 타임을 최적화할 경우 GaN의 손실을 더욱 낮출 수 있다. 또한 디바이스 공간은 GaN 솔루션에서 절반으로, 이는 두 배 이상 전력 밀도가 증가한다는 것을 의미한다.

무선 전력 애플리케이션에서 GaN의 장점 요약

무선 전력 전송에서, 위에서 언급한 Class-D 토폴로지에 적용할 경우, GaN 디바이스의 장점은 다음과 같이 요약할 수 있다.

• 더 낮은 게이트 차지 손실

표준 실리콘 MOSFET이 통상 약 10V로 구동되는 것과 달리, GaN 디바이스는 주로 5V 게이트 드라이브 전압으로 구동된다. GaN 디바이스의 게이트 차지(Q

G)는 MOSFET 또는 유사한 R

DS(on) 및 V

BRR의 약 1/5에 불과해 게이트 드라이버 IC에서 게이트 드라이브 전류를 획기적으로 낮추고 손실을 크게 줄여준다.

게이트 차지 손실을 최소화하려면 낮은 Q

G를 선택할 뿐 아니라 낮은 게이트 임계값 전압을 갖는 디바이스 기술을 사용하여 설계자가 더 낮은 구동 전압을 사용하는 것이 바람직하다. 이렇게 하면 구동 회로와 관련된 전체 손실을 감소시킬 수 있다.

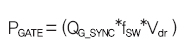

게이트 차지 손실은 다음과 같이 계산할 수 있다:

여기서 Q

G_SYNC는 (ZVS 전환을 가정하므로) QGD 없이 전압 V

dr에서의 게이트 차지이고, f

SW는 스위칭 주파수, V

dr는 구동 전압을 나타낸다.

•바디 다이오드 손실

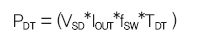

GaN HEMT 디바이스는 MOSFET과 같이 실제 바디 다이오드를 갖지는 않지만, 다이오드와 같은 특성을 보여준다. 시스템 손실의 또 다른 중요한 요인은 바디 다이오드 순방향 전압이다. 실제로 이 전압은 GaN 디바이스에서 더 높다. 턴온 시 ZVS 정류로 인해 손실이 발생하며, 긴 데드 타임을 선택하는 경우 손실이 비교적 높을 수 있다. Class-D 회로에서 GaN으로 최고의 성능을 얻으려면 바디 다이오드 전도를 피할 수 있도록 데드 타임을 낮춰야 한다.

바디 다이오드 손실 평가에서 정확한 VSD 값을 계산하는 것이 중요하다. 이 값은 전류와 온도에 따라 달라진다.

•역 복구

손실의 또 다른 요인은-이는 정량화하기 어려운데-데드 타임 동안 바디 다이오드 전도와 관련된 역 복구 전하(Q

RR)이다. GaN 디바이스는 자체적인 구조에 실제 바디 다이오드 구조를 포함하고 있지 않으므로 Q

RR가 영이다. 이들 손실을 정량화하기 어려운 이유는 주로 Q

RR가 다이오드의 순방향 전류, di/dt, 역 전압 및 온도 등의 동작 조건에 크게 의존한다는 사실과 관련된다.

디바이스 데이터시트에 제공되는 값은 특정 테스트 조건 하에서 측정된 값으로 설계자를 위한 참조용이며 실제 애플리케이션에서는 거의 관련이 없을 수 있다. 그럼에도 자기 공진 전력 전송에 사용되는 비교적 높은 스위칭 주파수에서는 더 낮은 QRR가 더 낮은 전력 손실을 생성한다는 것은 분명하다. 유일한 질문은 동작 전류와 그에 따른 동작 Q

RR가 이러한 애플리케이션에서는 높지 않기 때문에 손실의 상대적 중요성과 관련된다.

GaN 사용 시 무선 충전 설계 고려사항

이전 단락에서 GaN 기술이 시스템의 전체 효율을 증가시키는 많은 기회를 제공하는 이유를 살펴보았다. 그러나 이러한 기회는 거저 오지 않는다. GaN 기술은 시스템 설계 시 고려해야 하는 몇 가지 특성이 있다. 다음과 같은 설계 기준을 고려해야 한다.

•구동 전압 정확도

데이터시트에 지정되어 있듯이 MOSFET의 V

GS에 대한 절대 최대 정격은 통상 +/-20V이다. 이 값은 설계자에게 구동 스테이지의 전압 레귤레이터를 비교적 단순하고 저렴하게 유지할 수 있는 일부 여유를 준다.

하지만 GaN의 경우 이는 해당되지 않으며, 절대 최대 정격은 약 5~6V로 제한된다. 주된 이유는 게이트 구조의 다이오드 특성 때문이다. 동작 중에 게이트 소스 전압이 최악의 경우 이러한 제한을 초과하면, 디바이스에 심각한 손상이 초래되고 수명이 단축될 수 있다.

이러한 이유로 구동 전압을 생성하기 위해 사용하는 전압 레귤레이터의 설계는 매우 신중하게 수행되어야 한다. 실리콘에 적용되는 솔루션이 GaN에는 적합하지 않을 수 있다. 게이트 소스 전압을 절대 최대 정격 미만으로 유지하는 작업과 관련된 어려움은 구동 전압 레귤레이터 정확도뿐 아니라 데드 타임 시 동작, 그리고 Class-D 구현에서 상부 스위치를 구동하기 위한 부트스트랩 커패시터의 재충전과도 관련된다.

데드 타임 동작 중에 부트스트랩 커패시터는 하부 스위치의 바디 다이오드를 통해 재충전된다. GaN 디바이스의 경우 높은 순방향 전압을 갖는 바디 다이오드는 부트스트랩 커패시터에 여분의 전하를 제공한다. 이는 스파이크와 안정 상태 모두 디바이스의 절대 최대 정격을 초과할 수 있다. 이러한 과전하는 많은 파라미터(부트스트랩 다이오드 순방향 전압, 드레인-소스 다이오드 순방향 전압, 데드 타임, 온도)에 의존하므로 신중하게 평가해야 한다.

•게이트 전류

게이트가 게이트 산화 절연층을 통해 제어되는 실리콘 기반 제품과는 특성이 다르다. GaN 디바이스의 게이트 연결은 쇼트키 장벽의 형식을 취함으로써 누설 전류가 나노암페어(nA)가 아닌 밀리암페어(mA) 범위에 있다. 게이트 드라이브 전압과 드라이브 네트워크 구성요소를 선택할 때 신중한 주의가 필요하다.

•디바이스 공간

앞에서 언급했듯이 GaN 기술은 낮은 R

DS(on) x 공간 지수로 보다 큰 전력 밀도를 제공한다. 이는 전자 가스(2DEG)의 높은 전도성으로부터 비롯되는 특성으로, 이에 따라 애플리케이션의 전력 밀도를 증가시키기 원하는 설계자에게 매우 매력적인 특성을 제공하지만, 동시에 일부 어려움을 안겨준다. 공간이 더 작다는 것은 디바이스 내부에 소산되는 전력을 추출할 수 있는 접촉 영역이 줄어든다는 것을 의미한다.

레이아웃 단계에서 디바이스(들)와 PCB 간 전원 연결 설계는 더 까다로워질 수 있으며, 디바이스의 열 저항이 나빠질 수 있다. 가장 중요한 열 저항은 접합부에서 주변 대기로의 열 저항이기 때문에(이는 주로 PCB 특성에 의해 결정된다), GaN 디바이스 패키지의 작은 크기에서 너무 많은 추가적인 열 저항을 발생시키지 않아야 한다. 어느 경우에나 GaN의 보다 작은 공간이 이 기술의 장점을 부분적으로 상쇄할 수 있기 때문에 PCB 설계 시 이러한 열 저항을 최소화하도록 특별한 주의를 기울여야 한다.

요약

무선 전력 설계에서 에너지 효율, 더 짧은 충전 시간, 더 높은 전력 밀도는 한동안 엔지니어의 아젠다가 되어왔다. 전반적인 무선 충전 시장은 빠른 속도로 성장하고 있으며, 최종 고객의 요구를 만족시킬 뿐 아니라 넘어서기 위해 어느 때보다 더 높은 반도체 성능을 필요로 한다.

이 글에서 살펴본 애플리케이션과 측정은 Class-D RF 전력 증폭기를 사용하는 무선 충전 설계에서 GaN HEMT가 갖는 명확한 가치를 보여준다. GaN HEMT는 이러한 애플리케이션 분야에서 효율과 밀도의 경계를 모두 넓혀준다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>

.jpg)

.jpg)

.jpg)