글 | 조셉 유(Joseph Yiu), 시니어 임베디드 테크놀로지 매니저, ARM

ARM Cortex-M 제품군에는 8개의 프로세서가 있다. 본지는 ARM Cortex-M의 입문자를 위해 총 3회에 걸쳐 Cortex-M 프로세서의 기능을 비교하며 애플리케이션에 적합한 프로세서를 선택하기 위한 고려 사항과 기능 및 성능에 대해 살펴본다.

1. 개요

현재 ARM Cortex-M 프로세서에는 8개의 제품이 있다. 또한 ARM 제품 포트폴리오에는 다른 많은 ARM 프로세서들이 있다. 초보자 뿐 아니라 ARM 아키텍처에 익숙하지 않은 칩 설계자들도 약간 혼란스러울 수 있다. 프로세서마다 서로 다른 명령어 세트 지원, 시스템 기능과 성능을 제공하기 때문이다. 이 백서에서는 Cortex-M 프로세서 간의 주요 차이점과 다른 ARM 프로세서들과 어떻게 다른 것인가 대해 알아본다.

1.1 ARM 프로세서 제품군

ARM은 오랜 기간 다양한 프로세서 제품을 개발했다. ARM 프로세서 제품군은 기존 ARM 프로세서와 신규 Cortex 프로세서 제품군으로 나눠진다(그림 1 참조).

이 프로세서들은 애플리케이션 영역을 기준으로 3가지 그룹으로 분류된다.

첫째, 애플리케이션 프로세서다. 모바일 컴퓨팅, 스마트폰, 서버 등을 위한 하이엔드 프로세서들은 1 GHz이상의 고주파 클록에서 실행되며 리눅스, 안드로이드, MS 윈도우 및 모바일 운영체제와 같은 모든 기능을 필요로 하는 메모리 관리 장치(Memory Management Unit, 이하 MMU)를 지원한다. 이러한 운영체제를 요구하는 제품을 개발하기 위해선 애플리케이션 프로세서를 사용해야 한다.

둘째, 실시간 프로세서는 하드디스크 컨트롤러, 자동차 파워 트레인과 무선 통신의 기저대역 제어와 같은 실시간 애플리케이션을 지원하는 고성능 프로세서다.

대부분의 실시간 프로세서에는 MMU가 없으며, 메모리 보호 장치(MPU), 캐시(Cache) 및 산업용 애플리케이션용 메모리 기능을 탑재하고 있다. 상당히 높은 클럭 주파수(200 MHz~1 GHz)에서 작동할 수 있으며, 응답 지연 시간은 매우 낮다. 이러한 프로세서들은 리눅스나 윈도우의 풀 버전을 실행할 수는 없지만, 이러한 프로세서와 함께 사용할 수 있는 실시간 운영 체제(RTOS)는 많이 있다.

셋째, 마이크로컨트롤러 프로세서들은 대체로 훨씬 적은 실리콘 면적과 훨씬 높은 에너지 효율성을 가지도록 설계가 되어 있다. 일반적으로 더 짧은 파이프라인을 갖추고 있으며, 일반적으로 최대 주파수는 낮지만 일부 프로세서는 200 MHz 이상 지원된다. 최신 Cortex-M 프로세서 제품군은 매우 쉽게 사용할 수 있도록 설계되어 마이크로컨트롤러와 임베디드 시스템 시장에서 인기가 많다.

▲ 그림 1. ARM 프로세서 제품군

〈표 1〉은 3가지 프로세서 종류의 주요 특징을 요약한다.

▲ 표 1. 프로세서 특징 요약

|

애플리케이션 프로세서 |

실시간 프로세서 |

마이크로컨트롤러 프로세서 |

설계 |

고주파 클럭, 긴 파이프 라인, 고성능, 멀티미디어 지원 (NEON 명령어 세트 확장) |

고주파 클럭, 중간에서 긴 길이의 파이프 라인, 확정적 (저지연 인터럽트) |

보통 더 짧은 파이프라인, 초저전력, 확정적 (저지연 인터럽트) |

시스템 기능 |

메모리 관리 장치(MMU), 캐시 메모리, ARM TrustZone 보안 확장 |

메모리 보호 장치(MPU), 캐시 메모리, 밀착 결합 메모리(Tightly Coupled Memory) |

메모리 보호 장치(MPU), 중첩 벡터형 인터럽트 컨트롤러(NVIC), 웨이크업 인터럽트 컨트롤러(WIC), 최신 ARM TrustZone 보안 기능 확장 |

목표 시장 |

모바일 컴퓨팅, 스마트폰, 에너지 효율 서버, 하이엔드 마이크로프로세서 |

산업용 마이크로컨트롤러, 자동차, 하드디스크 컨트롤러, 베이스밴드 모뎀 |

마이크로컨트롤러, 심층 임베디드(Deeply embedded) 시스템 (예: 센서, MEMS, 혼합 신호 IC), 사물인터넷 (IoT) |

1.2 Cortex-M 프로세서 제품군

Cortex-M 프로세서 제품군은 성능이 크게 중요하지는 않다. 그러나 이러한 프로세서는 대부분의 마이크로컨트롤러에 사용되는 다른 일반적인 프로세서와 비교할 때 여전히 강력한 성능을 발휘한다. 예를 들어 Cortex-M4와 Cortex-M7 프로세서는 최대 400 MHz 클럭 주파수로 많은 고성능 마이크로컨트롤러 제품에서 사용되고 있다.

프로세서를 선택할 때 성능이 유일한 요인은 아니다. 많은 애플리케이션에서는 저전력과 비용적인 측면이 프로세서를 선택하는데 가장 중요한 기준이다. Cortex-M 프로세서 제품군에는 여러 가지 요구 사항을 충족시킬 수 있는 다양한 제품이 있다.

▲ 표 2. Cortex-M 프로세서 제품군

프로세서 |

설명 |

Cortex-M0 |

저비용, 초저전력 마이크로컨트롤러 및 고도의 임베디드 애플리케이션용 초소형 프로세서(12K 게이트에서 시작) |

Cortex-M0+ |

소형 임베디드 시스템을 위한 최고 수준의 에너지 효율 프로세서. Cortex-M0 프로세서와 비슷한 크기와 프로그래머 모델이지만 단일 사이클 I/O 인터페이스와 벡터 테이블 재배치등 추가 기능이 포함되어 있다. |

Cortex-M1 |

FPGA 설계에 최적화된 소형 프로세서 설계이며 FPGA의 메모리 블록을 통해 밀착 결합 메모리(Tightly Coupled Memory)를 구현한다. Cortex-M0과 동일한 명령어 세트 |

Cortex-M3 |

복잡한 작업을 보다 신속하게 처리할 수 있도록 많은 명령어가 설정된 저전력 마이크로 컨트롤러를 위한 작지만 강력한 임베디드 프로세서. 하드웨어 디바이더(Hardware Divider)와 Multiply-Accumulate(MAC) 명령어를 탑재하고 있다. 이와 함께 소프트웨어 개발자가 애플리케이션을 더 빠르게 개발할 수 있도록 포괄적인 디버그 및 추적 기능을 지원한다. |

Cortex-M4 |

이 프로세서는 Cortex-M3의 모든 기능을 제공하며, Single Instruction Multiple Data(SIMD)와 보다 빠른 단일 사이클 MAC 연산과 같은 디지털 신호 처리(Digital Signal Processing) 작업에서 추가 명령어 대상을 제공한다. 또한 IEEE 754 부동 소수점 표준을 지원하는 단정도(Single Precision) 부동 소수점 유닛 (옵션)도 제공한다. |

Cortex-M7 |

하이엔드 마이크로컨트롤러 및 프로세싱 집약적인 애플리케이션용 고성능 프로세서. Cortex-M4에서 사용할 수 있는 모든 ISA 기능과 캐시 및 밀착 결합 메모리(Tightly Coupled Memory)와 같은 추가 메모리 기능뿐만 아니라 배정도(double precision) 부동 소수점을 위한 추가 지원을 제공한다. |

Cortex-M23? |

초저전력과 저비용 설계용으로 설계된 소형 프로세서로 Cortex-M0+ 프로세서와 비슷하지만 명령어 세트 및 시스템 수준의 기능이 다양하게 향상됐다. 이와 함께 TrustZone 보안 기능 확장을 지원한다. |

Cortex-M33 |

기존 Cortex-M3및 Cortex-M4 프로세서와 비슷하지만 더욱 향상된 유연성을 갖춘 시스템 설계와 보다 나은 에너지 효율성과 성능을 제공하는 주류 프로세서 설계. 또한 이 프로세서는 TrustZone 보안 확장을 지원한다. |

기존 ARM 프로세서(예: ARM7TDMI, ARM9)와는 전혀 다른 Cortex-M 프로세서는 매우 다른 아키텍처를 가지고 있다. 예를 들면,

- ARM Thumb 명령어만을 지원하며, Thumb-2 명령어 세트(Instruction Set)라고 정의된 16비트 및 32 비트 명령어를 모두 지원하도록 확장된다.

- 인터럽트 처리는 중첩 벡터형 인터럽트 컨트롤러(NVIC)로 불리는 내장형 인터럽트 컨트롤러에 의해 관리되며, 인터럽트와 시스템 예외의 자동 우선 순위 지정, 네스팅(Nesting), 마스킹(Masking) 등을 제공한다.

- 인터럽트 핸들러는 일반적인 C 함수로 쓰여질 수 있고 벡터 인터럽트 처리 메커니즘은 어떤 인터럽트가 서비스될 지 결정하기 위한 소프트웨어를 사용할 필요가 없도록 해준다. 동시에 인터럽트 응답은 결정적(Deterministic)이며 대기 시간은 짧다.

- 벡터 테이블은 인터럽트 및 시스템 예외 처리 Rountine으로의 분기 명령어(Branch instruction)에서 인터럽트 및 시스템 예외 처리가 시작되는 주소로 변경됐다.

- 또한 레지스터 뱅크와 프로그래머 모델의 세부 사항은 변경됐다.

변경 사항은 전형적인 ARM 프로세서용으로 작성된 이전의 많은 어셈블리 코드가 수정되어야 한다는 것을 의미하며, 기존 프로젝트는 Cortex-M 으로 마이그레이션 할 때 수정하고 다시 컴파일해야 한다.

1.3 Cortex-M 프로세서의 공통 기능

Cortex-M0, M0+, M3, M4 및 M7 프로세서는 서로 유사한 점이 많다. 예를 들어,

- 기본 프로그래머의 모델(섹션 3.1)

- 인터럽트 관리를 위한 중첩 벡터형 인터럽트 컨트롤러(NVIC)

- 아키텍처의 정의된 슬립 모드: 슬립과 심층 슬립(Deep sleep)(섹션 4.1)

- OS 지원 기능(섹션 3.3)

- 디버그 지원(섹션 6)

- 쉬운 사용

예를 들어 NVIC은 통합 인터럽트 컨트롤러다.

▲ 그림 2. Cortex-M 프로세서 안의 NVIC

NVIC은 주변 장치들로부터 다수의 인터럽트 입력, 마스크 불가능 인터럽트 요청, SysTick(3.3 참조)이라고 불리는 내장 시스템 타이머 및 다수의 시스템 예외로부터 인터럽트 요청을 지원한다. NVIC은 이러한 인터럽트와 예외의 우선 순위 관리 및 마스킹을 처리한다.

NVIC 및 예외 모델에 대한 보다 자세한 내용은 섹션 3.2에서 다룬다. 다른 영역에서의 유사점과 차이점은 본 문서의 나머지 부분에서 다루기로 한다.

2. Cortex-M 프로세서의 명령어 세트

2.1 명령어 세트 개요

대부분의 경우 애플리케이션 코드는 C 또는 다른 고급 언어로 작성이 된다. 그러나 Cortex-M 프로세서의 명령어 세트 지원에 대한 기본적인 이해는 어떤 Cortex-M 프로세서가 작업에 필요한지를 결정하는데 도움을 준다. 명령어 세트 아키텍처(ISA: Instruction Set Architecture)는 프로세서 아키텍처의 일부분이며 Cortex-M 프로세서는 여러 아키텍처 프로파일로 그룹화할 수 있다.

▲ 표 3. ARM Cortex-M 프로세서용 아키텍처 프로파일

아키텍처 |

설명 |

ARMv6-M |

Cortex-M0, Cortex-M0+ 및 Cortex-M1 프로세서용. |

ARMv7-M |

Cortex-M3, Cortex-M4 및 Cortex-M7 프로세서용. DSP 유형의 명령어 (예: SIMD)를 지원하기 위한 ARMv7-M의 확장은 ARMv7E-M으로 명명된다. |

ARMv8-M |

이 아키텍처 릴리스는 다음과 같이 나뉘어진다. |

모든 Cortex-M 프로세서는 Thumb이라고 불리는 명령어 세트를 지원한다. Thumb-2 기술이 사용 가능하고 확장되었을 때 완벽한 Thumb 명령어 세트는 상당히 커졌다. 그러나 각각의 Cortex-M 프로세서는 〈그림 3〉에서와 같이 Thumb ISA에서 사용할 수 있는 명령어의 다른 서브세트를 지원한다.

▲ 그림 3. Cortex-M 프로세서의 명령어 세트 지원

2.2 Cortex-M0/M0+/M1 명령어 지원

Cortex-M0/M0+/M1 프로세서는 ARMv6-M 아키텍처를 기반으로, 〈그림 3〉과 같이 작은 타원형 모양처럼 56개의 작은 명령어 세트를 가지고 있으며 이들 대부분은 16비트다. 그러나 프로세서의 레지스터와 작동중인 데이터는 여전히 32비트다. 대부분의 간단한 I/O 제어 작업과 일반 데이터 처리를 위해서는 이 작은 명령어 세트로도 충분하다. 이 작은 명령어 세트는 Cortex-M0 및 Cortex-M0+ 프로세서의 12K 게이트에서 시작해 매우 작은 게이트 카운트로 프로세서 설계를 구현할 수 있도록 해준다.

그러나 이러한 명령어 중 많은 명령어는 높은 레지스터(High Registers, R8~R12)를 사용할 수 없으며, 이 미디어트 데이터(Immediate Date)를 생성하는데 기능의 제한을 가지고 있다. 이는 초저전력 프로세서 설계의 요구 사항과 사용 가능한 성능 사이의 타협점이다.

2.3 Cortex-M3의 명령어 지원

Cortex-M3 프로세서는 ARMv7-M 아키텍처를 기반으로 하면서, 높은 레지스터를 효율적으로 활용할 수 있는 많은 32비트 명령어를 포함하는 훨씬 많은 명령어 세트를 지원한다. 또한 이것은 아래 사항을 지원하고 있다.

- IT 명령어를 사용해 테이블 분기 명령어 및 조건부 실행

- 하드웨어 디바이드 명령어

- 승법 연산(MAC: Multiply-Accumulate) 및 다양한 비트 필드 연산

많은 명령어는 다양한 방법으로 성능을 향상시켰다.

예를 들어, 32 비트 Thumb 명령어는 더 넓은 범위의 이미디어트 데이터 값, 분기 오프셋 및 데이터 메모리접근에 대한 이미디어트 오프셋(Immediate Offset)을 제공한다. 또한 DSP 연산에 대한 기본적인 지원을 한다(예: 다수의 클락 사이클을 취하는 소수의 MAC 명령어와 포화 조정(Saturation Adjustment) 명령어도 사용이 가능). 마지막으로 32비트 명령어는 단일 명령어에서 많은 데이터 연산과 함께 배럴 쉬프터를 사용할 수 있도록 해준다.

조금 더 많은 명령어 세트는 더 큰 실리콘 면적과 더 높은 전력을 발생하게 한다. 일반적인 마이크로컨트롤러에서 Cortex-M3의 게이트 수는 Cortex-M0 또는 Cortex-M0+ 설계의 두 배 이상이 될 수 있다. 그러나 프로세서의 실리콘 면적이 대부분의 최신 마이크로컨트롤러에서 작은 부분임을 감안하면 Cortex-M3의 더 큰 실리콘 면적과 전력이 심각한 수준의 영향을 미치진 않는다.

2.4 Cortex-M4의 명령어 지원

Cortex-M4 프로세서는 Cortex-M3과 여러 가지 면에서 매우 비슷하다(파이프라인, 프로그래머 모델). 또한 Cortex-M3의 모든 기능을 지원하며 SIMD, 포화 산술연산 명령어, 단일 사이클에서 실행할 수 있는 다양한 MAC 명령어와 (Cortext-M3에서는 여러 사이클이 걸리고 및 제한된 종류의 연산만 제공된다) 같이 DSP애플리케이션을 위한 다양한 명령어 타깃을 추가로 지원한다. 단정도(Single Precision)부동 소수점 연산을 지원하는 부동 소수점 처리 장치(옵션)를 제공한다.

Cortex-M4의 SIMD 연산은 2개의 16비트 데이터 또는 4개의 8비트 데이터를 병렬로 처리한다. 예를 들어, 〈그림 4〉는 QADD8 및 QADD16 연산을 보여준다.

▲ 그림 4. SIMD 명령어 예: QADD8 및 QADD16

계산을 병렬로 처리할 수 있는 것처럼 SIMD의 사용은 특정 DSP 연산에서 16비트 및 8비트 데이터를 훨씬 빠르게 계산할 수 있도록 해준다. 그러나 일반적인 프로그래밍에서 C 컴파일러는 SIMD 기능을 사용하지 않는다. 이것이 바로 Cortex-M3와 Cortex-M4의 일반적인 벤치마크 결과가 유사한 이유다. 그러나 Cortex-M4의 내부 데이터 경로는 Cortex-M3과는 다르고, 몇 가지 경우(예: 단일주기 MAC 지원 및 단일 클록 주기에 두 레지스터에 Write Back 가능)에서는 더 빠른 연산 작업이 가능하다.

2.5 Cortex-M7의 명령어 지원

Cortex-M7 프로세서의 명령어 세트지원은 Cortex-M4와 비슷하며, 아래와 같은 기능이 추가됐다.

- (Cortex-M4에서) 부동 소수점 아키텍처는 FPv4보다 FPv5를 기반으로 하며, 몇 가지 추가적인 부동소수점 명령어를 가지고 있다.

- 배정도(Double Precision) 부동 소수점 명령어(옵션)

- 사전에 데이터 캐싱을 위한 사전로드 데이터(Preload Data: PLD) 명령어 지원

Cortex-M7는 Cortex-M4와 매우 다른 파이프라인을 가지고 있다. 그것은 높은 성능을 가능하게 하는 6 단계 이중 이슈 파이프라인을 가지고 있다.

Cortex-M4를 위해 작성된 대부분의 소프트웨어는 Cortex-M7에서 재사용할 수 있는 반면, 소프트웨어는 파이프라인의 특성 차이로 인해 최고의 최적화를 위해 재컴파일을 해야 하며 대부분의 경우 캐시와 같은 새로운 기능을 이용할 수 있는 마이너 업데이트가 요구된다.

2.6 Cortex-M23의 명령어 지원

Cortex-M23 프로세서의 명령어 세트는 ARMv6-M의 상위 집합인 ARMv8-M Baseline의 서브 프로파일을 기반으로 한다. 추가 명령어는 다음과 같다.

- 하드웨어 디바이드 명령어

- 비교, 분기 및 32 비트 분기 명령어

- TrustZone 보안 확장을 위한 명령어

- 배타적 접근(Exclusive access) 명령어(보통 세마포어 연산에 사용됨)

- 즉각적인 16비트 데이터 생성 명령어

- C11 지원을 위한 Load-Acquire(LDAR) 및 Store-Release(STLR) 명령어

어떤 경우에는 이러한 명령어 세트 향상이 더 좋은 성능으로 나타날 수 있다. 그리고 또한 다중 프로세서를 포함하는 SoC 설계에도 유용하다(예: 배타적 접근은 다중 프로세서 전반에 걸쳐 세마포어에 유용함).

2.7 Cortex-M33의 명령어 지원

Cortex-M33 설계는 구성에 대한 다양한 설정이 가능하며(Configurable), 일부 명령어는 옵션이다. 예를들어,

- (Cortex-M4 및 Cortex-M7 프로세서에서 지원되는) DSP 명령어는 옵션이다.

- 단정도(Single Precision) 부동 소수점 지원은 옵션이며, Cortex-M4 부동 소수점 연산과 비교시 몇 가지 추가된 명령어를 가진 FPv5를 기반으로 한다.

또한 Cortex-M33은 아래 내용을 포함해 ARMv8-M Mainline 서브 프로파일을 위해 도입된 새로운 명령어를 지원한다.

- TrustZone 보안 확장을 위한 명령어

- C11 지원을 위한 Load-Acquire(LDAR) 및 Store-Release(STLR) 명령어

2.8 ISA 기능 비교 요약

아키텍처에는 많은 ISA 기능이 있어 모든 기능을 자세히 다루기는 어렵다. 그러나 〈표 4〉는 주요 차이점을 요약한 것이다.

▲ 표 4. ISA의 기능 비교

|

Cortex-M0/M0+ |

Cortex-M1 |

Cortex-M3 |

Cortex-M4 |

Cortex-M7 |

Cortex-M23 |

Cortex-M33 |

아키텍처 |

ARMv6-M |

ARMv6-M |

ARMv7-M |

ARMv7E-M |

ARMv7E-M |

ARMv8-M Baseline |

ARMv8-M Mainline |

v4T,v5T, v6-M Thumb ISA |

Y |

Y |

Y |

Y |

Y |

Y |

Y |

v7-M Thumb ISA |

- |

- |

Y |

Y |

Y |

- |

Y |

저전력/슬립 모드: WFE, WFI, SEV |

Y |

NOP로 실행 |

Y |

Y |

Y |

Y |

Y |

Single cycle Multiply(32 비트 결과) |

Y |

Y |

Y |

Y |

Y |

Y |

Y |

비트 필드 프로세싱 |

- |

- |

Y |

Y |

Y |

- |

Y |

하드웨어 디바이드(integer) |

- |

- |

Y |

Y |

Y |

Y |

Y |

비정렬 데이터 접근 |

- |

- |

Y |

Y |

Y |

- |

Y |

테이블 분기 |

- |

- |

Y |

Y |

Y |

- |

Y |

조건부 실행(IT) |

- |

- |

Y |

Y |

Y |

- |

Y |

비교 & 분기(CBZ, CBNZ) |

- |

- |

Y |

Y |

Y |

Y |

Y |

부동 소수점 |

- |

- |

- |

단정도(옵션) |

단정도/ 단 + 배정도 (옵션) |

- |

단정도(옵션) |

MAC |

- | - |

Y(다중 주기, 제한적) |

Y(단일 주기) |

Y(단일 주기) |

- |

Y(단일 주기) |

SIMD |

- |

- |

- |

Y |

Y |

- |

Y |

포화 |

- |

- |

USAT, SSAT만 해당 |

Y |

Y |

- |

Y |

배타적 접근 |

- |

- |

Y |

Y |

Y |

Y |

Y |

Load acquire, store release |

- |

- |

- |

- |

- |

Y |

Y |

메모리 장벽 |

Y |

Y |

Y |

Y |

Y |

Y |

Y |

SVC |

Y |

옵션 |

Y |

Y |

Y |

Y |

Y |

| TrustZone 지원 | - | - | - | - | - | - | - |

Cortex-M 프로세서에서 ISA의 핵심 특징 중 하나는 상위 호환성이다. Cortex-M3 프로세서에서 지원되는 명령어는 Cortex-M0/M0+/M1의 상위 집합이다. 이론적으로 메모리 맵이 같다면 Cortex-M0/M0+/M1의 이진 이미지를 Cortex-M3에서 직접 실행할 수 있다.

이는 Cortex-M4/M7과 다른 Cortex-M 프로세서 간의 관계에도 동일하게 적용된다. Cortex-M0/M0+/M1/M3에서 사용 가능한 명령어는 Cortex-M4/M7에서도 실행될 수 있다.

Cortex-M0/M0+/M1/M3/M23 프로세서에는 부동소수점 처리 장치 옵션이 없지만 소프트웨어를 사용하여 부동 소수점 계산을 수행할 수는 있다. 이는 부동소수점 처리 장치가 없는 Cortex-M4/M7/M33 기반의 제품에도 적용이 된다. 이러한 경우, 부동 소수점 데이터가 프로그램에서 사용될 때 컴파일러는 링크 단계에서 필요한 런타임 라이브러리 함수를 삽입하게 된다.

소프트웨어를 사용한 부동 소수점 계산은 시간이 오래걸리며 이때 코드 크기는 약간 커질 수 있다. 그러나 부동 소수점 계산이 빈번하지 않는다면 애플리케이션에 적합할 수 있다.

3. 아키텍처 특징

3.1 프로그래머 모델

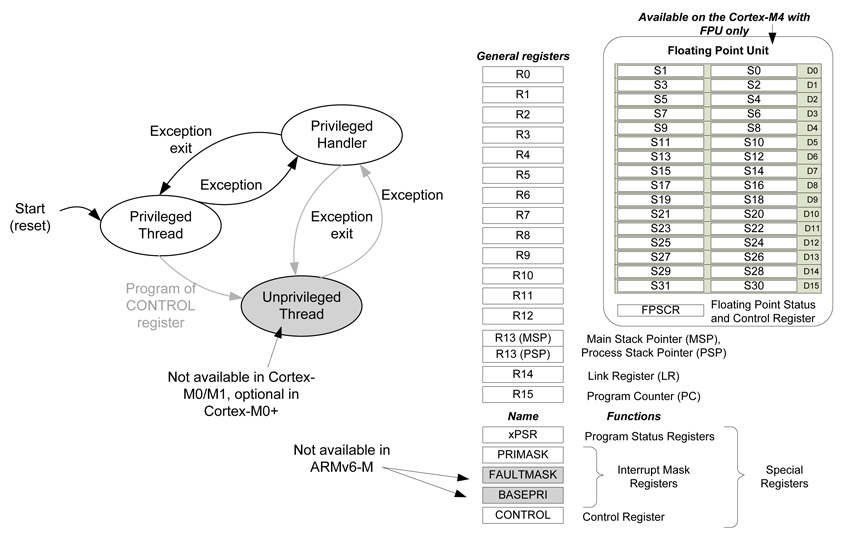

Cortex-M 프로세서 제품군의 프로그래머 모델은 매우 일관성이 있다. 예를 들어 R0~R15, PSR, CONTROL 및 PRIMASK는 모든 Cortex-M 프로세서에서 사용이 가능하다. 2개의 특수한 레지스터(FAULTMASK와 BASE PRI)는 Cortex-M3, Cortex-M4, Cortex-M7 및 Cortex-M33에서만 사용이 가능하며, 부동 소수점 레지스터 뱅크와 FPSCR(부동 소수점 상태 및 제어 레지스터)은 옵션인 부동 소수점 처리 장치가 있는 Cortex-M4/M7/M33에서만 사용이 가능하다.

▲ 그림 5. 프로그래머 모델

BASEPRI 레지스터를 통해 특정 우선 순위 레벨 또는 낮은 우선 순위의 예외 처리 및 인터럽트를 차단할 수 있다. Cortex-M3, Cortex-M4, Cortex-M7 및 Cortex-M33프로세서들에서는 많은 우선 순위 레벨을 가질 수 있으므로, 이러한 기능은 ARMv7-M 프로세서들과 ARMv8M Mainline에서 중요할 수 있다. 반면, ARMv6-M 및 ARMv8 Baseline에서는 4가지 프로그램 레벨로 제한이 된다. 일반적으로 FAULTMASK는 복잡한 오류 처리기(Fault Handler)에서 사용이 된다(3.4 섹션 참조).

권한이 없는(Unprivileged) 실행 레벨은 ARMv6-M에서 옵션이지만, ARMv7-M과 ARMv8-M에서는 항상 사용할 수 있다. Cortex-M0+에서는 옵션이며, Cortex-M0과 Cortex-M1에서는 사용할 수 없다. 이러한 차이점은 CONTROL 레지스터가 다른 Cortex-M프로세서 간에 작은 차이를 가질 수 있음을 의미한다. 또한 FPU 옵션은 〈그림 6〉에서 보는 바와 같이 CONTROL 레지스터에도 영향을 준다.

▲ 그림 6. CONTROL 레지스터

프로그래머 모델 간의 다른 차이점은 프로그램 상태 레지스터(PSR: Program Status Register)의 세부사항이다. 모든 Cortex-M 프로세서에서 PSR은 애플리케이션 PSR(APSR), 실행 PSR(EPSR) 및 인터럽트 PSR(IPSR)로 구분이 된다.

APSR의Q 비트와 EPSR의 ICI/IT 비트는 ARMv6-M과 ARMv8-M Baseline 에서는 사용할 수 없으며, GE 비트는 ARMv7E-M(예:Cortex-M4, Cortex-M7)과 ARMv8-M Mainline(예:DSP 기능 확장이 구현됐을 때의 Cortex-M33)에서 사용이 가능하다. 또한 IPSR에서 인터럽트 번호의 넓이는 ARMv6-M에서 더 작은 범위를 가지게 된다. 이것은 〈그림 7〉에 표시되어 있다.

▲ 그림 7. PSR 차이점

Cortex-M의 프로그래머 모델은 ARM7TDMI와 같은 기존의 ARM 프로세서와는 다르다. 레지스터 뱅크 이외에 기존 ARM 프로세서의 '모드' 및 '상태'에 대한 정의는 Cortex-M에서 또한 다르다. Cortex-M에는 쓰레드(Thread)와 처리기(Handler)의 2가지 모드만 있으며, Cortex-M 프로세서는 Thumb 상태에서 항상 작동한다(ARM 명령어는 지원되지 않음).

3.2 예외 처리 모델과 NVIC

모든 Cortex-M 프로세서에는 중첩 백터형 인터럽트 컨트롤러(NVIC)가 포함되어 있으며 동일한 예외 처리 모델을 공유한다. 예외 처리가 발생하며 현재 레벨보다 우선 순위가 높고, 마스킹 레지스터에 의해 차단되지 않을 때 프로세서는 인터럽트/예외 처리를 허용하고, 현재 스택(Stack)에 다수의 레지스터를 스택한다. 이 스택 메커니즘은 인터럽트 처리기(Interrupt Handler)를 일반 C 함수로 쓸 수 있게 하며, 또한 스태킹 기능이 필요하지 않기 때문에 많고 작은 인터럽트기능을 통해 실제 작업을 바로 시작할 수 있다.

ARMv7-M/ARMv8-M Mainline에서 사용 가능한 일부 인터럽트 및 시스템 예외 처리는 ARMv6-M/ARMv8-M Baseline에서는 사용할 수 없다(그림 8 참조). 예를 들어 Cortex-M0, M0+ 및 M1에서는 인터럽트 수가 32까지 제한적이고, 디버그 모니터 예외 처리는 없으며 오류 예외 처리는 HardFault로 제한이 된다(오류 처리에 대한 세부 정보는 3.4 섹션을 참조).

반면 Cortex-M23, Cortex-M3, Cortex-M4 및 Cortex-M7 프로세서는 최대 240개의 주변 장치 인터럽트를 지원한다. Cortex-M33 프로세서는 최대 480개의 인터럽트를 지원한다. 또 다른 차이점은 사용 가능한 우선 순위 레벨의 수다.

- ARMv6-M 아키텍처 - ARMv6-M 아키텍처에서 인터럽트/예외 처리의 우선 순위 레벨에는 (NMI 및 HardFault를 위한) 2개의 고정된 레벨과 4개의 프로그래밍 가능한 레벨(우선 순위 레벨 레지스터 당 2비트)이 포함되어 있다. 이것은 대부분의 마이크로컨트롤러 애플리케이션에 충분하다.

- ARMv7-M아키텍처 - 8레벨(3비트)에서 256레벨(8비트) 범위까지 프로그래밍이 가능한 우선 순위.

실제로 대부분의 디바이스는 실리콘 면적 때문에 단지 8레벨(3비트)에서 16레벨(4비트)까지만 구현한다. 또한 ARMv7-M에는 우선 순위 그룹화라는 기능이 있기 때문에 이 기능을 통해 우선 순위 레벨 레지스터를 그룹 우선 순위와 하위 우선 순위로 세분할 수 있을 뿐만 아니라 선점(Preemption) 동작을 자세하게 정의할 수도 있다.

- ARMv8-M Baseline - ARMv6-M과 유사하게, ARMv8-M Baseline도 역시 2비트 우선 순위 레벨 레지스터를 가지고 있다. 옵션인 TrustZone 보안기능 확장으로, 보안 소프트웨어는 비보안 인터럽트의 우선 순위 레벨을 우선 순위 레벨 공간의 하반부로 이동할 수 있으며, 이를 통해 보안 예외 처리/인터럽트 중 일부는 비보안 인터럽트보다 항상 높은 순위를 가지는 것이 가능하다.

- ARMv8-M Mainline-8에서 256 인터럽트 우선 순위 레벨과 우선 순위 그룹화 기능을 가질 수 있는 ARMv7-M과 비슷하다. 또한 ARMv8-M Baseline에서와 같이 우선 순위 레벨 이동을 지원한다.

▲ 그림 8. Cortex-M 프로세서의 예외 유형

모든 Cortex-M 프로세서는 예외 처리 중 벡터 테이블에 의존하게 된다. 벡터 테이블은 〈그림 8〉에서 보는 것과 같이 예외 처리기의 시작 주소를 저장한다. 벡터 테이블의 시작 주소는 벡터 테이블 오프셋 레지스터(VTOR)라고 불리는 레지스터에 의해 정의된다.

- Cortex-M0+, Cortex-M3 및 Cortex-M4 프로세서: 기본적으로 벡터 테이블은 메모리 맵(주소 0x0)의 시작 부분에 위치하고 있다.

- Cortex-M7, Cortex-M23 및 Cortex-M33 프로세서: VTOR의 기본값은 칩 설계자에 의해 정의된다.

Cortex-M23 및 Cortex-M33 프로세서는 보안 및 비보안 예외처리/인터럽트에 대해 2개의 분리된 벡터 테이블을 가질 수 있다.

- Cortex-M0 및 Cortex-M1은 프로그래밍이 가능한 VTOR을 구현하지 않으며 벡터 테이블의 시작 주소는 항상 0x00000000이다.

VTOR은 Cortex-M0+ 및 Cortex-M23 프로세서에서 옵션이다. VTOR이 구현되면 VTOR를 프로그래밍하여 벡터 테이블 시작 주소를 변경할 수 있다. 이것은 다음과 같은 경우에 유용한 기능이다.

- 동적으로 변하는 예외 처리기의 진입점을 허용하기 위해 벡터 테이블을 SRAM으로 재배치

- 좀 더 빠른 벡터 인출(Vector Fetch)을 위해 벡터 테이블을 SRAM으로 재배치(플래시 메모리가 느린 경우)

- 벡터 테이블을 ROM(또는 플래시)의 다른 테이블로 재배치해 프로그램 실행의 다른 단계에서 다른 예외 처리기를 가질 수 있다.

NVIC 프로그래머 모델은 다른 Cortex-M 프로세서들과 몇 가지 차이점이 있다(표 5 참조).

▲ 표 5. NVIC 프로그래머 모델 및 기능의 차이점

|

Cortex-M0 |

Cortex-M0+ |

Cortex-M1 |

Cortex-M3/M4/M7 |

Cortex-M23 |

Cortex-M33 |

인터럽트의 수 |

최대 32 |

최대 32 |

최대 32 |

최대 240 |

최대 240 |

최대 480 |

NMI |

Y |

Y |

Y |

Y |

Y |

Y |

SysTick |

Y(옵션) |

Y(옵션) |

Y(옵션) |

Y |

Y(옵션) |

Y |

오류 처리기 |

1(HardFault) |

1(HardFault) |

1(HardFault) |

4 |

1(HardFault) |

4 |

VTOR |

- |

Y(옵션) |

- |

Y |

Y(옵션) |

Y |

디버깅 모니터 |

- |

- |

- |

Y |

- |

Y |

프로그래밍이 가능한 우선순위 레벨 |

4 |

4 |

4 |

8~256 |

4 |

8~256 |

소프트웨어 트리거 인터럽트 레지스터 |

- |

- |

- |

Y |

- |

Y |

인터럽트 활성화 상태 |

- |

- |

- |

Y |

Y |

Y |

레지스터 접근 |

32비트 |

32비트 |

32비트 |

8/16/32비트 |

32비트 |

8/16/32비트 |

동적 우선순위 변경 |

- |

- |

- |

Y |

Y |

Y |

대부분의 경우 NVIC의 인터럽트 제어 기능에 대한 접근은 마이크로컨트롤러 공급업체의 디바이스 드라이버 라이브러리에 포함된 CMSIS-CORE에 제공된 API에 의해 처리된다. Cortex-M3/M4/M7/M23/M33에서는 활성화된 경우에도 인터럽트의 우선 순위를 변경할 수 있다. 이와 같은 동적 우선 순위 레벨 변경은 ARMv6-M에서 지원되지 않으므로 우선 순위 레벨을 변경할 때에는 일시적으로 인터럽트를 비활성화해야 한다.

3.3 OS 지원 기능

Cortex-M 프로세서를 위한 아키텍처는 OS를 중심으로 설계됐다. OS 지원에 대한 주요 기능은 아래와 같다.

- 그림자 스택 포인터(Shadowed Stack Pointer)

- SVC 및 PendSV 예외

- SysTick 타이머 - 시간 유지와 작업 관리를 위해 정기적으로 OS 예외 처리를 생성하는 24비트 다운 카운터

- Cortex-M0+/M3/M4/M7/M23/M33의 권한없는(Unprivileged) 실행 레벨 및 메모리 보호 장치(MPU)

SVC 예외 처리는 권한이 없는 상태(Unprivileged State)에서 실행중인 애플리케이션 작업이 권한이 있는 OS서비스(Priviliged OS Service)를 트리거할 수 있도록 하기 위해 SVC 명령어에 의해 트리거된다.

PendSV 예외 처리는 컨텍스트 스위칭과 같이 중요하지 않은 연산을 예약하기 위해 OS에 유용하다.

Cortex-M1을 일부 소형 FPGA 디바이스에 적합하게 하기위해 Cortex-M1에서 이러한 모든 OS 지원 기능을 옵션으로 만들었다. Cortex-M0, Cortex-M0+ 및 Cortex-M23 프로세서에서 SysTick 타이머는 옵션이다.

일반적으로 OS 지원은 모든 Cortex-M 프로세서에서 가능하다. Cortex-M0+, Cortex-M3, Cortex-M4, Cortex-M7, Cortex-M23 및 Cortex-M33 프로세서에서의 애플리케이션 작업은 권한없는 실행 레벨에서 실행할 수 있으며 메모리 접근 위반을 방지하기 위해 MPU 옵션인 메모리 보호 장치와 함께 작동한다. 이것은 시스템의 견고성을 향상시킬 수 있다.

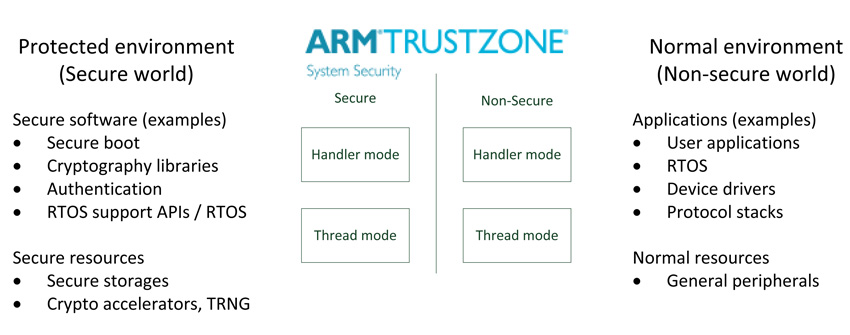

3.4 TrustZone 보안 기능 확장

지난 몇 년간 사물인터넷(IoT)은 임베디드 시스템 설계자에게 매우 뜨거운 주제였다. 사물인터넷 시스템이 더욱 정교해지고 시장 진입 압박이 증가함에 따라 임베디드 시스템은 시스템의 보안을 보장하는 더 좋은 방법이 필요한 반면, 동시에 소프트웨어 개발자가 쉽게 구

현할 수 있어야 한다.

일반적으로 소프트웨어를 권한이 있는 부분과 권한이 없는 부분으로 분리하여 권한이 있는 소프트웨어가 권한이 없는 애플리케이션으로 하여금 보안에 민감한 정보를 비롯해서 중요한 시스템 리소스에 접근하는 것을 방지할 수 있도록 메모리 보호 장치(MPU)를 활용할 수 있다.

이러한 방식은 다양한 사물인터넷 시스템에서 제대로 동작하지만 어떤 경우에는 2개의 분할만으로도 충분하지 않다. 특히 복잡한 권한 있는 소프트웨어 구성 요소가 많이 포함된 시스템의 경우 권한 있는 코드 중 하나의 취약점으로 인해 해커가 시스템을 완전히 장악할 수 있다.

ARMv8-M 아키텍처에는 TrustZone이라는 보안 기능 확장이 포함되어 있으며 이는 보안 및 비보안 상태의 직교 분할(Orthogonal Partitioning)을 추가한다.

- 비보안 상태는 일반 애플리케이션용이다.

- 보안 상태는 소프트웨어 구성 요소 및 보안 리소스용이다(예: 보안 저장 공간, 암호화 가속기, 순수난수 생성기(TRNG)).

▲ 그림 9. 보안 및 비보안 상태의 분리

비보안 소프트웨어는 비보안 메모리와 주변 장치에만 접근할 수 있으며, 보안 소프트웨어는 양쪽 모두에 있는 리소스에 접근할 수 있다.

이러한 방식으로 소프트웨어 개발자는 이전과 같이 비보안 환경에서도 자신의 애플리케이션을 개발할 수 있다. 동시에 칩 벤더가 제공하는 보안 통신 라이브러리에 의존하여 안전한 사물인터넷 연결을 수행할 수 있다.

그리고 비보안 권한 소프트웨어에 취약성이 있더라도 TrustZone 보호 메커니즘을 통해 해커가 전체 디바이스를 장악하지 못하게 함으로써 공격의 영향을 제한할 뿐만 아니라 잠재적으로 시스템을 원격으로 복구할 수 있다. 또한 ARMv8-M 아키텍처는 추가 보안 조치를 좀 더 쉽게 구현하기 위해 스택 제한 검사(Stack Limit Checking)와 향상된 MPU 설계를 도입했다.

보안 아키텍처는 시스템 레벨로 확장이 되며 각 인터럽트는 보안 또는 비보안으로 할당될 수 있다. 인터럽트/예외 처리 시퀀스는 보안 정보가 유출되지 않도록 하기 위해 레지스터에 보안 데이터를 자동으로 저장하고 복원한다. 결과적으로, TrustZone 보안 기능 확장은 시스템이 실시간으로 시스템 요구 사항을 지원하고 사물인터넷 애플리케이션에 대해 견고한 보안 기반을 제공할 수 있도록 해주며 소프트웨어 개발자가 애플리케이션을 쉽게 개발할 수 있도록 도와준다.

TrustZone은 Cortex-M23 와 Cortex-M33 프로세서에서는 옵션이다. ARMv8-M프로세서의 TrustZone에 대한 자세한 내용은 스마트 연결 시대를 위한 임베디드 프로세서의 발전 과정에 있는 다음 단계에서 찾을 수 있다.

3.5 오류 처리

ARM 프로세서와 일부 다른 마이크로컨트롤러 아키텍처의 차이점 중 하나는 오류 처리 기능이다. 오류가 감지될 때 해당 소프트웨어가 적절한 조치를 수행할 수 있도록 오류 예외 처리가 트리거된다. 오류는 다음과 같다.

- 정의되지 않은 명령어(예: 손상된 플래시 메모리)

- 잘못된 주소 공간(예: 스택 포인터 손상)에 대한 접근 또는 MPU 접근 위반

- 잘못된 연산(예: 프로세서가 SVC보다 이미 높은 인터럽트 우선 순위에 있을 때 SVC 예외 처리를 트리거하려는 시도)

오류 처리는 임베디드 시스템이 다양한 문제에 대해 훨씬 빠르게 대응할 수 있도록 도와준다. 그렇지 않으면 시스템이 멈춘 경우 워치독 타이머가 시스템을 초기화하는 데 오랜 시간이 걸릴 수 있다.

ARMv6-M 아키텍처에서 모 든 오 류 이벤트는 HardFault 처리기를 트리거하며, 우선 순위 레벨은 -1 이다(모든 프로그래밍이 가능한 예외 처리보다 높은 우선 순위지만 마스크가 불가능한 인터럽트 NMI 바로 아래임). 모든 오류는 복구 불가능한 것으로 간주되며 일반적으로 오류 보고를 수행하고 잠재적으로 HardFault 처리기 내에서 자체 초기화를 생성한다.

ARMv8-M Baseline은 단 하나의 오류 예외 처리(HardFault)를 가지고 있는 ARMv6-M과 비슷하다. 그러나 TrustZone 보안 기능 확장이 구현될 때 HardFault의 우선 순위 레벨은 -1 또는 -3이 될 수 있다.

ARMv7-M 및 ARMv8-M Mainline에는 HardFault 외에도 몇 가지 구성 가능한 오류 처리기가 있다.

- Memmanage(메모리 관리 오류)

- 버스 오류(버스는 오류 응답을 반환)

- 사용 오류(정의되지 않은 명령어 또는 다른 잘못된 연산)

- SecureFault(TrustZone 보안 기능 확장의 보안위반 처리를 위한 ARMv8-M Mainline에만 해당)

이러한 예외 처리들은 프로그래밍이 가능한 우선 순위 레벨을 가지고 있으며 개별적으로는 활성화 또는 비활성화를 할 수 있다. 또한 필요에 따라 HardFault와 동일한 레벨로 우선 순위를 높일 수 있도록 FAULTMASK 레지스터를 사용할 수 있다. 뿐만 아니라 오류 예외 처리를 트리거한 것에 대한 힌트를 제공하는 다양한 오류 상태 레지스터와 디버깅을 쉽게 하기 위해 오류를 트리거한 전송 주소를 정확히 찾는데 사용될 수 있는 오류 주소 레지스터가 있다.

ARMv7-M 과 ARMv8-M Mainline프로필의 추가 오류 처리기는 좀 더 유연한 오류 처리 기능을 제공하며 오류 상태 레지스터는 오류 이벤트를 쉽게 찾아 디버그할 수 있도록 했다. 상용 개발 제품군에 있는 여러개의 디버거에는 오류 상태 레지스터를 사용하여 오류 이벤트를 진단하는 기능이 포함되어 있다. 또한 잠재적으로 런타임 중에 오류 처리기는 일부 처리 조치를 수행할 수 있다.

▲ 표 6. 오류 처리 기능 비교의 요약

|

ARMv6-M(Cortex-M0, Cortex-M0+, Cortex-M1) 및 ARMv8-M Baseline(Cortex-M23) |

ARMv7-M(Cortex-M3, Cortex-M4, Cortex-M7) 및 ARMv8-M Mainline(Cortex-M33) |

HardFault |

Y |

Y |

MemManage |

- |

Y |

사용 오류 |

- |

Y |

버스 오류 |

- |

Y |

SecureFault |

- |

ARMv8-M Mainline 용 |

오류 상태 레지스터 |

- (디버그만을 위한 하나의 디버그 FSR) |

Y |

오류 주소 레지스터 |

- |

Y |

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>