SoC(system-on-chip) 인터커넥트 IP분야의 혁신기업인 아테리스(Arteris, 지사장 연명흠)가 SoC 설계 기술력을 향상시키는 반도체 설계 기술을 발표하면서 여러 벤더들로부터 공급되는 IP를 이용해 효율적인 캐시 코히어런트(cache-coherent) 시스템을 설계할 수 있게 됐다고 밝혔다.

아테리스의 K. 찰스 자나크(K. Charles Janac) 사장 겸 CEO는 “현재 인터커넥트 기술은 오늘날의 최첨단 SoC가 요구하는 복잡도 수준을 해결하는데 부적합하다”면서 “매우 까다로운 시스템에서 애플리케이션에 특화된 성능 목적을 효율적으로 달성시키기 위해 필수적인 성능과 설정 변경 기능을 증대시켜 시스템 개발자에게 특별히 제공하고자 새로운 아키텍처를 개발하게 됐으며, 이 기술은 다른 어느 곳에서도 이용할 수 없는 핵심적인 시스템 기능을 지원한다”고 말했다.

기자간담회에서 커트 슐러(Kurt Shuler) 아테리스 마케팅 부문 부사장은 캐시 코히어런시에 대해 “캐시는 복수의 데이터 복사본을 생성하는데, 소프트웨어로는 복사본을 관리하기가 어려운 반면, 하드웨어 캐시 코히어런시는 허상의 플랫(flat) 공유 메모리를 생성함으로써 복수의 복사본을 일관성 있게 보관할 수 있다”라고 설명했다.

이어 “최근 SoC 설계에서 등장하는 과제는 확장성(scalability), 이질혼합성(heterogeneity), 시스템 통합, 물리적 설계, 전력관리 등으로 집약되는데, 이 난제를 어떻게 해결할 것인지가 관련 기업들의 주 관심사”라고 밝혔다.

설정 변경 가능한 확장성 좋은 분산형 아키텍처

설정 변경 가능한 확장성 좋은 분산형 아키텍처

아테리스가 새롭게 발표한 ‘Ncore 캐시 코히어런트 인터커넥티드 IP 1.5’(이하 Ncore)는 업계 최초의 분산형 헤테로지니어스 캐시 코히어런트 인터커넥트를 구현해, 설계자들이 휴대용 기기, HDTV, 기업용 스토리지, 자동차 ADAS(advanced driver assistance systems), 마이크로서버 및 네트워크 시장 등 다양한 설계 영역에서 더 높은 주파수와 더 낮은 전력 소모를 실현하면서도 제조 시 출시시간을 단축시키는 차별화된 SoC를 구현하도록 했다.

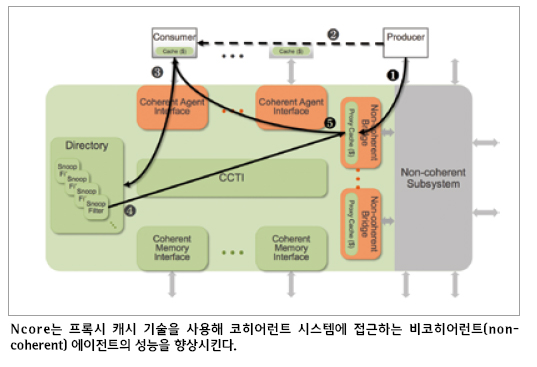

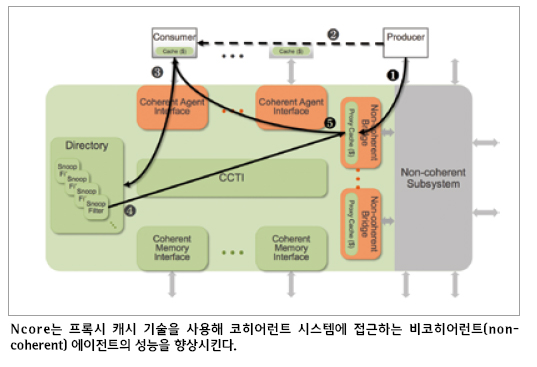

아테리스 설계 팀은 설계자가 프로토콜 불가지론(Protocol-agnostic) 방식에서 복수의 전체 코히어런트 에이전트 포트로 캐시 코히어런트 인터커넥트를 설정할 수 있는 아키텍처를 개발해, 고정 및 중앙 집중형 캐시 코히어런시 인터커넥트보다 더 우수한 설정 변경기능(configurability)을 제공한다. 또한, 아테리스 기술은 프록시 캐시 기술(‘I/O 캐시’로 명명함)을 사용해 코히어런트 시스템에 접근하는 비코히어런트(non-coherent) 에이전트의 성능을 향상시키며, 비코히어런트 IP가 시스템급 코히어런시의 장점을 달성할 수 있도록 했다.

데이비드 크뤽케마이어(David Kruckemyer) 아테리스 하드웨어 설계 부문 최고임원은 “아테리스의 Ncore는 복수의 코히어런스 모델과 다른 캐시 구성을 수용할 수 있도록 설정 가능한 복수의 스눕(snoop) 필터의 사용을 지원한다”며 “캐시 코어 에이전트들은 캐시 구성, 코히어런시 모델, 부하 측면에서 매우 다른 동작방식을 가질 수 있는데, Ncore IP는 개별 스눕 필터보다 다이 면적을 적게 차지한다”고 말했다.

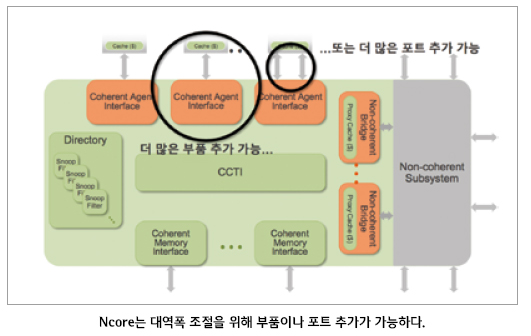

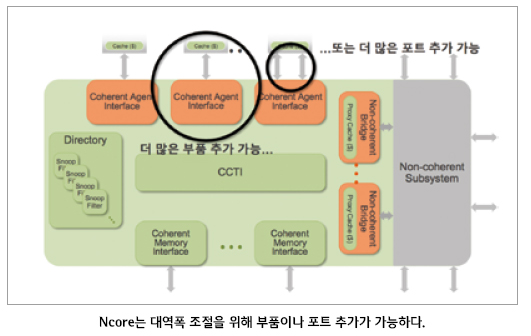

특히 설정을 변경할 수 있으며 SoC 설계자가 코히어런트 에이전트 및 메모리 인터페이스 포트, 설정 변경 가능한 스눕 필터의 개수 및 크기, 프록시 캐시의 개수 및 크기, ‘victim’ LL(last-level) 캐시를 선택할 수 있다. 분산형 하드웨어 아키텍처는 물리적 플로어 플랜(floor plan) 제약요건에 더 자연스럽게 맞추어 조정하기 때문에 물리적 구현과 타이밍 클로저(timing closure)를 수월하게 할 수 있다.

또한 서로 다른 코히어런트 프로토콜 구현, 캐시 상태 모델, 캐시 구성을 동시에 구현함으로써 헤테로지니어스 캐시 코히어런트 시스템을 지원한다. 이러한 기능들은 업계에서 사용할 수 있는 가장 뛰어난 수준의 설정 변경 기능을 설계자에게 제공해 개별 시스템의 독자적인 요건에 알맞은 SoC 주파수, 대기시간(latency), 소비전력 등을 설정할 수 있다.

한편, 데이비드 크뤽케마이어 최고임원은 “이번 Ncore IP 1.5가 적용된 시제품은 빠르면 내년 하반기에 볼 수 있으며, 자동차용 칩이 먼저 출시될 것”이라며 “1차 타깃은 자동차, 스마트폰, 태블릿 PC 등이나 최근 스마트폰에 적용된 다양한 기술들이 가전제품에 사용되는 추세가 증가하고 있어 관련 시장으로의 확장도 기대된다”고 밝혔다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>