글|*폴 블랑샤르 애플리케이션 엔지니어 **브라이언 펠레티에 제품 개발 엔지니어, 리니어 제품 기술 사업부 아나로그디바이스

.jpg)

외부 과전압 조건이 증폭기에 인가되는 경우에, ESD 다이오드는 증폭기와 전기적인 과부하 사이에 최후의 방어선이다. ESD 셀이 디바이스에 구현되는 방법의 충분한 이해와 함께 설계자는 매우 적합한 회로 설계와 더불어 증폭기의 동작 범위를 확장할 수 있다. 이 글은 ESD 구현의 다양한 유형을 소개하고 각 구현의 특징을 설명하며 설계의 강건성을 향상시키기 위해 이들 셀을 활용하는 방법에 대한 지침을 제공한다.

테스트 장비 혹은 계측 및 센싱 장비와 같은 여러 애플리케이션의 경우 입력이 시스템에서 제어되지 않고 외부 세계와 연결되어 있어서 프런트엔드 증폭기의 최대 정격 전압을 초과할 수 있다. 이러한 애플리케이션에서 설계의 유효 범위와 안정성을 보장할 수 있는 보호장치는 필수이다.

프런트엔드 증폭기의 내부 ESD 다이오드는 과전압을 차단하는 클램핑에 사용되기도 하는데, 이때 이 클램프를 사용해 장비를 충분히, 그리고 안전하게 보호하려면 여러 가지 요인이 고려되어야 한다. 프런트엔드 증폭기 내부의 다양한 ESD 다이오드 아키텍처를 주어진 보호회로가 가진 열 및 일렉트로마이그레이션(electromigration)의 영향과 함께 이해하면, 설계 시 보호 회로에 발생할 수 있는 문제점을 피하고 애플리케이션의 수명을 향상시키는 데 도움이 된다.

ESD 다이오드 구성

전원공급장치에 연결되거나 접지 연결된 ESD 다이오드가 전부 간단한 다이오드 클램프는 아니라는 점을 이해할 필요가 있다. 다이오드 여러 개의 직렬 연결이나 다이오드와 저항, 또는 백투백 다이오드 같이 다양한 구성이 사용될 수 있다. 흔히 사용되는 구성은 아래와 같다.

전원에 연결된 다이오드

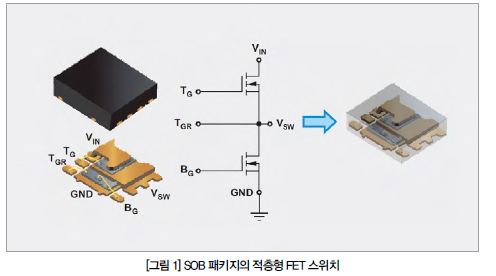

그림 1은 다이오드가 입력 핀과 전원 사이에 연결된 증폭기의 예를 보여준다. 다이오드에는 일반적인 동작 환경에서 역 바이어스(reverse bias)가 걸리지만 입력이 양의 전원 전압보다 커지거나 음의 전원 전압 아래로 떨어지면 순 바이어스(forward bias)가 걸린다. 이때 다이오드에 순방향 바이어스가 걸리기 때문에 전류는 증폭기의 입력을 통과해서 각 전원으로 흘러 들어간다.

.jpg)

그림 1의 회로는 과전압이 +Vs 이상으로 넘어설 때 본질적으로 입력 전류가 증폭기 자체에서 제한되지 않으며 직렬 저항의 형태로 외부 전류를 제한해야 한다. 전압이 -Vs 아래로 떨어지면 400 Ω의 저항으로 전류를 어느 정도까지 제한할 수 있기 때문에 설계 시 이 점 역시 고려해야 한다.

그림 2의 증폭기는 그림 1과 비슷한 다이오드 구성을 사용하지만, 이 경우 전류는 2.2 kΩ의 내부 직렬 저항에 의해 제한된다. 이렇게 구성하면 전류를 제한하는 R의 값에 따라 그림 1의 회로와 구별할 수 있을 뿐 아니라 2.2 kΩ의 저항이 +Vs보다 큰 전압으로부터 회로를 보호한다는 점에서도 그림 1과는 차이가 있다. 이는 복잡하지만 ESD 다이오드를 사용할 때 최적화된 과전압 보호를 제공하기 위해 충분히 이해해야 하는 복잡한 사항 중 하나이다.

.jpg)

.jpg)

전류 제한 JFET

그림 1과 2의 구현방식과는 대조적으로 전류 제한 JFET는 IC 설계에서 다이오드 클램프 대신 사용할 수 있다. 그림 3은 입력 전압이 장치의 특정 동작 범위를 넘어설 때 장치보호를 위해 JFET를 사용하는 경우를 보여준다. 이 장치의 경우 본질적으로 JFET를 사용해서 반대편 레일로부터 들어오는 전압을 최대 40 V까지 견딜 수 있다. JFET가 입력 핀으로 들어가는 전류를 제한하기 때문에 ESD 셀은 과전압 보호를 위해 추가로 사용할 수 없다.

최대 40 V의 전압으로부터 보호가 필요한 경우 JFET를 사용하는 이 장치의 보호 시스템은 잘 제어되고 믿을 수 있으며 명확한 보호 옵션을 제공한다. 이는 과전압 보호에 ESD 다이오드를 사용하는 것과는 보통 반대로, ESD 다이오드를 사용하면 다이오드 전류 제한에 관한 정보가 종종 특정 값으로만 명시되거나 그렇지 않으면 전혀 명시되지 않을 수 있다.

.jpg)

다이오드 스택

공급 전압이나 접지 전압보다 큰 입력 전압이 허용되는 애플리케이션에서는 다이오드 스택을 사용해 ESD 상황으로부터 입력을 보호할 수 있다. 그림 4는 스택 구조의 다이오드 보호 방식을 구현한 증폭기를 보여준다. 이 구성에서는 음의 과도 신호로부터 장치를 보호하기 위해 다이오드 스트링을 사용한다. 다이오드 스트링은 사용 가능한 입력 범위에서 누설전류를 제한하는 데 사용되기는 하지만 음의 공통 모드 범위가 초과될 때는 장치를 보호하는 데에도 사용된다. 전류 제한만이 다이오드 스트링의 직렬 저항과 동일한 역할을 한다는 데 주의하자. 주어진 전압 수준에 대한 입력 전류를 줄이는 데에는 외부 직렬 저항을 사용할 수 있다.

.jpg)

백투백 다이오드

백투백 다이오드(Back to Back Diodes)는 입력 전압 범위가 공급 전압을 초과해도 되는 경우 사용될 수 있다. 그림 5는 공급 전압이 3.3 V일 때 최대 70 V의 전압이 허용되는 장치에서 ESD 보호를 제공하는 백투백 다이오드를 설치한 증폭기를 보여준다. D4와 D5는 입력 핀에 걸리는 고전압을 격리 절연하는 데 사용되는 고전압 다이오드이며, D1과 D2는 입력 전압이 일반 동작 범위 이내에 있을 때 전류누설을 방지하는 데 사용된다. 이러한 구성에서 이러한 ESD 셀은 과전압 보호에 사용하기에 바람직하지 않다. 고전압 다이오드에 걸리는 최대 역 바이어스가 영구 손상을 일으킬 수 있는 상황을 쉽게 유발하기 때문이다.

.jpg)

ESD 클램프를 사용하지 않는 경우

장치 중에는 프런트엔드에 ESD를 포함하지 않는 것도 있다. ESD 다이오드가 없다면 설계자가 ESD 다이오드를 전압 클램프로 사용할 수 없는 것은 당연하지만, 이러한 아키텍처는 과전압 보호(overvoltage protection, OVP) 옵션을 고려할 때 살펴봐야 하는 상황 중 하나로 언급했다. 그림 6은 증폭기 보호를 위해 높은 크기의 저항만을 사용한 장치를 보여준다.

클램프의 역할을 하는 ESD 셀

ESD 셀을 설치하는 방식을 이해하는 것뿐 아니라 장치 보호를 위해 구조를 활용하는 방법을 이해하는 것도 중요하다. 일반적인 애플리케이션에서 직렬 저항은 특정 전압 범위에 대해서 전류를 제한할 때 사용된다.

.jpg)

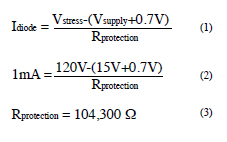

증폭기가 그림 7처럼 구성되어 있거나 전원에 연결된 다이오드가 입력을 보호한다면, 입력 전류는 다음 식 1에 따라 제한될 수 있다.

식 1에서는 Vstress > Vsupply라고 가정한다. 그렇지 않다면 0.7 V 추정치 대신 다이오드 전압을 더욱 정밀하게 측정한 뒤, 이 측정값을 계산에 사용해야 한다.

다음은 공급 전압(Vsupply)이 +/-15 V, 입력 전압(Vstress)이 최대 +/-120 V이고 입력 전류를 1 mA로 제한할 때 증폭기 보호를 위한 계산의 예를 보여준다. 식 1을 이용하면 이러한 입력 값을 이용해 다음 식 1-3을 계산할 수 있다.

이와 같이 주어진 조건에서 Rprotection > 105 kΩ이면 다이오드 전류(Idiode)는 1 mA보다 작다.

전류 제한 이해하기

Idiode의 최댓값은 부품에 따라 달라질 수 있으며 스트레스가 걸리는 특정 애플리케이션 시나리오에 따라서도 달라진다. 최대 전류는 몇 밀리초(millisecond) 동안 지속되는 일회성 이벤트일 경우와 예상 수명이 20년 이상인 애플리케이션에 전류가 지속적으로 걸리는 경우에 따라 달라질 수 있다. 특정 값에 대한 지침은 증폭기 데이터시트의 절대 최댓값 섹션이나 애플리케이션 노트에서 확인할 수 있으며, 그 범위는 보통 1 mA에서 10 mA 사이이다.

실패 모드

주어진 보호 방식에서 최대 정격 전류는 궁극적으로 다이오드에서 소비되는 전력이 가진 열 영향과 전류 경로에 대한 최대 정격 전류 두 가지 요인에 의해 제한된다. 소비 전력은 유효한 범위 내에서 동작 온도를 유지할 수 있도록 한계 값보다 낮게 유지시켜야 하며, 전류는 일렉트로마이그레이션(electromigration)으로 인한 안정성 문제를 피하기 위해 정해진 최댓값보다 낮은 값을 선택해야 한다.

열 영향(Thermal implication)

전류가 ESD 다이오드로 흘러 들어갈 때 다이오드 내에서 소비되는 전력으로 인해 온도가 증가한다. 대부분의 증폭기 데이터시트에는 전력 소비로 인해 접합 온도(junction temperature)가 어떻게 증가하는지를 보여주는 열 저항(보통 JA로 표기)이 명시되어 있다. 전력 소비로 인해 온도 증가에서 발생할 수 있는 최악의 경우 외에도 애플리케이션 온도에서 발생할 수 있는 최악의 경우를 생각해 보면 보호회로의 가능성을 가늠해볼 수 있다.

일렉트로마이그레이션

전류가 온도 문제를 야기하지 않더라도 다이오드 전류는 안정성 문제를 야기할 수 있다. 전기 신호 경로에는 일렉트로마이그레이션으로 인한 최대 수명 정격 전류가 존재한다. 다이오드 전류 경로에 대한 일렉트로마이그레이션 전류 한도는 다이오드를 직렬로 연결한 내부 경로의 두께에 의해 제한된다(typ). 이러한 정보가 증폭기마다 항상 공개되는 것은 아니지만 다이오드가 과도 신호 발생과 달리 오랜 기간 활성화되어 있다면 반드시 고려해야 한다.

일렉트로마이그레이션이 문제가 되는 경우는 증폭기가 자체의 전원 레일과, 이와 별도로 존재하는 전압 레일을 모니터링하기 위해 여기에 연결되어 있을 때이다. 여러 전원 범위가 있다면 전원 시퀀싱(power supply sequencing)으로 인해 일시적으로 절대 최대 조건을 초과하는 전압이 발생할 수 있다. 최악의 전류 경로와 이러한 전류가 활성화되어 있는 기간을 고려하고, 일렉트로마이그레이션에 허용될 수 있는 최대 전류를 이해하면 일렉트로마이그레이션으로 인한 안정성 문제를 피할 수 있다.

결론

전기 과부하가 발생했을 때 증폭기 내부의 ESD 다이오드가 활성화되는 방식을 이해하면 설계의 안정성을 쉽게 향상시킬 수 있다. 보호회로가 가진 열과 일렉트로마이그레이션의 영향을 모두 살펴보면 잠재적인 문제와 추가적인 보호가 보증되는 곳을 발견할 수 있다. 여기에서 살펴본 상황들을 고려하면 설계 시 현명한 선택을 하고, 이 분야에서 잠재적인 안정성 문제를 방지할 수 있다.

<저작권자(c)스마트앤컴퍼니. 무단전재-재배포금지>